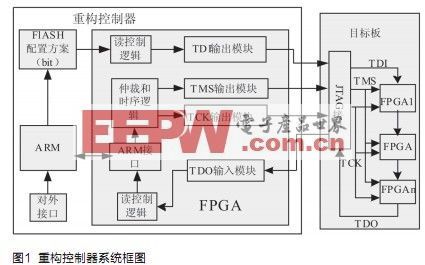

重构控制器硬件系统组成

本文介绍一种基于“ARM处理器+FPGA”架构的重构控制器,重构控制器中的FPGA能够根据ARM处理器传送来的命令,对目标可编程器件JTAG接口进行控制,并模拟JTAG接口中TAP状态机产生激励信号(TMS、TDI、TCK序列),向目标可编程器件的JTAG接口提供所需的激励,使目标可编程器件内的TAP状态机进行状态转换,将指令和数据扫描到FPGA内部边界扫描电路指令寄存器和数据寄存器中。完成一次目标可编程器件配置,实现用户此时所要求功能,在下一时段,可根据用户新的要求,调用重构控制器内部存储器中不同方案在系统重新配置目标可编程器件,实现硬件的时分复用,灵活快速的改变系统功能,节省逻辑资源,满足大规模应用需求。

其主要功能是控制按照用户不同需求调用不同的方案配置目标可编程器件。它主要包括ARM处理器、FPGA、Flash存储器,各功能部件主要功能如下:

(1) ARM处理器,其主要功能是控制模拟JTAG接口的FPGA读取Flash存储器中的重构方案,实现在系统配置;

(2) FPGA协处理器选用Xilinx公司SPARTEN3AN系列,是基于非易失性存储的FPGA,自身带有PROM,它作为外部总线和ARM控制器之间的双端口,主要功能是模拟JTAG接口实现TAP控制器时序,完成配置方案数据的并串转换并输出至外部总线;

(3)FLASH存储器容量为32M×16bit,用于处理器的上电引导、存放多种重构配置方案。由于要求的存储容量较大,采用SPANSION公司[1]S29GL512P(32M×16bit)的存储空间,访问速度110ns,可以达到25ns快速页存取和相应的90ns随机存取时间;

(4) 测试线TCK 、TMS 、TDI 和TDO,是重构控制器向目标可编程器件提供所需的JTAG TAP 激励,分别控制目标多个FPGA的重构配置和反馈重构信息。

系统实现

重构控制器

本文设计的重构控制器采用ARM微处理器作为主控制器,以FPGA芯片作为协处理器配合主控制器工作。用户事先根据需求设计出不同的配置方案,并存储在重构控制器内部的存储器中,上电后,重构控制器就可以按需求将不同设计方案分时定位到目标可编程器件内,同时保持其他部分电路功能正常,实现在系统灵活配置,提高系统工作效率。

重构控制器框图如图1所示。ARM执行的初始化工作包括程序更新加载运行,FPGA参数设定等(见图2)。FPGA初始化包括设定内部命令寄存器和逻辑状态的初始值、内部缓冲区数据清零等。ARM处理器一方面通过ARM总线读取外部Flash中的配置方案,将其存储到TDI模块的缓存中;另一方面重构控制器中模拟TAP控制器的FPGA,通过执行ARM处理器发出的配置指令,模拟产生TCK 、TMS 、TDI 和TDO信号,作为目标可编程器件的JTAG接口激励,与目标可编程器件的JTAG口串联成菊花链,对目标可编程器件进行在系统编程。

重构控制器模块

ARM接口模块

如图1所示,ARM接口模块主要作为FPGA和ARM处理器之间的接口,完成ARM的命令控制和参数传递。当系统上电后,ARM处理器将预先设定好的各种配置信息传送至ARM接口模块,完成对FPGA及各外围模块进行配置。系统正常运行时,该模块处于闲置状态。直到ARM处理器请求进行新的配置时,ARM接口模块再次传递新的配置信息,完成目标板重新配置。

仲裁与时序控制模块

仲裁与时序控制模块主要完成对重构控制器内部各模块的仲裁与时序控制。协调各模块之间的数据流向。其具体的功能包括提供内部各模块所需的时钟信号,并进行相应的时序控制;以及对内部数据流的切换控制。

TCK,TMS,TDI,TDO产生模块

TCK: JTAG配置时钟输入,所有基于JTAG的操作都必须同步于JTAG时钟信号TCK。关键时序关系是:TMS和TDI采样于TCK的上升边沿,一个新的 TDO值将于TCK下降边沿后出现,因此一般情况下JTAG的时钟不会太高。

TMS:模式选择,控制JTAG状态转移,同步时钟TCK上升沿时刻TMS的状态决定状态转移过程。

TDI :配置数据输入,配置数据在TCK的上升沿采样进入数据移位寄存器(SDR);

TDO:配置数据输出,在TCK的下降沿从移位寄存器移出,输出数据与输入到TDI的数据应不出现倒置。

目标板

目标板上被重构的FPGA由支持重构的Xilinx公司的VIRTEX-4" title="VIRTEX-4">VIRTEX-4系列FPGA来实现,以菊花链方式串联,支持JTAG边界扫描模式配置。

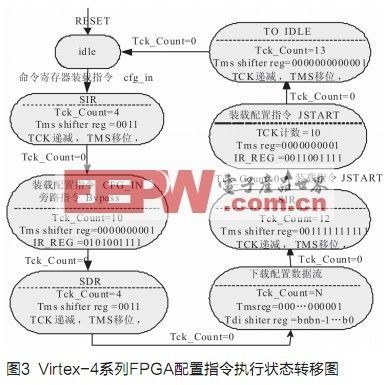

JTAG边界扫描配置的FPGA实现

TAP控制器是16个状态的有限状态机,主要为JTAG接口提供控制逻辑。主要有四大状态:复位(RESET),空闲(idle),数据寄存器移位(SDR)和指令寄存器移位(SIR)状态, 在TCK,TMS的控制下,根据输入的配置指令实现状态的转移。Xlinx公司Virtex4系列 FPGA器件的边界扫描指令集中有三条专用于配置的边界扫描指令:CFG_IN、BYPASS和JSTART(10个bit位)。其中CFG_IN的代码:0101001111;BYPASS的代码:1111111111;JSTART的代码:0011001111。执行CFG_IN指令可以访问器件内部的配置总线,通过串行移入配置文件中的命令和数据执行对内部配置寄存器的读写,从而完成对FPGA的配置。BYPASS指令在对多个目标器件配置时可以旁路不需要重配置的器件。JSTART指令使用TCK时钟触发启动时序,使FPGA完成从配置状态到操作状态的转换,激活FPGA。图3为可重构控制器模拟TAP状态机配置指令执行的状态转移图。

系统仿真

仿真在Active-HDL7.1软件下运行,所有仿真是基于对单器件配置的过程。

图4为JTAG边界扫描方式核心控制TAP状态机仿真波形 ,本文把整个下载模拟过程设计为三步,分别为TAP_Reset、TAP_CFG、TAP_JStart,ARM分别给三步提供一个启动命令,三个步骤分时按顺序由自己独立的状态机实现,由图可以看出状态衔接正确。

图5为各状态机个状态下接口输出波形,TCK、TMS、TDI时序和输出值满足JTAG扫描方式配置Virtex-4系列FPGA接口激励要求。

本系统ARM工作时钟为50MHz,TCK输出为25MHz,为便于观察,TAP_CFG部分状态机中SDR状态项实际由配置方案文件bit位数决定,仿真图有所压缩。

如果目标板FPGA是Virtex-4 XC4VLX25" title="XC4VLX25">XC4VLX25,其配置方案文件为995KB,整个配置过程大约所需时间327ms。

结语

本文介绍的重构控制器具有相对通用性,适用于对同一类FPGA芯片实现可编程器件在系统配置,使得硬件信息(可编程器件的配置信息)也可以象软件程序一样被动态调用或修改,从而动态的改变电路的结构和功能,对电路中出现的错误和故障进行实时动态重构,达到高可靠性的目的,有效节省逻辑资源,通过设计和仿真验证了此方法的可行性。