摘要:基于彩色面阵CCD传感器设计的高速实时图像采集系统,以信号处理芯片CXD3172AR为核心,可实现输出标准PAL/NTSC格式的视频信号,具有自动白平衡、自动曝光、缺陷补偿等功能,并构建优化的模拟前端电路(包括相关双采样和自动增益控制)大幅度提高了采集数据的信噪比。根据DSP芯片具有参数化控制的特点,通过单片机实现与DSP的特殊通讯传输协议来配置DSP参数,并使用外部开关控制完成各种信号处理功能。通过仿真调试,该电路很好地实现了图像采集和控制功能。

关键词:单片机;CCD;可控化;图像采集

光学成像系统是将光学信息转化为人们更易处理的电子信息的重要工具,特别对于智能监控、医学诊断及消费电子领域,其重要性就更大。随着成像系统功能的复杂化,摄像机的便携易控性成了设计中需考虑的重要要素。自从1969年Willard S.Boyle和George E.Smith发明电荷耦合器(CCD)以来,它一直就是光学成像系统的首选传感器。相对于目前发展快速CMOS图像传感器,它仍然具备噪声低,动态范围高的优点。而CCD的模拟前端决定了采集信号的质量,对整个系统信噪比有着决定性的影响,因此对它的噪声抑制是设计中的重点。完成各种图像处理功能的模块是成像系统的核心,针对低照度视频信号成像的设计要求,采用专业信号处理芯片进行各种处理,通过单片机(MCU)对信号处理芯片(DSP)进行参数配置,以完成各种复杂运算功能的控制,简化了系统的逻辑设计,使其具有良好的可控性。

1 系统组成

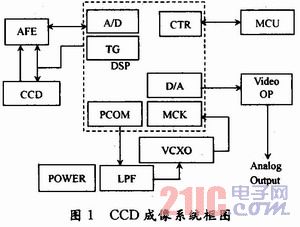

该系统由CCD、模拟前端AFE(包括相关双采样CDS和自动增益控制AGC)、信号处理模块、微处理器模块以及模拟数字输出模块等组成。系统框图如图1所示。

图中CCD传感器是整个系统的基础,外部光学信号通过光电转换才能进行各种处理。传感器输出模拟信号将经前端放大,以差分输入的方式进入AFE,然后通过一系列模拟信号的降噪放大处理(CDS,AGC),进入信号处理模块进行各种运算处理。信号处理模块是连接CCD输出和后端通用设备的桥梁,专业信号处理芯片提供了大量视频处理运算功能和多种视频输出格式,为后续处理带来了方便。通过DSP的各种处理,得到设计要求的色度、亮度和饱和度图像,最后输出与终端格式兼容的模拟或者数字信号。模拟输出可以直接与监视器相连,数字输出可以通过FPGA,ASIC等器件与VGA,DVI接口显示器相连。

2 模拟前端模块

CCD读出电路的噪声主要包括读出电路中所用器件的固有噪声,以及因电路结构、电路工作方式引入的附加噪声。主要有1/f噪声、KTC噪声和固定平面噪声,这些噪声限制了图像传感器的动态范围,降低了信噪比。在读出电路中,相关双取样技术(CDS)是目前应用最广泛的噪声抑制技术。由于一个像元传输时间中的复位噪声是相关的,相关双取样电路(CDS)可以利用信号相减的运算关系来消除或消弱信号里的1/f噪声、KTC噪声和固定平面噪声,从而可大大提高系统的信噪比。自动增益控制电路(AGC)可以使放大电路的增益自动地随信号强度而调整,使图像信号的亮度平稳,特别是低照度环境里微弱光信号的放大。但不足的是它也会放大低照度条件下的暗电流,降低图像质量。另外,模拟前端带宽的合理选择可以对系统噪声和系统调制传递函数进行折中,以满足应用的需求。目前有两种AFE设计方法,一种是采用分立元器件实现,另一种是采用集成AFE芯片实验。随着AFE芯片的成熟,其内部还集成了暗电流校正电路,各项指标远高于一般分立元器件搭建的电路,并且调试简单。该系统选择的集成AFE是CXA2096N,是专门为数字摄像机而设计的,内部包括相关双取样电路(CDS)、自动增益控制电路(AGC),为A/D转换器提供的参考电平以及采样保持电路,其自动增益变化范围为-0.8~31.3 dB。

3 信号处理模块

3.1 视频处理芯片

本文选择的信号处理芯片是SONY公司的CXD3172AR。该芯片内建10位高精度A/D转换器,具有自动白平衡、自动曝光、自动黑电平校正和缺陷补偿等功能,并能产生驱动CCD的时序脉冲,能够输出PAL/NTSC制式的模拟信号和ITU656格式的数字信号,其控制方式有2种:通过RS 232接口用PC机软件控制;通过MCU通用管脚直接用硬件控制。因为MCU的传输总线不属于通用的I2C和SPI总线,所以参考芯片资料,设计了与MCU的通信接口。该芯片支持的最大传输速率为400 Kb/s;使用PC机软件仅支持19.2 Kb/s,且不能完全利用该芯片的带宽,软件控制还必须依赖PC机,不利于携带。在该系统中,采用纯硬件控制方式实现的DSP功能,具有快速灵活的特性。以CXD3172AR为核心组成信号处理模块的外围电路主要有电源、时钟、视频输出接口和控制通信接口。

3.2 时钟产生电路

CXD3172AR需要产生驱动CCD的时序脉冲,其主时钟将影响整个系统的正常稳定工作。该系统选择的CCD兼容PAL制式色彩摄像机,总共像素为795(H)×596(V),系统要求28.375 MHz的时钟驱动系统和27 MHz的时钟驱动编解码器。为了有稳定的时钟源,采用锁相环路(PLL),用一个高稳定性参考源的一个分频和VCXO的一个分频进行相位比较,产生一个误差变化电压,给VCXO进行环路负反馈,从而使输出频率更稳定。设计VCXO输出28.375 MHz时钟和石英晶振回路输出27 MHz时钟,系统产生的水平同步信号频率为15.625 kHz,其与VCXO的分频进行相位比较,PCOMP引脚输出相位比较结果,判断是否相位锁定。

3.3 电源电路

系统需要4组独立电源,其电压分别为:3.3 V,5 V,15 V,-7 V。基于便携性的考虑,采用9 V直流电压作为电路板的输入,通过线性稳压电源芯片LT1117-3.3和LT1117-5得到3.3 V和5 V电压,选择TPS65131得到15 V和-7 V电压。TPS65131能够输出正负双电压,非常适用于便携性设备。4组电源的输出端分别通过LC低通滤波器,就能为系统提供高精稳定的直流电源。

3.4 视频输出电路

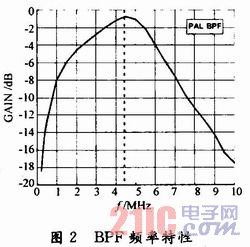

CXD3172AR能输出PAL制式的模拟信号,其输入端口采用电流输出结构,通过电阻产生信号电压,但是由于系统噪声的存在,特别是模拟地和数字的干扰,信号走线长度,元器件布局等因素,对输出端可以增加一级滤波器,以提高信噪比。对于亮度信号而言,芯片内部在输出端已集成了LPF,故只需对色度信号进行处理。设置DSP输出Y/C分离信号,视频信号的带宽一般为6 MHz,色度信号副载波频率为(4.43±1.3 MHz),图2是色度BPF的频率特性图。亮度信号和通过BPF的色度信号进入视频信号混合放大器NJM2274,其输出阻抗为75 Ω,放大后的信号可以直接输入监视器。

3.5 MCU-DSP通信

DSP处理功能可以通过MCU或软件进行控制。将DSP各控制参数通过特定的通信协议传输到DSP内部寄存器或者外部E2PROM保存,以使其实现视频信号的各种处理功能。这里的MCU为STC的STC89C52RC芯片,并且外搭基本硬件电路,使其成为最小系统。DSP控制参数有635 B,在调试的时候,可以存入DSP的寄存器组以便修改,调试完成之后,优化的参数可以存入E2PROM,使得下次掉电复位后可以继续使用。

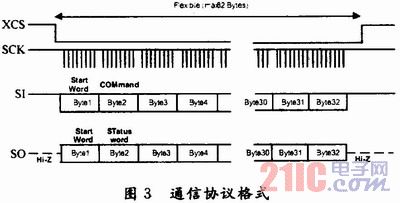

在通信过程中,一个通信协议包传输的字节数是可变的,最高可达32 B。DSP接收到一包数据后分析它,执行控制命令,完成1次通信。一个通信包由起始字、命令字、地址字和数据字组成。因为DSP内部寄存器数量有限,在执行完上次命令之前,不会再接收任何其他控制命令。该过程被称为“通信禁止周期”,并且此时,芯片返回一个确认数据,该数据可能是写应答信号、读取数据或者通信错误代码。它的片选信号、时钟信号和输入/输出信号格式如图3所示。

3.6 MCU与DSP的接口

在不同硬件接口之间进行数据通信时必须保证其逻辑电平一致,不然通信过程中将出现各种不可预料的错误。该设计中,CXD3172AR主供电电源VDD是3.3 V,其逻辑高电平大于等于0.7 VDD,逻辑低电平小于等于0.2 VDD,它们属于LVTTL电平。通用MCU管脚一般是TTL电平,所以两者之间的通信必须经过电平转换,这里选择SN74ALVC164245作为电平转换器。 SN74ALVC164245有2组独立电源端口,分别将其与MCU和DSP各自的主供电电源相连。这样,就能通过电平转换器将3.3 V系统和5 V系统连接起来。

4 仿真和调试

图4是软件仿真图,输入数据是低位先传,每个字节有8位,字节之间延迟1个时钟周期,DSP在时钟上升沿采样输入数据,在时钟下降沿输出数据。选通信号XCS为低电平有效,为了满足系统的一定时序冗量,在DSP处理时间内(即通信禁止周期)强制将XCS置高。由于是软件仿真的原因,DO没有波形。但是为了能够测试通信是否成功,在程序里添加回读显示功能,通过4个7端数码显示管显示2个16进制回读数据,判断是否通信成功。

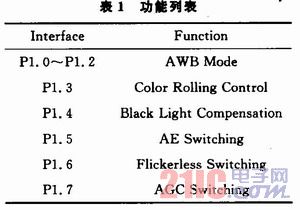

同时,参考DSP的几个基本功能,将其控制参数保存在程序代码中,通过外部开关的选择,MCU的P1端口读出其电平,实现各种功能的控制,其功能见表1。

完成电路板中各部分的设计以及调试后进行实验,其结果表明,MCU-DSP通信正常,可满足时序及功能要求。

5 结语

采用专业信号处理芯片及单片机实现了可控成像系统设计,完成了电路板的调试和功能实验,为后续数字信号处理提供了源图像信号。该系统具有电路实现简单可靠,功能控制方便,能够输出多种视频格式信号,具有简易灵活性。目前,将该系统已使用于低照度环境下的帧间滤波技术采集系统中,效果很好。