引言

随着信息技术的飞速发展,基于ARM在嵌入式系统方面的优势和CAN总线的广泛应用,目前越来越多的ARM处理器内部自带了CAN控制器,极大的方便了开发人员对CAN总线的开发。本课题是基于ARM2104的微处理器CAN总线系统节点开发,采用CAN总线可以将节点控制器直接安装在现场,数据经处理后发送到总线上,实现了信息的全数字方式传输,提高了传输的抗干扰能力,增加了信息的传输量。

总体设计方案

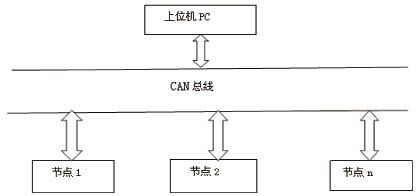

本课题中所设计的是CAN总线系统节点,系统节点结构图如图1。

图1 系统节点结构图

CAN总线系统应用要求:CAN总线接口的扩展、点对点通信。

CAN节点的设计主要是CAN通信控制器与微处理器之间、CAN总线收发器与物理总线之间的电路的设计。微控制器主要负责CAN控制器的初始化,进行与CAN控制器的数据传递,并按照预定的程序进行处理;CAN的通信协议主要由CAN控制器完成,CAN控制器主要负责将数据以CAN报文的形式传递,并进行系统的诊断、测试以及处理CAN总线上的错误等;而CAN总线收发器是CAN控制器和CAN总线之间的接口,完成物理电平的转换,功能是增大通信距离,提高系统的瞬间抗干扰能力,保护总线,降低射频干扰(RFI)。

通常一个完整的CAN节点应该包括三个部分:微控制器、CAN控制器、CAN收发器。目前广泛流行的CAN总线器件有两大类:一类是独立的CAN控器,另一类是带有在片CAN的微控制器。

CAN节点硬件电路设计

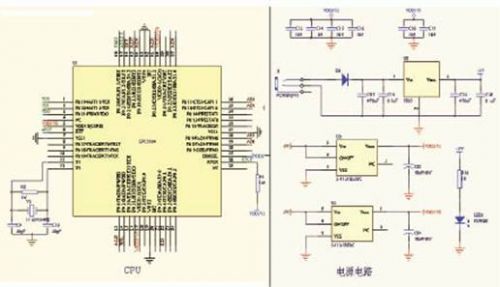

对于CAN节点硬件电路的的各接口电路的设计有:CAN接口电路、CPU模块、外围电路(复位电路和JATG接口电路)。其中CPU及电源电路如下图2所示:

图2 CPU及电源模块

LPC2104要使用两组电源,I/O供电电源为3.3V应用系统。首先,电源DW1将电源整流,经过C1、C3滤波,然后通过78M05将电源稳压至5V,再使用LDO芯片(低差压电源芯片)稳压输出3.3V及1.8V电压。LD0芯片采用S-1131B33UC和S-1131B18UC,其特点为输出电流大、精度高、稳定性高、功耗低。

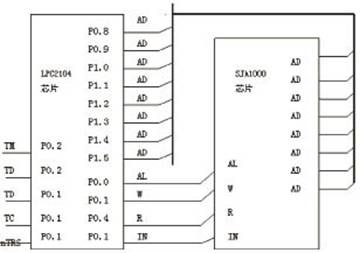

设计中的CPU芯片与控制器SJA1000的配脚图如图3所示。

图3 模拟总线硬件图

CAN节点的软件设计

CAN节点的软件设计主要包括ARM处理器的编程和SJA1000驱动程序的设计。在硬件电路确定以后,系统控制的主要功能将依赖于软件来实现。系统能否正常可靠的工作,除了硬件的合理设计以外,与功能完善的软件设计是分不开的。

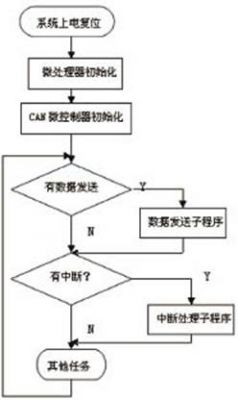

软件程序流程图如下图4所示:

图4 主程序流程图

配置软件包使用的GPIO必须在文件config.h中进行,其程序清单如列表1所示,其中程序清单(1)设置地址总线的宽度,只能为8、16、和24三个值之一。清单(2)设置信号AD0对应GPIO,其中0对应P0.0,1对应P0.1,以此类推。地址/数据总线的其它信号以这个信号为基准,顺序定义。清单(3)信号ALE对应GPIO,其中0对应P0.0,1对应P0.1,以此类推。清单(4)信号WR对应GPIO,其中0对应P0.0,1对应P0.1,以此类推。

程序清单列表1 配置总线使用的GPIO

#define ADDR_N_BIT 16 (1)

#define AD0_PIN_NUM 8 (2)

#define ALE_PIN_NUM 0 (3)

#define WR_PIN_NUM 1 (4)

#define RD_PIN_NUM 4 (5)

#include“exbus.h” (6)

本系统CAN控制器采用SJA1000,SJA1000控制器在微控制器正常通讯前,都必须先在相应地址寄存器中加载,确定接收标识码、总线接收波特率以及输出控制等,这就是CAN控制器的初始化。系统所用的CAN总线控制器SJA1000和CAN2.0A以及CAN2.0B两个版本的协议同时兼容。本系统设计以CAN2.0A的Basic CAN为协议标准进行设计。

测试之前编写的程序前首先要确定SJA1000的片选地址,确定与其他外部存储器无冲突。其次,微处理器对SJA1000的控制访问是以外部存储器的方式,来访问SJA1000的内部寄存器,所以应该正确定义微处理器访问SJA1000时,SJA1000内部寄存器的访问地址。

整个流程进行测试之后,SJA1000有8个不同的中断,这些中断可使主控制器立即作用在CAN控制器的某些状态上。一旦CAN产生中断,SJA1000就将中断输出(管脚16)设为低电平,直到主控制器通过读SJA1000的中断寄存器对中断采取相应措施,在主控制器响应后中断,或接收INFO里有更多有效数据,SJA1000立刻将中断输出再次设为低电平。采用中断接收的方式来接收数据,LPC2104的P0.16设置为外部中断INT,整个数据接收模块由数据接收函数void ReceiveData(uint8 *Rt)、中断处理函数CANException(void)构成。当SJA1000接收到CAN总线数据,通过接收中断使得LPC2104产生外部中断INT而使其进入中断处理函数,进而对接收到的数据进行处理。

可想,在CAN节点的软件设计的整个流程中,当硬件电路确定以后,系统控制的主要功能将依赖于软件来实现,并且能够正常可靠的工作。

结论

以ARM芯片作为主控制器,CAN总线作为数据传输方式来进行通讯的嵌入式系统得到了越来越广泛的应用。同时CAN通讯的可靠性也成为影响系统性能的关键部分之一。

本文以LPC2104为例,给出了一类微处理器与CAN控制器SJA1000之间的较为通用的硬件连接方法,对CAN总线节点进行了可靠性设计,采用CAN总线可以将节点控制器直接安装在现场,数据经处理后发送到总线上,实现了信息的全数字方式传输,提高了传输的抗干扰能力,增加了信息的传输量。

该设计现已在工厂车间中的车身控制系统中得到了应用,且运行可靠。