用AD7755设计的低成本电能表

2009-01-07

作者:(1)Anthony Colli

摘 要: 摘要介绍应用AD7755设计的低成本电能表技术报告,包括严谨的设计原理,精心的电路分析、先进的抗电磁干扰设计方案和详细的PCB布线图,本文对国内电子式电能表的生产具有重要参考价值。

关键词: 有功功率 功率因数 精度 电磁干扰

介绍了用美国Analog Devices Inc.(简称ADI)公司生产的AD7755设计的一种低成本、高精度电能表。本电能表是为单相、两线制系统设计的,但也容易适合特殊地区的设计要求,例如美国的配电系统通常要求居民电表采用单相、三线制系统。采用AD7755设计电子式电能表是一种电能测量的低成本单片解决方案。设计目的按照1级和2级交流有功功率电能表国际标准IEC1036(1996-09),作为本设计的主要依据。

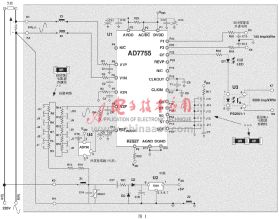

为满足多种情况下的精度要求,例如功率因数(PF)等于1时的精度要求和PF较低(PF=±05)时的精度要求,设计技术指标应该远远高过基本技术指标。另外电能表的动态范围也超过500。IEC1036标准规定在5%Ib~Imax电流范围内达到规定的精度要求。图1示出了用AD7755设计的一种简单、低成本电能表工作原理图。为了给AD7755提供必要的电流电压转换,本设计采用分流器,并且为衰减线电压采用了简单的分压网络。电能记录器(kWh)是一种用两相步进电机构成的简单机电式计度器。AD7755的F1,F2脚能够直接驱动这种计度器,CF脚还可提供仪表常数为3200imp/kWh(脉冲数/千瓦小时)的高频输出,所以这种高频输出可用LED和光电耦合器输出。这种高频输出还可加快电表的校验过程,从而为生产电表提供一种快捷的校验方法。本设计利用电阻网络R5~R14改变线电压的衰减来校验电表。

1 设计原理

AD7755产生的输出频率与两个输入电压信号乘积的时间平均值成正比。加在AD7755上的输入电压值为V1和V2。图1示出的电表工作条件,线电压为220V,最大电流(Imax)为40A。然而,只要正确标定通道1和通道2的输入信号,就能设计出工作于任何线电压和最大电流的电能表。AD7755有4种频率选择方式适合这类电表(即直接驱动计度器),Imax高达120A。当这类表的Ib选为5A时,规定精度的电流范围为2%Ib~Imax,或动态范围为400(即100mA~40A)。机电式计度器的电表常数为100imp/kWh,即要记录1 kWh的电能要求AD7755发出100个脉冲。IEC1036标准4.2.11节规定机电式记录器从最低位起按十进制计数,每位都是逢十进一。因此计度器采用5位整数1位小数显示方式,即最高位的1对应10,000,较低位依次对应1,000,100,10,1,最低位对应1/10。供校验和测试用的仪表常数选作3200imp/kWh。

2 AD7755基准源电路

图1中还示出了一个供选择的基准源电路。AD7755片内基准源电路的温度系数典型值为30ppm/℃,但A级AD7755的温度系数没有这么低,而高达80ppm/℃。在-20℃或+60℃情况下,由于80ppm/℃的温度系数使AD7755相对25℃标准值产生的误差要高达+0.65%。

3 分流器的选择

为了使通道V1(电流通道)的动态范围最大,分流器选为350μΩ。在为电表选择分流器时,有几个重要问题应该考虑。第一,要使分流器的功耗最低。由于本设计方案的最大额定电流为40A,所以分流器的最大功耗为(40A)2×350μΩ=560mW。IEC1036标准要求最大功耗为2W(包括电源功耗)。第二,如果功耗很高会给芯片散热带来困难。虽然分流器是采用低温度系数的锰铜合金材料制成的,但是在高温情况下对重负载仍会产生明显的误差。第三,应该考虑电表对相电压短路造成损害具有的防护能力。由于分流器的阻值非常小,所以外部短路对分流器的影响也非常小。因此分流器总是应该做得尽量小,但这样必然抵消通道V1(0~20mVrms,G=16)的信号范围。如果分流器做得太小,在轻负载情况下又不能符合IEC1036标准精度的要求。因此本设计权衡考虑分流器选为350μΩ。

4 设计值的计算

设计参数:

线电压=220V(标称值)

Imax=40A、Ib=5A

计度器=100imp/kWh

仪表常数=3200imp/kWh

分流器阻值=350μΩ

100imp/h=100/3600s=0.027777Hz

在Ib=5A条件下校表

Ib条件下功耗=220V×5A=1.1kW

Ib条件下F1(和F2)频率=1.1×0.027777Hz=0.0305555Hz

Ib条件下分流器(V1)两端电压=5A×350μΩ=1.75mV

根据AD7755活页资料的公式(1)计算为:

0.030555Hz=(8.06×1.75mV×V2×16×3.4Hz)/2.52

V2=248.9mVrms

因此为了校验这块电表需要将线电压衰减到248.9mV。

5 校验电表

从前一节可知通过将线电压衰减到248.9mV的方法能对这块电表做简单校验。线电压衰减是通过简单电阻分压器实现的。为了准许分流器的容差和片内基准源±8%的误差(见AD7755活页资料),该衰减网络应该允许至少有±30%的校验范围。此外,这种衰减网络布局的特点是,既使当衰减程度改变时,通道1与通道2之间仍能保持相位匹配。

两个通道间恰当相位匹配AD7755在40Hz~1kHz频率范围内,内部相位匹配。在电能计量应用中恰当的相位匹配是非常重要的,因为在低功率因数情况下两个通道之间的任何相位失配都会带来明显的测量误差。

如果相对AD7755外部产生一个相位误差(e),例如抗混叠滤波器,由此引起的测量误差按下式计算:

[cos(δ°)-cos(δ°+e)]/cos(δ°)×100%

其中δ为电压和电流之间的相角,e为外部相位误差。对于0 2°的外部相位误差,例如当PF=0.5(60°)时,计算测量误差为0.6%。这个例子表明,在低功率因数情况下即使很小的相位误差都会造成一个很大的测量误差。

6 抗混叠滤波器

如前所述,有一种外部相位误差源可能来自通道1和通道2的抗混叠滤波器。抗混叠滤波是一种低通滤波器,它放置在ADC的模拟输入之前。为了防止由于采样可能引起的失真(称作混叠)必须采用抗混叠滤波器。使用一种非常简单的低通滤波器(LPF)衰减掉那些无用的高频(900kHz附近)分量,从而可防止有用频带内的失真。最简单的LPF是RC滤波器,它是一种单极点滤波器,以-20dB/十倍频程衰减。

正如上一节所述,如果通道1和通道2的相频响应不匹配,会产生明显的误差。由于LPF的元件容差大很容易产生相位失配。LPF(抗混叠滤波器)的-3dB频率越低,在基频或电源频率附近引起的相位误差越明显。本设计为了减小由于相位失配造成的测量误差,抗混叠滤波器选取容差为1%的电阻器和容差为10%的电容器。这样抗混叠滤波器的转折频率扩展到10kHz-15Hz。但是转折频率不能太高,因为这样要允许足够高的混叠频率成份,从而在噪声环境下对精度有影响。

在低频情况下,对分流器寄生电感的补偿通常将分流器看作纯阻性元件,而不是电抗元件。但是当实际的数据采集系统使用分流器时在某些情况下,即使很小的寄生电感也会产生不合需要的影响。当分流器的阻值非常低时(200μΩ数量级),这个问题非常明显。图2示出了AD7755设计方案中采用的分流器的一种等效电路。分流器有三条接线。其中两条接线提供电流检测输入(V1P和V1N),第三条按线接系统地参考点。

通过对AD7755设计方案采用的分流器等效电路分析结果,指出了分流器的寄生电感对抗混叠网络的影响,主要因素是由于这种抗混叠网络增加一个零点所致。取消该网络附加零点(Zero)作用的一种方法是在同一位置(或靠近)增加一个附加极点(Pole)。

7 电源设计

本设计采用由电容器分压网络(即C17和C18)构成的简单低成本电源。大部分线电压都降落在电容器C17两端,它是一种560nF耐压250V的金属聚酯薄膜电容器。C17的阻抗决定电源的VA额定有效值。但C17的尺寸必须符合IEC1039标准的功耗指标的要求。包括电源在内的全部电压电路的总功耗应符合IEC1039(1996-9)标准4.4.1.1节的规定。在标称条件下,每相电压的总功耗是2W和10VA。本设计电源的标称VA额定值是7VA。总功耗大约为0.98W。在40A负载条件下包括分流器的功耗在内,电表的总功耗为1.54W。

8 抗电磁干扰设计

IEC1036标准的4.5节指出“电表设计应当遵循的原则是防止传导、辐射和静电放电三种形式的电磁干扰不损坏或实质性影响电表”。设计时应考虑如下三种干扰源:

(1)静电放电(ESD)

(2)高频电磁场

(3)快速瞬变脉冲群(EFT)

9 静电放电(ESD)

虽然许多对ESD敏感的电子元器件芯片内部都含有一些保护措施,但是对于下面介绍的那种剧烈放电则没有保护作用。另一方面,ESD作用是累积的,即一个器件可能经受住一次ESD作用,但不能保证在今后某一段时期能经受住多次ESD作用。最好的方法是,在ESD与敏感电子器件接触之前就消除或衰减ESD的作用。为了保护器件不必接入过多的外部元件,而应尽量让电路中已经接入的元件起到双重作用。例如在与外部有接触的那些点(如与分流器连接的点)必须防护ESD的作用。

RC滤波器对防止ESD损坏CMOS器件也有足够的保护作用,但是必须注意使用合适类型的元器件,例如电阻器不应选用线绕电阻器,因为在电阻两端会传导释放电荷。为了阻止电荷放电在电阻器两端传导,电阻器的体积应该大。在本设计中的抗混叠滤波器选用1/2W SMD 2010电阻器,还用两个铁氧体与分流器串联。铁氧体的阻塞作用对于减缓ESD电流脉冲快速上升时间特别有效。这种高频瞬时能量被铁氧体吸收后不再传送或反射给系统中的其它器件。另一个很常见的低成本方法是在PCB板的元件面制作火花隙(spark gap)来捕获ESD作用。但是,电表在一个开放环境下正常工作时要遭受多次ESD作用,所以在类似分流器的敏感连接点处不推荐采用这种方法。因为多次放电会使火花隙两端的碳增多,这样造成的短路或产生的电阻到时会影响电表精度。

为防止PSU中大幅度或快速上升时间的放电,在考虑选用金属氧化物压敏电阻器(MOV)之后,再采用火花隙。

10 高频电磁场

集成电路(IC)对射频(RF)的敏感度比较明显趋向在20~200MHz范围内。高于这个频段,寄生电容对敏感器件没有影响。一般对IC来说,20~200MHz频段的RF实际上范围已经很宽了,也就是说没有比这个频段更易出麻烦的。但是由于PCB的谐振作用,对某些频率可能更加敏感。这些谐振频率在某段频率范围内能产生插入增益,进而会对敏感器件造成干扰。到目前为止,最大量的RF信号都是经过电缆进入系统的,所以对这些连接点必须采取防护措施。系统抗高频干扰的主要措施是:

(1)缩小电路带宽

(2)隔离敏感器件

11 缩小电路带宽

本设计需要的模拟带宽仅2kHz,这对尽量减小RF影响是十分有利的。为了减少RF辐射进入系统,在电缆进入点可接一个低通滤波器。在进入AD7755之前,分流器的输出端已经滤波。这就是前边已经介绍的抗混叠作用。选择好元件并且增加一些必要的元件(例如铁氧体)能使这种抗混叠滤波器对RF的滤波效果加倍。

当频率很高时(例如>1MHz),必须考虑每个集总元器件的寄生电抗。

一般使用体积小、引脚短的元器件(例如SMD器件)使其寄生电抗保持最小。因为不知道确切的源阻抗(它取决于电源的源阻抗),所以一些通用的预防措施是减小潜在的谐振作用。由于源阻抗和滤波器网络相互作用产生的谐振能产生插入增益,从而在某个频点(谐振频率)会增加RF辐射对系统的作用。类似电容器(例如X7R型)这种具有介质损耗的元件(即大电阻元件)和铁氧体都是这种应用的理想元件。这种元件将RF辐射以热能形式被损耗而不是将其反射或传输给系统的其它元器件。铁氧体Z3和Z4在这方面具有优良的性能。

如前所述,由于铁氧体阻抗随频率增加而增加,所以它仅对高频RF有衰减作用。

12 隔离敏感器件

隔离分流器只能使AD7755(经过抗混叠滤波器)直接与“外部”连接。另一方面,为了提供电源和电压通道(V2),该系统还要接到相线和中性线。铁氧体(Z1)和电源滤波电容器(C16)应该对电源的RF辐射有明显的衰减作用。产生RF另外一个可能的途经是系统的信号地。为了使AD7755周围的信号地与外部接地参考点(K4)隔离,通常采用分隔(moating)法,图3示出了这种方法的原理图。

对系统中的敏感区域要防止RF辐射在I/O连接处进入系统。由于图中所示的I/O连接的周围区域没有任何接地面和电源面,从而限制了RF辐射的传导路径,所以称作“分隔”法。很显然,电源、地和信号必须跨过这个分隔区才能接通,因此图3示出了使用一个铁氧体可以安全地实现这种连接。

13 快速瞬态脉冲群(EFT)

EFT测试用来测定系统抵抗传导瞬态脉冲群的能力。按照IEC1000-4-4标准规定的条件进行测试。对EFT脉冲进行防护非常困难,因为这种干扰经过外部连接进入系统,例如电源线。使该脉冲特性衰减的最主要因素可能不是其幅度(高达4kV),而是由快速上升时间决定的高频成份。快速上升时间意味着该脉冲的高频成份能通过寄生电容等路径耦合到系统其它部分。PCB的印制线(traces)和信号地的感应作用能产生一个很大的差动信号。

类似ESD传导EFT带来的另一个问题是,这种辐射作用通常对电子元器件具有累积作用。一个EFT脉冲的能量高达4mJ,它能将40A的电流传输给50Ω负载。因此,由于感性负载的切换等原因表现出连续的EFT作用,对元器件的长期可靠性可能带来隐患。最好的方法是对EFT敏感的系统中的那些元器件采用防护措施。

上一节介绍的对高频电磁场的防护方法也完全适用于EFT。电子线路应尽可能地与通过PCB板的干扰源和滤波信号与电源连接隔离(即“分隔”)。另外在干线两端接一个10nF电容器(C16)以便为差动的EFT脉冲提供一个低阻抗分流器。由器件引脚和PCB印制线产生的寄生电感表明金属氧化物压敏电阻器(MOV)对衰减差动EFT脉冲不是很有效的。MOV对衰减大能量、持续时间相当长的干扰(例如闪电)非常有效。

14 S20K275型MOV

本设计使用的MOV是Simens公司的S20K275型MOV。MOV基本上是一种压敏电阻器,其电阻随电压增加而减小。MOV通常与被保护的器件或电路相并联。在过压期间形成一个低阻的分流器,因此可以防止被保护电路两端的电压进一步上升。这种过压保护主要是靠降低过压源的源阻抗,例如干线网络的源阻抗。

15 EMC测试结果

在一个独立的试验室对本设计的电磁兼容性(EMC)做了测试。全部测试都是由美国Integrity Design & Test Services Inc.(Littleton、MA 01460、USA)完成的。发射性测试报告的副本可从ADI公司的如下网址得到:

http:∥www.analog.com/techsupt/application?鄄notes/ad7755/64567-e1.pdf

抗干扰性测试报告的副本可从ADI公司的如下网址得到:

http:∥www.analog.com/techsupt/application?鄄notes/ad7755/64567-c1.pdf

由于篇幅所限,有关AD7755设计方案的详细讨论,包括四层电路板的布线图,元器件清单都不能详细介绍。感兴趣的读者请与北京市英赛尔器件集团及其分公司联系,或直接访问英赛尔器件集团的网址:incel.cn、com