在数据处理中为了更好地对被测对象进行处理和分析,研究人员们把重点更多的放在高速、高精度、高存储深度的数据采集系统的研究上

由于A/D芯片及高性能的FPGA的出现,已经可以实现高速高精度的数据处理,则进行大批量高存储深度的数据处理成为当前要解决的主要问题

l 常用存储器的比较

现在用于数据采集系统的存储器常见的有先进先出存储器(FIFO)、静态RAM和SDRAM等 FIFO由于容量和速度的限制,不是实现大容量存储的首选

FIFO由于容量和速度的限制,不是实现大容量存储的首选 目前,最为常见的存储器就是静态存储器(SRAM),静态存储器有控制简单、功耗低的优点

目前,最为常见的存储器就是静态存储器(SRAM),静态存储器有控制简单、功耗低的优点 当前大容量的SRAM可以达4 MB,存储时钟速率250 MHz

当前大容量的SRAM可以达4 MB,存储时钟速率250 MHz

如果要实现单通道32 M的存储深度和200 M的数据传输速度,就要由8×1片SRAM拼合起来才能实现 但由于每片SRAM都要有独立的地址对应存储的数据,这对设计者进行制版和布线都是一个极大的挑战

但由于每片SRAM都要有独立的地址对应存储的数据,这对设计者进行制版和布线都是一个极大的挑战 与静态存储器相比,单数据率动态存储器(SDR SDRAM)具有存储密度高、速度快等特点,数据线位宽可最大可以达到64 b,很适合于高速采样系统

与静态存储器相比,单数据率动态存储器(SDR SDRAM)具有存储密度高、速度快等特点,数据线位宽可最大可以达到64 b,很适合于高速采样系统 标准的SDR SDRAM可以达到的时钟频率达100 MHz以上,如果要满足系统存储速率的要求则至少需要有2×12 b的数据位宽,而目前并没有64 b或32 b的SDRSDRAM,则需要使用多片拼合

标准的SDR SDRAM可以达到的时钟频率达100 MHz以上,如果要满足系统存储速率的要求则至少需要有2×12 b的数据位宽,而目前并没有64 b或32 b的SDRSDRAM,则需要使用多片拼合 这样,对应于一个通道的存储就至少需要有2片12 b的动态存储器才能满足存储的需要,显然成本比较高

这样,对应于一个通道的存储就至少需要有2片12 b的动态存储器才能满足存储的需要,显然成本比较高

双速率同步动态随机访问存储器(DDR),是在SDRAM存储技术上发展而来的一种新型存储器件,在计算机行业得到了广泛的应用 其特点是采用了双倍速率结构实现高速操作,其在同一时间内传输的数据量是SDRSDRAM的2倍,最大传送数据的时钟速率可达400 MHz,而存储一个通道的数据只需要1片16 b的DDR,并且单位存储成本和SDR SDRAM相比并没有提高

其特点是采用了双倍速率结构实现高速操作,其在同一时间内传输的数据量是SDRSDRAM的2倍,最大传送数据的时钟速率可达400 MHz,而存储一个通道的数据只需要1片16 b的DDR,并且单位存储成本和SDR SDRAM相比并没有提高 因而,对于高速数据采集系统,无论从成本还是性能方面考虑,采用DDR作为系统的存储器件是合适的

因而,对于高速数据采集系统,无论从成本还是性能方面考虑,采用DDR作为系统的存储器件是合适的 但DDR却带来了相对复杂的控制工作,不仅需要与SDRSDRAM一样进行定时刷新,而且较SDRAM增加了新的控制信号和使用了新的电平标准

但DDR却带来了相对复杂的控制工作,不仅需要与SDRSDRAM一样进行定时刷新,而且较SDRAM增加了新的控制信号和使用了新的电平标准

2 DDR的基本工作原理

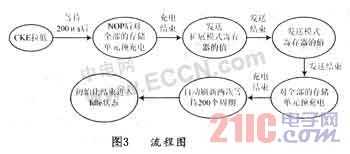

所谓DDR的双倍速率结构,即在数据随路时钟的上升沿和下升沿各发送一次数据,这样在一个时钟周期内可完成双倍速率的数据传输 由于DDR的控制逻辑比较复杂,这里只对其"写模式"下的工作原理进行介绍,如图1所示

由于DDR的控制逻辑比较复杂,这里只对其"写模式"下的工作原理进行介绍,如图1所示

|