摘要:论述了基于麦克风" title="麦克风">麦克风阵列的声源定位" title="声源定位">声源定位技术的基本原理,给出了利用FPGA" title="FPGA">FPGA实现系统各模块的设计方法。重点介绍了其原理和模块的电路实现,给出的基于FPGA设计实验结果表明,系统最大限度发挥了FPGA的优势、简化了系统设计、缩短了设计周期、符合设计要求。

关键词:声源定位;时延估计;FFT" title="FFT">FFT;CORDIC" title="CORDIC">CORDIC

声源定位,即确定一个或多个声源在空间中的位置,是一个有广泛应用背景的研究课题。基于麦克风阵列的声源定位技术在视频会议、声音检测及语音增强等领域有重要的应用价值。

声源定位算法目前主要有3类:第一类算法是基于波束形成的方法。这种算法能够用于多个声源的定位,但是它存在着需要声源和背景噪声先验知识以及对初始值比较敏感等缺点;第二类算法是基于高分辨率谱估计的方法。这种算法理论上能够对声源方向进行有效估计,但是计算量较大,且不适于处理人声等宽带信号;第三类算法是基于到达时间差的方法。由于这种方法原理简单,计算量较小,且易于实现,在声源定位系统中得到了广泛应用。根据以上介绍,本文决定选择第三类即基于到达时间差的定位方法。

基于到达时间差声源定位算法包括2个步骤:

1)先进行时延估计,从中获得传声器阵列中相应阵元对之间的声音到达时延。常用的方法有最小均方自适应滤波法、互功率谱相位法和广义互相关函数法。

2)利用时延估计进行方位估计,主要方法有角度距离定位法、球形插值法、线性插值法和目标函数空间搜索定位法。与其他几种方法相比,基于广义互相关函数的方法计算量小、计算效率高。优点明显,故时延估计采用此方法。方位估计则采用精度适中、易于实现的角度距离定位法。

FPGA具有高速处理能力,而且开发灵活,易于在线系统升级,能较大缩短系统的开发周期。为此,采用Ahera公司的FPGA处理器件实现本系统。

1 系统的基本原理及流程图

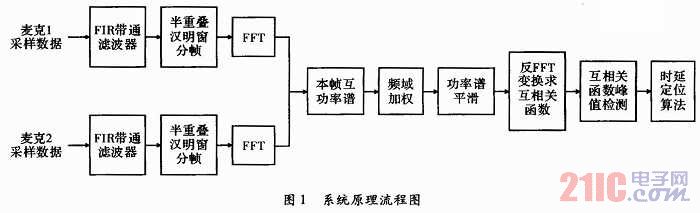

算法的结构流程如图1所示,首先由麦克1和2获得说话人的语音信号,再经过A/D采样和低通滤波器,最后得到待处理输入语音信号,可以分别记为x1(n)和x2(n)。

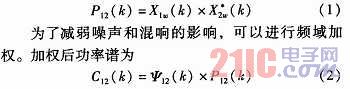

经过FIR带通滤波器后,用半重叠汉明窗对x1(n)和x2(n)加窗可得X1w(n)和X2w(n),然后即可求得x1(n)和x2(n)的互功率谱为

为进一步突出峰值,在频域加权后,可对麦克信号间的互功率谱平滑,得到

其中,m表示累加平滑的帧数。

接下来对求傅里叶反变换,即可以得到麦克1和2间的广义互相关函数为

其峰值就是麦克1和2之间的时延。得到多对麦克间的时延后,由角度距离定位法,就可得到声源位置。

2 各模块设计实现

2.1 FIR带通滤波模块

为了消除噪声和回声干扰的影响,首先需要进行滤波。语音信号的带宽是0.3~3.4 kHz,因而需要设计一个带通滤波器滤除语音信号带宽之外的噪声。为了使处理过的信号相位不发生变化即保持线性相位,需要采用FIR滤波器。

这里采用切比雪夫逼近法,由Matlab滤波器设计工具求得滤波器的各系数,乘以1024进行量化,转化为CSD编码以提高其运行效率,最后由Verilog代码实现。

2.2 半重叠汉明窗模块

为了保证语音信号平稳性,一帧信号的时间窗长度选为10~30 ms。而采样器频率为10 kHz,为了便于FFT处理选择25.6 ms即帧长为256点。为了保证统计特征的连续性和得到更好的语音处理效果,各帧之间进行50%的重叠,即每次处理只更新12.8 ms的数据。这样,一帧内的信号可以近似认为是平稳的。

分帧是用可移动的有限长度窗口进行加权的方法实现,这就是用某窗函数w(n)乘以s(n),从而形成加窗的语音信号sw(n)=s(n)×w(n),其中窗函数的值存储在内部存储资源中。常用的窗函数有汉明窗与矩形窗,汉明窗比矩形窗的平滑效果更好,故选择汉明窗,其表达式如式(5)所示

其中,N是帧长。

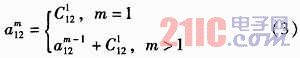

2.3 FFT运算模块

由于语音信号是连续的实时采样,为了能使传来的语音信号连续不断的处理,这里采用了乒乓结构,即采用两个分别能存储一帧数据的双口RAM,第一个RAM在存储新数据时,第二个RAM进行FFT运算,并存储其结果。然后,第一个RAM进行FFT运算,并存储其结果,第二个RAM存储新的数据,这样就保证了信号处理的连续性。

乒乓存储时由倒序地址模块产生倒序存储地址,使RAM中存储数据为倒序,为FFT运算做准备。为了加快运算速度,蝶形运算旋转因子,先由Matlab软件生成,量化为12位带符号数,然后存储在内部ROM里面。

整个FFT运算单元由状态机设计完成,共由5个状态完成;S1状态输出第一个操作数地址;S2状态得到第一个操作数,输出第二个操作数地址;S3状态得到第2个操作数,计算出第一个结果;S4状态寄存第一个结果,计算出第二个结果;S5状态寄存第二个结果,产生下一级运算地址。

2.4 本帧互功率谱模块

第一路信号FFT结果与第二路信号FFT结果的共轭相乘得到本帧互功率谱。

若第一路是r1+i1,第二路是r2+i2,其共轭为r2-i2,相乘时可用式(6),式(7)所示的计算方法,这样可以减少一次乘法运算,节省内部资源

![]()

其中,R和I是本帧互功率谱的实部和虚部;r1和r2是FFT结果的实部;i1和i2是FFT结果的虚部。

2.5 频域加权模块

本帧互功率谱乘以存放在ROM中的加权函数,使互相关函数峰值更加突出。调用内部乘法器模块即可完成。

2.6 功率谱平滑模块

对加权模块结果,进行连续数帧的累加以平滑互功率谱,使峰值便于检测。调用内部加法器模块即可完成。

2.7 反FFT模块

对平滑结果进行反FFT运算,求得互相关函数。根据FFT原理,反FFT运算可借助于FFT模块计算。即将FFT运算中旋转因子取倒数,最后的输出乘以1/N就可以用来计算反FFT。为防止运算过程中发生溢出,可将1/N分配到每一级蝶形运算中。由于1/N=(1/2)M,所以每级的每个蝶形输出支路均有一相乘因子1/2,即右移一位即可。

2.8 峰值检测模块

对FFT结果求模即是求![]() 的值,然后求出其模值的峰值,即相应的语音信号时延值。

的值,然后求出其模值的峰值,即相应的语音信号时延值。

2.9 定位算法模块

根据角度距离定位法,声源相对原点的水平角θazimuth为

![]()

其中,a是麦克之间的间距;d是声源到麦克对的距离差。

声源相对原点的仰角φelevation为

![]()

其中,a是麦克之间的间距;d是声源到麦克对的距离差。

由上可知,需要计算反余弦函数值确定出相应的角度值。反余弦函数是超越函数,可以用泰勒级数近似计算这个函数,但较为麻烦且精度不高,而CORDIC算法是由移位和加减运算组成,所以比较适合FPGA的实现,速度较快且具有较高的迭代精度。本系统使用高速9级流水线结构实现CORDIC算法。迭代关系如下

式(10)是迭代的初始条件,式(11)是根据本次坐标值判定下次迭代方向,式(12)~式(14)是下次迭代公式。

算法经过数次迭代后θ的值即是*****。实际中使用9级迭代,可以得到7位精度。最小角度精度为0.111 905。

3 模块仿真和综合报告

Quartus II是Altera公司开发的综合性PLD软件,内嵌综合器和仿真器,可以完成从设计输入到硬件配置的完整PLD设计流程。而且具有运行速度快、界面统一、功能集中、易学易用等特点。

本设计使用Quartus II8.0对各个模块进行仿真验证。通过仿真,验证了各个系统模块可以准确的工作,并完成了整个设计功能。选取Alte-ra公司Cyclone II系列中的EP2C35F484C8器件对整个程序进行时序仿真,其主要资源消耗为:总逻辑单元为3740/3 3216,总存储单元为74 240/483 840,总管脚为387/475。总乘法器为16/35。仿真结果表明,本文所述实现方法结构可行,可以获得良好的性能,其最高速率可以达到87.3 MHz,完全满足系统要求。

4 结束语

本设计通过FPGA来实现整个系统,充分利用了Altera公司FPGA产品高速大容量开发灵活方便等优点,并使用QuartusⅡ开发环境所提供的库资源,同时最大限度地利用和发挥了FPGA的优势,从而简化了系统设计,缩短了设计周期。