FPGA是一种现场可编程器件,设计灵活方便可以反复修改内部逻辑,适用于算法结构比较简单、处理速度较高的情况。DSP是一种基于指令集的处理器,适于大信息、复杂算法的信息处理场合。鉴于两种处理器件自身优势,FPGA+DSP信号处理架构,已成为信号处理系统的常用结构。但当前FPGA+DSP的信号处理平台或者是基于某些固定目的,实现某些固定功能,系统的移植性、通用性较差。或者仅仅简要介绍了平台的结构没有给出一些具体的实现。

本文提出的基于FPGA+DSP通用信号处理平台具有两种处理器的优点,兼颐速度和灵活性,而且可以应用在不同雷达信号处理系统中,具有很强的通用性。本文举例说明该系统在连续波雷达和脉冲雷达中的典型应用。

1 系统资源概述

1.1 处理器介绍

本系统FPGA选择Altera公司的EP2S60F1020。Stratix II FPGA采用TSMC的90 nm低k绝缘工艺技术。Stratix II FPGA支持高达1 Gb·s-1的高速差分I/O信号,满足新兴接口包括LVDS,LNPECL和HyperTransport标准的高性能需求,支持各种单端I/O接口标准。EP2S60系列内部有48 352个ALUT;具有2 544 192 bit的RAM块,其中M512 RAM(512 bit)329个,M4K RAM(4 kbit)255个,M-RAM(512 kbit)2个。具有嵌入式DSP块36个,等效18bit×18bit乘法器144个;具有加强型锁相环EPLL 4个,快速锁相环FPLL 8个。这些锁相环具有高端功能包括时钟切换,PLL重新配置,扩频时钟,频率综合,可编程相位偏移,可编程延迟偏移,外部反馈和可编程带宽等。

本系统DSP选择ADI公司的ADSP TS201。它有高达600 MHz的运行速度,1.6 ns的指令周期;有24 MB的片内DRAM;双运算模块,每个计算块包含1个ALU,一个乘法器,1个移位器,1个寄存器组和1个通信逻辑单元(CLU);双整数ALU,提供数据寻址和指针操作功能;集成I/O接口,包括14通道的DMA控制器,外部端口,4个链路口,SDRAM控制器,可编程标识引脚,2个定时器和定时器输出引脚等用于系统连接;IEEE1 149.1兼容的JTAG端口用于在线仿真;通过共享总线可以无缝连接多达8个TigerSHARC DSP。

1.2 FPGA+DSP结构

由于FPGA和DSP各自的自身优势,FPGA+DSP信号处理架构已成为信号处理系统的常用结构。一般情况下FPGA+DSP的拓扑结构会根据需要进行不同的连接,这就导致这种结构的专用性,缺乏灵活性。对于一个通用处理平台要考虑到各种不同的信号通路,因此大部分通用FPGA+ DSP平台都采取各个处理器间均有通路的方式。这种拓扑结构灵活方便,可以满足各种不同的通路需求,这种结构的缺点就是硬件设计的复杂以及可能会有资源浪费。对于这种通用FPGA+DSP结构,FPGA与各个DSP之间均有连接,不同之处便是DSP之间的拓扑结构。一般分两种,一是高速外部总线口耦合结构组成多DSP系统,这种结构可以实现多DSP共享系统内的资源,系统内的个处理器可以共享RAM,SDRAM和主机等资源,还可共享其他处理器核内资源。这种结构的长处就在资源共享上,但这种结构的PCB设计十分困难,而且当总线负载较重时速度很难提高,要达到50~60 MHz的数据速率都很难。另外一种结构就是高速链路口耦合结构。ADSP TS201有4个高速链路口内核时钟600 MHz时,单向数据传输率最高可达600 MHz。高速链路口通信是点对点的,这是它的局限,但也带来的一个优点就是较高的传输可靠性。在本信号处理系统中采用第2种结构。

1.3 本信号处理系统的硬件结构

在充分考虑系统的通用性能上,本系统在硬件结构上采用1片FPGA与4片DSP的拓扑结构。每片DSP与FPGA分别有一路链路口相连,4片DSP之间由链路口相连,同时,DSPA与DSPD分别有64位的数据总线与FPGA相连。这种拓扑结构使得任意两片DSP之间都可以连通,对角的DSP可以通过连到FPGA内部的链路口相互通信。此外,本系统采用一片FLASG存储DSP程序,对所有DSP进行加载。DSPB,DSPC分别连有32×64 Mbit的SDRAM,对DSP的内存空间进行了扩展,便于大量数据处理,如图1所示。

2 具体应用

2.1 在连续波雷达中的应用

其主要功能是完成对接收的全相参体制的双波束原始视频信号的数字采样信号进行相关处理,其中包括时/频转换、MTI、MTD处理、双波束估高处理等,最终能够对动目标进行检测。

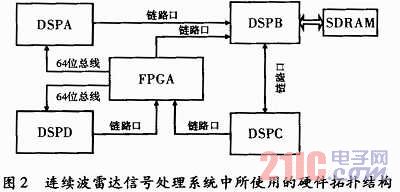

拓扑结构:待处理数据通过接插件传送到FPGA内部,通过FPGA的初步处理,经由FPGA与DSPA、DSPD相连的64位数据总线传送到两片DSP内进行进一步的处理。DSPA将处理完的数据经过链路口直接传送到DSPB,而DSPD将处理完的数据通过DSPD到FPGA,FPGA到DSPB的链路口也传送到DSPB。DSPC接收DSPB处理完的数据并将数据进行进一步的处理后通过链路口传送到FPGA输出。如图2所示为应用所使用的硬件拓扑结构。

处理流程:FPGA将接收到的两路信号分别进行4 096点FFT,并对FFT的结果进行MTI,MTI可以是根据命令选做。DSP中完成两路信号的二维FFT也就是MTD,CFAR,估高,杂波图等,最后将整理后的结果输出到FPGA,由FPGA输出给雷达的其它模块,如图3所示。

资源的使用:在FPGA需要完成的功能为两路复信号的FFT,MTI,以及与DSP的数据通信。FFT的实现采用Altera公司的FFT IP Core实现,它是一个高性能、高度参数化的快速傅里叶变换(FFT)处理器,实时正序输出变换结果。采用缓冲突发模式4输出引擎结构完成一路4 096点FFT。MTI采用3次相消器即4脉冲对消法,在FPGA中采用FIFO实现。与DSP的总线数据通信的实现为FPGA将待传输数据写到FIFO中同时向DSP发送中断,DSP响应中断后从FIFO中将数据读出。与DSP的链路口数据通信,无论是接收链路口还是发送链路口均由一个数据缓冲模块和一个数据拆包/打包模块组成。表1为FPGA中资源时间的具体使用,由此看出EP2S60F1020的资源丰富。

在DSPA,DSPD中接收数据采用乒乓操作,在接收一组数据的同时对已接收的数据进行操作,完成数据的定浮转换和MTD。应用中用N点傅立叶变换实现N个窄带多普勒滤波器实现MTD。在DSPB中实现恒虚警检测(CFAR),采用的是两侧单元平均选大CFAR处理(GO—CFAR),也就是从被检测电路单元前后各取一段距离范围的回波信号,分别计算前后两部分的平均值,选取平均值较大的一个乘以门限因子C作为检测门限,与被检测单元作比较,如果被检测距离单元的回波幅度高于检测门限,就可认为被检测距离单元有目标存在。被检测单元前后各空出几个参考单元避免目标本身对门限值的影响。速度维聚心是指,对同一距离单元的各个通道道进行幅度峰选,取出其中的最大值作为目标所在的速度通道号。杂波图的实现,首先建立杂波图,然后选取零通道数据并根据已知的方位信息及递归公式更新杂波图中数据。假设DSPA和DSPD接收到的数据位每周期1 024点的数据,DSP需要每8周期一滑窗做32脉冲的MTD,CFAR取8个单元平均选大,则DSP中各功能所占资源如表2所示。

2.2 在脉冲雷达中的应用

功能:完成对接收的全相参体制的回波信号的中频采样信号进行相关处理,其中包括DDC、脉冲压缩、MTI、MTD处理、CFAR、测角等,最终能够对动目标进行检测。

所用到的拓扑结构:待处理数据通过接插件传送到FPGA内部,通过FPGA的初步处理,经由FPGA与DSPA、DSPD相连的64位数据总线传送到两片DSP内进行进一步的处理。DSPA将处理完的数据经过链路口直接传送到DSPB,DSPD将处理完的数据直接传送到DSPC。DSPC处理完自身数据并接收DSPB的数据并将数据进行进一步的处理后通过链路口传送到FPGA输出。如图4所示为应用所使用的硬件拓扑结构。

处理流程:FPGA将接收到的和差两路信号分别进行DDC以及低通滤波,并对结果进行整理,和路信号发送给DSPA,差路信号发送给DSPD。在DSPA和DSPD中分别进行和路以及差路信号的脉压、MTI,其中MTI可以是根据命令选做的。DSPA将处理完的信号传送给DSPB,DSPD将处理后的数据传送给DSPC,在DSPB和DSPC中进行和路以及差路信号的MTD、MOD、CFAR,同时DSPC接收DSPB处理后的信号,在DSPC中进行和差比商测角,最后将整理后的结果输出到FPGA,由FPGA输出给雷达的其它模块,如图5所示。

资源使用:在FPGA需要完成的功能为两路信号的DDC、低通滤波,以及与DSP的数据通信。其中在做DDC时为了便于测试在FPGA内部有Mat-lab产生的两组数据分别作和差两路数据的内部源数据。与DSP交互部分无论是总线传输还是链路口传输均与连续波雷达信号处理实现方法一致,在此不再赘述(假设FPGA到DSP传输数据为1 024个复数)。则在FPGA中占用的主要资源如表3所示。

在DSPA和DSPD中以乒乓方式接收FPGA的数据完成数据的定浮转换,脉冲压缩和MTI。其中脉冲压缩采用频域脉压的方式,然后对脉压结果作MTI,采用四脉冲对消。在DSPB和DSPC中要完成数据的MTD,MOD,CFAR,最后在DSPC中实现测角,最终将目标数据结果传输给FPGA。这些功能的实现与连续波雷达实现这些功能方法相同,在此不再赘述。则在DSP中所占用的资源如表4所示。

2.3 几个重要模块的速度

在实时信号处理系统中,系统的速度至关重要,本文所介绍的平台在各个接口及模块上均能达到不错的速率。

(1)FPGA与DSP总线传输速率。

在本系统中总线传输可以采取流水协议,零等待周期的配置,这样总线速度可以达到DSP SCLK的速度,在本系统中为50 MHz×64 bit的速率。

(2)FPGA与DSP链路口传输速率。

在本系统中链路口采取四位模式,则链路口可以配置成150 MHz,300 MHz,400 MHz,600 MHz。经过测试,FPGA与DSP之间的链路口速度可以达到400 MHz×4 bit的完美无错传输。

(3)DSP与DSP链路口传输速率。

经过测试,DSP与DSP之间的链路口速度可以达到600 MHz×4 bit的无错传输。以上几个速率为数据传输十分重要的几个接口的速度,通过测试数据可知,系统可以达到较高的,完全可以满足信号实时性的要求。

3 结束语

针对当前FPGA+DSP的信号处理平台现状,提出一种通用的硬件结构,该结构不仅将两种处理器的优点集于一身,兼顾速度和灵活性而且可以应用在不同雷达信号处理系统中,具有很强的通用性。分别介绍了此平台在连续波雷达以及脉冲雷达中的一种应用,并且这些方法已经成功应用于雷达信号处理机中。除了文中列举的方法外由于本结构硬件连通的灵活性,本结构可以根据需要应用于各种雷达处理系统中。