实时红外弱小目标检测跟踪系统

2007-11-13

作者:杨灿军1, 李建勋2,林志行2,

摘 要:针对红外弱小目标检测" title="目标检测">目标检测和跟踪的实时性要求,基于法国Sofradir中波(3~5μm)红外热成像仪" title="红外热成像仪">红外热成像仪和英国Hunt Engineering的双DSP管理板卡HEPC9、双DSPC6201和双FPGA搭建了一套实时红外图像" title="红外图像">红外图像处理系统" title="处理系统">处理系统。同时针对C6201微处理器成功地实现了弱小目标检测和跟踪程序的优化和移植。系统测试表明,该系统可实时、有效地检测跟踪每秒50帧,每帧320×240像素,每像素14位的低信噪比的复杂序列图像。

关键词:红外热成像仪 双DSPC6201 目标检测与跟踪

红外弱小目标的检测与跟踪方法,是红外搜索与跟踪系统、精确制导系统、红外预警系统、大视场目标监视系统、卫星遥感系统等的一项核心技术。焦平面红外探测器具有极强的抗干扰能力,而且在作战中不会产生各种辐射,隐蔽性好且适应能力强; 红外成像可穿透烟雾,分辨率高,空间分辨能力更可达0.1毫弧度;红外成像不受低空工作时地面和海面的多路径效应影响,低空导引精度很高,可直接攻击目标要害,具有多目标全景观察、追踪及目标识别能力,可整合微处理器实现对目标的热成像智慧型化导引,具有良好的抗目标隐形能力。

然而在低信噪比条件下,尤其是针对实际情况下的各种背景干扰、人为干扰以及探测器低频扫描噪声和高频探测噪声所导致的低信噪比条件下,目标点极易被噪声所淹没,从而难以实现对弱小目标的可靠检测和跟踪。实际上,现有的弱小目标检测和跟踪算法[1~3]主要适用于信噪比较高的情况,而且普遍存在一个共同的致命弱点:计算量大、运行时间长,无法满足实时处理的要求。因此,尽快研究出一套实用的弱小目标检测与跟踪的红外图像处理" title="图像处理">图像处理系统就成为一项亟待突破的关键技术。

针对上述问题,本文成功地研制了一种针对实际应用的红外图像处理系统。该系统基于法国Sofradir中波(3~5μm)红外热成像仪和英国Hunt Engineering的双DSP 管理板卡HEPC9,双DSPC6201和双FPGA搭建了一套实时的红外图像处理系统。同时针对红外弱小目标(大约2dB)检测和跟踪的实时性要求,基于C6201微处理器成功地实现了弱小目标检测和跟踪程序的移植和优化,实现了高精度红外图像的实时采集、传输、处理和显示,具有良好的性能和广阔的应用前景。

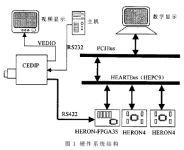

1 硬件原理

硬件系统结构如图1所示。为了确保构建的图像处理系统可以达到原理样机的要求,同时在实际条件又没有合作飞机的前提下,将图像处理系统的样机功能分解为:高精度图像的高速稳定传输和实测数据的实时处理两个部分。(1)针对Sofradir中波(3~5μm)红外热成像仪,基于HEPC9母卡的双DSP管理功能,采用双DSPTMSC6201实现对图像的并行处理,提高运算性能。同时采用一个FPGA用于实现数据接收的时序和控制,其时序严格按照法国Sofradir中波红外热成像仪的实际时序(见图4),以验证系统的高速稳定通信能力。(2)基于HEPC9母卡的双DSP管理功能,采用双DSPTMSC6201实现对图像的并行处理,提高运算性能,同时采用双FPGA系统。一个FPGA用于实现数据接收的时序和控制,其时序严格按照法国Sofradir中波(3~5μm)红外热成像仪的实际时序(见图4);而另一个FPGA用于与调用硬盘中存储的实际测试数据一起模拟实际的测量环境。为实现每秒50帧的处理能力,采用了具有可编程序的板卡HERON-FPGA3S,实现对真实环境和实测数据的有效测试。

该系统可广泛地应用于实际测试图像的后期处理和检测跟踪算法的实际性能考核,具有极大的试验和测试功能。实时红外图像处理系统由三部分组成:

(1) 红外成像仪

红外成像仪采用法国SOFTDIR生产的红外头部以及美国CEDIP公司生产的后续处理板卡组成。红外摄像仪具有两个输出端口和一个RS232控制端口。一个输出端口为模拟的视频输出端口,可以使用监视器进行图像的实时观察。另一个输出端口是RS422平衡式差分数字信号输出端口。RS232串行控制端口用来控制摄像头的性能参数,如:调节数字图像的输出速率(25帧/秒、50帧/秒和100帧/秒可选)、图像的积分时间以及校正图像以达到最佳的成像效果。

(2) 图像的接收和处理模块

红外图像的接收和处理板卡及芯片采用英国HUNT公司生产的板卡HEPC9和HERON-FPGA3S以及HERON4。HEPC9是一块母卡,作为HUNT公司各种处理板卡的载体,采用环形的HEART总线来规划各个模块的通讯功能,通过PCI总线与主机通讯。HERON-FPGA3S是一块FPGA板卡,用于解析红外摄像仪的电平信号和接收红外图像数据。HERON4是TIC6201DSP板卡,负责对红外弱小目标的检测和识别。另外还需要一个由多个MC3486组成的板卡模块将红外摄像仪的RS422差分信号转换为TTL单端信号。

(3) 系统控制和显示模块

整个系统的控制和显示部分由PC机完成,这里使用ADLINK公司的工控机PENTIUM Ⅲ 866,内存128MB。

2 各子模块具体实现

2.1 Hunt Engineering 产品简介[8]

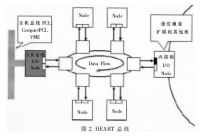

(1)母卡HEPC9

HEPC9是一个可以集成4个HERON模块的主板卡,各个模块之间的连接关系是可编程的,具体由network文件规定。母卡具有6个32bit的同步虚拟输入FIFO,6个32bit的同步虚拟输出FIFO,模块之间通过这些虚拟的FIFO进行连接。虚拟FIFO是母卡中环形HEART总线的一部分,如图2所示,通过令牌环(标志位)的设置分配数据的传输带宽和时间片,这部分功能对于用户是透明的。每个FIFO的同步时钟可以达到60M~100MHz,使FIFO的输入输出速度可以达到4×100MBps。

(2)HERON-FPGA3S

HERON-FPGA3S可编程逻辑芯片在系统中用于接收红外摄像仪图像数据,并具有存储功能。具有200K门,最大时钟频率可达180MHz,I/O带宽达400MBps。

(3)HERON4-DSPC6201

这是一块基于TI公司TIC6201DSP的HERON系列的板卡,具有200MHz主频的16位定点DSP,采用哈佛结构,具有64KB的片内程序存储器PROM和64KB的片内数据存储器IDRAM。HERON4-DSP板卡增加了512KB的片外突发存储器SBSRAM和16MB的片外动态数据存储器SDRAM。DSP具有八条流水线,可以使指令并行执行,这对于大数据量的图像处理非常重要。

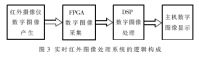

2.2 系统的逻辑构成

实时红外图像处理系统在逻辑上要完成一个完整的数据传输、处理、显示过程。其逻辑构成如图3所示。

母卡通过编写network文件下载到母卡的存储器中,修改特定的标志寄存器,实现拓扑连接方式。这里的两片DSP采用流水线处理方式,即两者协同完成同一图像处理工作的先后两部分,以提高处理速度。在一些情况下,也可以将两块DSP描采取并行处理的方式,即两块DSP同时处理不同的数据。

(1)FPGA图像数据的采集模块

红外摄像仪的逻辑时序如图4所示。图中:帧控信号FRAME高电平有效,在FRAME信号上升沿后出现第一帧数据时钟;行控信号LINE_VALID上升沿有效,在其上升沿后每行数据有效,则时钟信号CLOCK上升沿像素信息有效;数据信号PIXEL_DATA共有14对数据线,产生14位数据,每行有320个时钟,每帧有240行,一帧总共具有320×240=76 800个14bit的有效像素信息。

(2) DSP数字图像处理模块

这是整个系统的核心模块,其功能是利用采集到的图像数据进行数字图像的处理。

利用HUNT公司的嵌入式模块“Create New HREON-API project”,可以建立一个完整的基于以上硬件结构的系统程序框架。该软件框架基于TIDSP的DSP/BIOS结构,是一种小型的嵌入式实时操作系统,可以对DSP系统的各种资源(如内存、信号量等)进行规划管理。本系统中DSP图像处理模块的整体框图如图5所示。

通过FPGA上的标志寄存器协调DSP和FPGA之间的通讯,在准备接收图像数据之前,清空接收FIFO,然后通过串口HSB使能FPGA的发送允许标志位通知FPGA发送数据。在接收图像到帧存之后,同样通过HSB设置这个标志使FPGA停止发送。

(3)主机控制显示模块

这部分是运行于PC机上的程序。其作用是完成整个系统的控制模块和显示模块功能。

红外摄像仪所拍摄的数字图像具有14位的像素精度,虽然是有利于图像处理精度,但由于无法在一般的显卡上显示超过256级灰度的灰度图像,因此有必要采用先灰度均衡再线性映射的方法,将14位的高精度图像压缩为8位的灰度图来显示,以达到人机界面显示的功能。

3 弱小目标检测跟踪及在DSP上的实现

红外序列图像中运动的弱小目标的检测算法包括形态学滤波和能量特征匹配两部分,即基于能量特征的弱小目标检测方法。同时还包括利用数据关联进行多帧积累实现的序列图像跟踪,从而实现了对低信噪比的复杂序列图像的实时、有效的检测和跟踪[4]。

在实时红外图像处理系统中,由于图像数据量大,数据间相关性高,需要满足严格的实时性要求,因此需要对图像处理算法及程序进行基于数字信号处理器(DSP)的优化编程,从而大大提高算法的运行速度,来满足系统的实时性能。TI公司的C6x系列DSP[5],具有很高的运算速度和良好的优化结构,完全可以满足图像的实时处理要求。

3.1 算法结构的优化

算法结构的优化方法针对具体的处理算法具有特殊性,这部分的优化与DSP的结构没有关系,优化的目的是使算法本身具有良好的时间空间复杂度和简单的逻辑结构。如在图像处理中,通常要实现一个NX-N的二维数字滤波。在不做任何优化的情况下,得到一个结果要进行N2+l次内存读写,内存操作耗时长,需要占用专用的功能单元,因而成为功能提高的瓶颈。因此通常对该二维模板进行线形化,即先对源图进行一个N×1的一维滤波,再对中间结果图也进行N×1的一维滤波,从而得到最终的结果图。这样只需要进行 2(N+1)次内存读写操作就可以得到一个结果。当N比较大时(如11×11高斯平滑),程序的性能有明显提高。

3.2 DSP程序的结构优化

DSP的内部结构具有特殊性,如果程序的编写能够在一定程度上与DSP的结构相适应,利用C编译器的优化功能就可以在程序级的基础上大大提高算法的性能[4~8]。具体如下:

(1) 尽量使用int 类型中间变量

在图像处理程序中,数据通常为8bit的变量,而C6XDSP的内部寄存器和数据通道为32bit,在图像处理的滤波、卷积等过程中,需要较多的中间变量,如果采用8bit的中间变量存储方式,势必迫使编译器使用额外的数据调整指令,因此采用32bit的中间变量具有最好的效率。

(2) 使用移位代替除法运算

①DSP中的移位运算具有硬件支持,由一条指令完成,而除法运算使用程序实现,比较复杂耗时。

②DSP的浮点运算往往采用调用子函数方法,效率低,编译器无法进行软件流水优化,而采用移位运算可以代替一些定值的浮点运算,如:

for(I=0;I<1000;I++) for(I=0;I<1000;I++)

{ {

b+=35*0.325; b+=((35*333)>>10);

} }

以上两条程序完成同样的功能,但是第一条含有浮点数的乘法,运行时间为222 775;第二条只有定点数的乘法和移位运算,运行时间仅为881,可见效率差距非常大。

(3) 使用C6x内联函数

C6x编译器内部提供了许多指令,可以在单周期内完成许多复杂的函数功能,从而提高了代码的运行速度。如:

“饱和加法”:

int sadd(int a, int b)

{

int result;

result = a + b;

if (((a ^ b) & 0x80000000) == 0)

{

if ((result ^ a) & 0x80000000)

{

result = (a < 0) ? 0x80000000 : 0x7fffffff;

}

}

return (result);

}

这样一个复杂的算法可以用一条内联函数_sadd( a,b)实现。

(4) 使用32bit数据类型访问16bit数据

由于C6x系列DSP具有32位的寄存器和内部通道,在操作16bit的数据如short类型时,往往浪费一半的寄存器空间和通道带宽。为了充分利用这些资源,编译器设置了一些内联函数同时对两个16bit的数据进行操作,如_add2、_sub2。

short in1[]、 short in2[] 是两个short类型的数组,具有N项,以下是将两者对应项相加的操作。

for (i = 0; i < (N/2); i++)

_amem4(&sum[i]) = add2(_amem4_const(&in1[i]), _amem4_const(&in2[i]));

程序中,_amem4_const、_amem4将in1、in2和sum进行了32bit的对齐操作,然后同时进行两个short数据的加法运算和读取存储运算,从而提高了运算效率。

(5) 使用restrict关键字消除内存关联

为提高代码效率,C6x编译器总是尽可能多地安排指令并行,而指令能否并行取决于指令之间的相关性。对于编译器而言,内存读写指令之间是否独立是很难判断的,如下列程序:

void vecsum(short *sum, short *in1, short *in2, unsigned int N)

{

int i;

for (i = 0; i < N; i++)

sum[i] = in1[i] + in2[i];

}

程序中,sum的存储对于in1、in2的读取地址产生影响,只有等到sum存储完毕以后,才可以再次进行in1、in2的读取操作。这个问题叫做“别名问题”,因为sum可能和in1是一个地址,使其无法将读取数据和写结果的操作并行起来。

为了让编译器放心地将读取源数据和写结果数据两者并行操作,可以利用restrict变量申明当前数组名(或指针)是指向这段内存的惟一变量,如下列程序所示:

void vecsum(short *sum, short * restrict in1, short * restrict in2, unsigned int N)

{

int i;

for (i = 0; i < N; i++)

sum[i] = in1[i] + in2[i];

}

这样就可以消除以上的内存相关性,提高流水线效率。

(6) 软件流水优化

在程序的优化中,循环部分往往是最耗时的步骤,软件流水就是一种用来优化循环步骤的,使其循环内部的指令尽可能地并行执行。在C6201编译器中选择-o2或者-o3开关就可以打开编译器的软件流水优化功能。

形成软件流水的有效方法:在编译器选项中选定了-o2或者-o3选项,编译器就可以自动作出软件流水的优化。形成高效的软件流水,可以使用MUST_ITERATE给定循环变量信息和循环展开。形成软件流水应避免:①软件流水优化只在最内层循环进行。②循环体内部代码太多。③循环体内部代码太复杂。

在定点DSP中,浮点数的运算都是用子函数软件实现的,所以在定点DSP的程序循环中,如果由浮点数运算,就无法形成软件流水。解决的方法是手工进行浮点数的定标工作。对于已经确定操作数的浮点运算,如果运算结果可以是整数,就可以使用乘法加移位的方法实现乘除运算。如35×0.25可以转化成(35×1)>>2。

4 系统测试

本实验采用法国Sofradir中波热成像仪采集到的320×240像素6733帧8位真实红外对空序列图像,截取其中的100帧数据验证能量匹配滤波检测与数据关联跟踪算法的适用性。由于目标很远,此时的信噪比小于2,属于典型的强杂波环境下的弱小目标检测问题。实拍红外图像的显示如图6所示。

本文介绍的系统成功实现了弱小目标检测和跟踪程序的移植和优化。针对红外弱小目标检测和跟踪的实时测试表明:该系统实时和有效检测跟踪了每秒50帧,每帧320×240像素,每像素14位的低信噪比的复杂序列图像。

参考文献

[1] BRUNO M S, MOURA J F. Multiframe detector/tracker:optimal performance, IEEE Trans. AES, 2001,37(3):925.

[2] TZANNES A P, BROOKS D H. Point target detection in IR image sequences: A hypothesis testing approach based on target and clutter temporal profile modeling. Optical Engineering, 2000,38(2):2270-2278.

[3] TZANNES A P, BROOKS D H. Detecting small moving objects using temporal hypothesis testing. IEEE Trans.

AES, 2002,38(2):570-585.

[4] 田元,叶秀清.实时图像处理中的DSP优化编程,电子技术,2000,(10):43-46.

[5] Texas Instruments Incorporated.TMS320C6000 Programmer’s Guide, 2001.

[6] Texas Instruments Incorporated. TMS320C6000 optimizing compiler user’s guide, 2001.

[7] 徐盛. TMS320C6201数字信号处理器在图像处理中的应用.电子技术应用,1999,25(1).

[8] WAMES P. Hunt Engineering Incorporated. Developing a complex real time system with HERON and HEART Rev1.0. 2002.