摘要:电荷耦合器件(CCD)作为一种新型的光电器件,被广泛地应用于非接触测量。而CCD驱动设计是CCD应用的关键问题之一。为了克服早期CCD驱动电路体积大,设计周期长,调试困难等缺点,以线阵CCD图像传感器TCD1251UD为例,介绍一种利用可编程逻辑器件FPGA实现积分时阃和频率同时可调的线阵CCD驱动方法,使用Verilog语言对驱动电路方案进行了硬件描述,采用QuartusII对所设计的时序进行系统仿真。仿真结果表明,该驱动时序的设计方法是可行的。

关键词:线阵CCD;可编程逻辑器件;积分时间;频率

电荷耦合器件(CCD)作为新兴的固体成像器件——图像传感器,具有体积小、重量轻、分辨力高、噪声低、自扫描、工作速度快、灵敏度高、可靠性好等优点,受到人们的高度重视,广泛应用于图像传感、景物识别、非接触无损检测、文件扫描等领域。其应用系统的关键技术在于CCD驱动信号的产生及输出信号的处理。以往经常采用的驱动方法主要偏重硬件的实现,调试困难,灵活性较差。而单片机驱动方法虽编程灵活,但存在资源浪费较多、频率较低的缺陷。复杂可编程逻辑器件FPGA具有编程灵活、集成度高、速度快、容量大、功耗小、可靠性好等优点,并且节省PCB板的空间,可移植性好,使用灵活。因此,结合实际应用需要,设计了基于复杂可编程逻辑器件FPGA的CCD驱动时序设计,使用Verilog语言对驱动电路方案进行了硬件描述,采用QpartusⅡ对所设计的时序进行了系统仿真。

1 CCD图像传感器TCD1251UD

TCD1251UD芯片是日本东芝公司生产的一种高灵敏度、低暗电流、具有2 700个有效像元的双沟道两相线阵CCD图像传感器。它的中心距为11μm,最佳工作频率为1 MHz,光敏单元阵列总长为29.7 mm。该传感器可用于传真、图像扫描和OCR。它的结构包括:MOS电容存储栅、转移栅电极SH、CCD模拟移位寄存器φ1和φ2信号输出单元OS和补偿输出单元DOS。

2 TCD1251UD的驱动时序要求

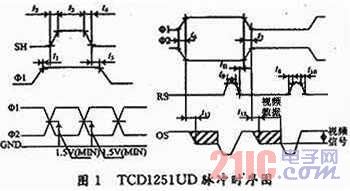

TCD1251UD的驱动脉冲波形图如图1所示,各信号之间定时关系如表1所示。

当SH脉冲为高电平时φ1脉冲亦为高电平,其下均形成深势阱,SH的深势阱使φ1电极下的深势阱与MOS电容存储势阱沟通,从而使MOS电容存储栅中的信号电荷转移到φ1电极下的势阱中。当SH电平由高变低时,SH低电平形成的浅势阱将MOS电容存储栅下的势阱与φ1电极下的势阱隔离开。存储栅的势阱进入光积分状态,而模拟移位寄存器将在φ1和φ2脉冲的作用下驱动信号电荷向左转移,最后信号经由OS端输出哑元信号和2 700个有效像元信号,而由DOS端输出补偿信号。由于结构的安排,OS端首先输出13个虚设单元信号;再输出51个暗信号;最后连续输出2 700个有效像素单元信号;接着输出9个暗信号、2个奇偶检测信号和没有信号的空驱动,空驱动的数目为任意的,但必须大于0,否则会影响下一行信号的输出。由于该器件是两行奇、偶传输,所以在一个SH周期中至少要有1 388个φ1脉冲,即TφSH>1 388Tφ1。CCD各路脉冲的技术指标为:φ1,φ2为驱动脉冲,φ1,φ2相位相反,两者均是频率为0.5~2 MHz,占空比为1:2的方波,本文要求该频率可调节。SH为转移脉冲,由图1可以看出:当SH为高电平时必须φ1同步为高电平。当SH为低电平时,φ1也将变为低电平。但是,φ1脉冲必须比SH脉冲提前上升、迟后下降。即在并行转移时φ1脉冲有一个大于SH为高电平时的持续时间的宽的高电平脉冲。由上面分析可以得出,TφSH>1388Tφ1,RS为复位脉冲,占空比为1:4的方波,频率为1~4 MHz,同时要求该频率同样可调节。

3 驱动时序的实现

3.1 驱动时序的FPGA实现

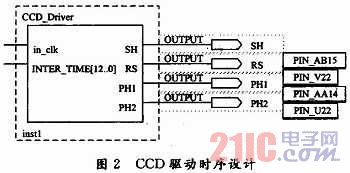

为了产生系统中用到的时序,设计了基于复杂可编程逻辑器件FPGA的CCD传感器驱动时序发生器,采用Altera公司的QuartusⅡ软件开发系统。QuartusⅡ软件开发系统是一种全集成化的可编程逻辑设计环境,它支持硬件描述语言(VHDL和Verilog HDL)、状态图和原理图三种输入方式,拥有编译、逻辑综合、仿真等功能。相对于其他输入方式,硬件编程语言的输入方式(如VHDL或VerilogHDL)可移植性和可读性好,因此成为本设计的首选。其中Verilog HDL具有编程灵活、使用方便等优点为众多设计所接受。总体的设计思想是将驱动时序分成三个模块,分别为AD0832,Divider和CCD_Driver。AD0832模块采集输出数据由Divider分频模块处理后输入给CCD_Driver模块去调节CCD的积分时间与驱动频率,同时CCD_Driver模块输出4路信号驱动CCD。CCD_Driver模块的的总体设计思想是将可调时钟in_clk、积分时间INTER_TIME作为输入而且它们与Dirider模块的输出CCD_clk、Ctr_Time_Out[12..0]对应,产生四路信号SH,RS,PH1,PH2作为输出直接驱动CCD。其中驱动频率RS和积分时间SH可调。CCD驱动时序的设计如图2所示。CCD_Driver模块实现的功能是将时钟输入(in_clk)二分频分别得到Q1和Q2信号,四分频得到temp_ph。用信号temp_ph作为计数时钟输入,分别在它的上升沿和下降沿触发产生信号temp_sh1,temp_sh2。将Q1,Q2,temp_ph,temp_sh1,temp_sh2进行组合逻辑运算分别得到转移脉冲SH、复位脉冲RS、时钟信号PH1,PH2。其中转移脉冲SH、复位脉冲RS频率可调。使用VerilogHDL编写程序中要求时钟PH2与PH1信号相位相反。Q1为在时钟in_clk的上升沿触发的二分频信号,Q2为在时钟in_clk的下降沿触发的二分频信号。把Q2取反后与Q1相与产生RS信号。由于SH,RS,PH1,PH2信号存在一定的周期关系,所以在Q1下降沿时触发翻转二分频得到基信号temp_ph。用信号temp_ph作为计数时钟输入,分别在它的上升沿和下降沿触发并根据积分时间计数控制temp_sh1,temp_sh2的高低电平时间。将temp_sh1,temp_sh2相与得到SH信号;将temp_ph,temp_sh1与temp_sh2相或得到PH1信号。PH1取反得到PH2信号。

3.2 仿真结果

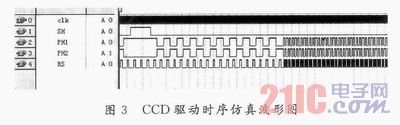

以上模块在QuartusⅡ软件开发系统上进行设计输入,经编译、校验后,其仿真波形如图3所示。

从仿真结果可看到产生的驱动脉冲与线阵CCD-CCD-TCD1251UD所需要的驱动时序完全吻合,能够达到CCD驱动电路要求。

4 结语

使用FPGA器件实现对CCD驱动器的设计,很好的满足了CCD应用向高速、小型化、智能化发展的需求。在设计中,首先必须清楚CCD驱动时序的要求,并利用硬件描述语言进行科学的编程,这样才能有效地完成设计需求。本文通过一个设计实例,来说明利用FPGA设计CCD驱动器的方法,经过仿真测试,验证了该设计满足CCD驱动要求。