1 电路系统设计

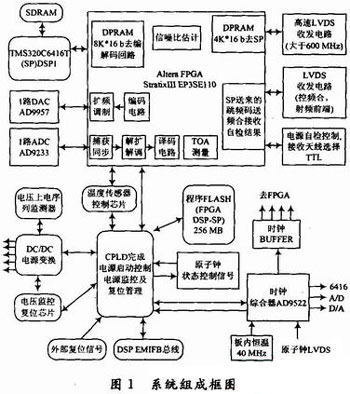

数字中频调制解调系统以Ahera公司的FPGAEP3SE110为核心,来实现中频调制解调系统中MSK数字调制解调、扩频解扩、信噪比估计和RS编译码等数字信号处理功能。并在其外围加上TMS320C6416 DSP协处理器完成与信息处理器的信息处理和扩跳频图样管理,采用AD9233完成模拟中频到数字信号的转换,采用AD9957将调制后的MSK数字信号转换成70MHz的模拟中频,系统总体框图如图1所示。

1.1 TMS320C6416的内部结构

在本系统中,采用了一片TMS320C6416A8作为协处理器,处理外界接收到的各种通信消息,完成格式的转换、信息预处理、端机运行控制,扩跳频图样计算与管理等功能。TMS320C6416是TI公司推出的TMS320C6000系列中的定点的高速DSP芯片,它采用超长指令字体系结构,CPU时钟频率最高可达到1GHz时,其运算能力最高支持8条指令并行执行,定点处理能力最高可达8GIPS。它有64个相互独立增强的可编程E-DMA通道,可独立于CPU进行工作,以CPU时钟速率进行数据吞吐。DSP在上电时根据相应管脚的状态确定Boot模式、工作频率。TMS320C6416有三种上电自举方式:No Boot引导、HPI引导与ROM引导。DSP在复位时检测BEA[19:18]引脚电平状态来确定采用何种Boot模。TMS320C6416T的PLL系数选择由引脚CLKMODE1和CLKMODE0决定,复位时系统检测这两个引脚的状态,根据这两个引脚的状态,决定选择不同的PLL系数,有BY-PASS方式、×6方式、×12方式、×20方式。本板选用40MHz的外部晶振时钟输入,PLL的倍频系数设为20倍,CPU的系统时钟运行在800MHz。

1.2 外部存储器

1.2.1 EMIFA与SDRAM的接口

TMS320C6416片内有1MB的内部RAM存储器,而用于通信消息格式转换的程序需要500KB的存储空间,还需要1MB的数据存储空间,其片内存储器不能满足以上程序运行和数据处理的需要,因此电路系统扩展了大容量的SDRAM以存放相关的数据以及程序。

基于以上需求,DSP外部SDRAM采用1片Micron的MT48LC8M3282 8M×32映射到EMIFA总线的CE0外部存储空间。Micron的MT48LC8M3282是86-pin TSOP的CMOS同步DRAM,最高工作频率(处理速度)为166MHz(5.5ns)。SDRAM设备时钟始终控制在CPU时钟速率的1/6,即当CPU芯片以800MHz运行时,SDRAM以133MHz运行。

1.2.2 EMIFB与程序FLASH的接口

FLASH存储器是在EPROM和E2PROM的基础上发展起来的一种非易失性存储器,在掉电情况下仍能保证数据不丢失,并能够在线实施擦除和再编程操作。在TMS320C6416的应用程序的开发中,程序代码或数据表是要保存在FLASH或其他非易失存储器中,以保证掉电时代码仍在,程序在加电复位后自动运行。TMS320C6416的EMIFB通过异步接口可以支持8位FLASH配置。要实现TI公司TMS320C6416的外部ROM自举,8b的ROM/FLASH存储器必须配置在TMS320C6416的EMIFB总线上的CE1空间。本系统使用的程序FLASH芯片为Spansion公司S29GL256P,该FLASH芯片是一种存储量32M×8b的闪速存储器,存取时间为90ns,能够在线擦除,并能在大多数标准的微处理器总线上通过特殊的编码命令序列编程。为了方便以后FPGA和DSP程序的远端动态更新,本系统采用了FPGA和DSP共享FLASH的方式,当DSP收到上位机更新程序的命令后,通过更新FLASH中相应段的内容,来更新相应FPGA或DSP程序。

1.2.3 EMIFA与FPGA双口RAM的接口

在本系统中,为了实现并行处理,需要实现DSP与FPGA之间的数据通信,考虑到数据交换的处理速度和软件编译的难易程度,本系统采用FPGA内建双口RAM的方式实现这一功能,具体的实现方式采用中断方式,当DSP收到上位机通过高速LVDS传来的下时隙发送数据命令后,将下一时隙要发射的数据和计算好的扩跳频图样,放到与FPGA通信的发射数据单元双口RAM内,向FPGA内控制模块双口RAM写中断命令,FPGA收到中断后,跟据内部的时隙控制信号,完成RS编码,MSK数字调制,频合控制,将基带调制数据送给AD9957,产生70MHz模拟调制信号,送给上变频单元。当DSP收到上位机传来的下时隙接收数据命令后,将下一时隙伪码和跳频图样计算好后,通知FPGA,FPGA根据AD9233采样信号进行同步捕获、解扩、解跳、译码,将解调译码后的信息送到与DSP通信的接收数据单元双口RAM后,给DSP产成中断信号,这个中断信号使DSP完成一次EDMA传输,EDMA传输完成后,DSP发出中断清除命令,并将接收到的信息报给上位机,从而完成一次完整的数据发送和接收。

1.3 FPGA模块

本系统中采用了Altera公司的StrixⅢ系列EP3SE110作为核心处理器,完成了数字中频MSK调制解调、RS编译码、CRC校验码、信号信噪比估计、频合控制、收发通道自检控制、收发延时测量、TOA测量、各种时隙信号产生和对外600 MHz高速LVDS串行通信等功能。StrixⅢ系列FPGA是Altera公司具有全新构架的高密度产品。它采用65 mm工艺,与StratixⅡ相比,器件的逻辑密度是前者的2倍,功耗降低了50%,性能提高了25%。本设计采用的EP3SE110芯片,片上LVDS总线最高速率可以达到1.25 Gb/s,该芯片集成有106 500 LE,896个18×18乘法器,16个全局时钟网络,88个等效LVDS通道,片上RAM达到9 Mb的容量。FPGA的加载方式采用FPP方式,加载时序控制由CPLD来完成。600 MHz高速LVDS采用FPGA内部的SERDES来完成,为保证数据高效可靠的传输,数据传输采用8b10b编码。

1.4 D/A模块

D/A采用AD9957。AD9957是具有18位I,Q数据通路和14位DAC的1GSPS正交数字上变频器。它在单片上集成了高速直接数字频率合成器(DDS)、高速14位数模转换器、时钟乘法器电路、数字滤波器以及其他DSP功能。AD9957有3种工作模式:正交调制模式、单频输出模式、插值DAC模式。

本系统中MSK调制方式采用正交调制,AD9957在正交调制模式下主要设置的工作参数有时钟倍频、频率控制字、内插因子、D/A输出增益控制等。时钟倍频:AD9957的系统时钟频率=输入时钟频率×倍频。系统的载波是由DDS提供的,其工作时钟等于系统时钝。根据抽样与恢复定理,DDS的工作时钟至少要两倍于载波频率,才有可能产生完整的载波信号。一般情况下,为使DDS产生的载波更为稳定,其频率要小于系统时钟的40%。为了保证输出信号的频谱质量,本板的800MHz系统时钟直接由时钟综合器产生。AD9957内部锁相环采用旁路方式,内插滤波器系数设为5,产生与外部基带调制数据同步的80MHz时钟PDCLK。

1.5 A/D模块

A/D部分的设计采用ADI公司的AD9233和差分放大器AD8352配合使用,进来的70MHz模拟中频信号先经过AD8352放大后再送给AD9233进行处理,AD9233可以在70MHz输入频率下提供85dBc的SFDR性能,通过SPI或硬件连接,采样后的数据可以输出为二进制补码、偏移码和格雷玛。ADI公司的AD8352低失真放大器可以用于单端转差分输入,来缓冲和与多种12b,14b和16b的高速模数转换器接口。AD8352可以在频率为180MHz时达到一个高达80dB的无杂散动态范围,差分放大器的增益范围在0~24dB之间,可以按照单晶体管要求进行调节。

1.6 CPLD模块

CPLD采用Altera公司的MAXⅡ系列的EPM2210F324来实现系统电源上电顺序控制电压监测、软件看门狗、时钟综合器的配置和FPGA与DSP的程序加载等功能。具体实现如下:系统上电时根据系统电源上电要求,控制电源模块加电使能端来控制上电顺序。通过电压监测芯片,对系统电压异常进行监测,根据异常情况进行系统复位或切断电源。通过内建计数器,实现软件看门狗功能,软件看门狗可以通过DSP使能打开或关闭,以方便系统调试。系统正常上电后通过SPI配置时钟综合器,产生系统所需的时钟。时钟配置完成后,CPLD控制FPGA采用FPP方式从FL-ASH中加载程序,当FPGA加载成功后,根据FPGA的配置引脚CONFIGDONE状态,将FLASH控制权交给DSP,控制DSP完成程序的加载。

1.7 时钟和电源模块

实现数字中频调制解调系统的时钟电路设计如下:板内40MHz恒温晶振与外部供给的10MHz原子钟通过时钟综合器ADI公司的AD9522做双时钟切换、主备时钟备份,CPLD根据需要配置时钟综合器生成DSP与FPGA的40MHz工作时钟、AD9233的40MHz或80MHz采样时钟、AD9957的800MHz输入时钟。电源采用凌特公司的LTM4600产生FPGA和DSP的I/O电压3.3V和FPGA的核电压1.1V,采用凌特公司的LT1764产生FPGA的2.5V电压,采用TI公司的TPS54310产生DSP的核电压1.2V,用凌特公司的LT1764产生AD9233的模拟电源1.8V和AD9957的模拟电压3.3V。

2 软件设计

2.1 MSK数字扩频调制

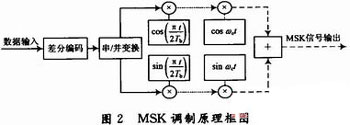

根据理论分析,MSK可以看作是具有正弦加权的OQPSK,系统采用具有正弦加权的OQPSK的调制方案,原理框图如图2所示。

![]()

在硬件电路实现时,MSK基带调制(图中实线部分)在FPGA中实现,当接收到系统的发送允许St_TCLK时,启动MSK基带调制,从RAM中读取发送信息数据,从低位开始进行差分编码、根据消息和伪码进行伪随机扩频,将扩频后的数据进行串并变换、正余弦加权运算,之后将正余弦加权后数据送给D/A处理。中频调制(图中虚线部分)采用AD公司的带D/A转换的正交数字上变频器AD9957完成,AD9957可以实现数据的内插滤波、正交上变频、D/A转换输出等功能,本系统设置中频频率为70MHz。

由于基带MSK调制就是对并行的两路数据进行正弦加权,即每个比特对应于周期为fb/4的半个的正弦波形,根据0/1选择不同的相位,因此在具体实现中,可以采用查找表的方法,根据内插系数先产生半个波长的正弦波信号数据进行存储,在调制时根据数据选择输出不同相位的半个周期正弦波形。

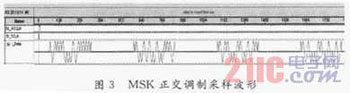

图3表示的是在板运行时,在QuartusⅡ的在线逻辑分析仪SignalTap上采集的MSK基带调制波形,其中Ldata为I路调制数据。

2.2 MSK数字解扩解调

本板的信息解调采用解扩解调一次完成的方案:即在系统完成捕获和同步的情况下,利用扩频码的相关性,通过相关运算,解出信息,因此系统接收方案就归结为如何对相关峰进行捕获的问题。

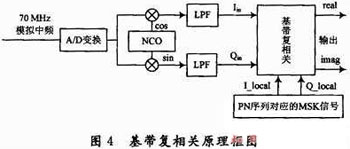

由于本系统的信号带宽为5MHz,因此可以根据欠采样理论,对70MHz模拟中频信号进行40MHz欠采样;根据数字信号处理理论,对70MHz模拟中频信号进行40MHz采样,相当于一次下变频,将频谱搬移到10MHz的载频上,通过本地的10MHz的NCO,对采样后的信号进行数字正交下变频,采用低通滤波器,滤掉高次谐波分量,变为基带信号后,在与本地的PN码所对应的MSK基带信号进行基带复相关运算,运算后的实部与虚部的模值就是最大相关峰值。基带复相关原理框图如图4所示。

图5为根据基带复相关原理,在板运行时解出的相关峰,根据实际测试结果,该方法完全可以满足系统的指标要求,并具备一定的抗多径和多普勒频偏的能力。

3 结论

通过采用DSP+FPGA的方案构建的中频调制解调系统能够更好地完成中频调制、解调、编译码、扩频解扩和消息预处理等功能。将对时序要求严格的算法放到FPGA中实现,系统控制和消息预处理由DSP来完成,这样使得系统调试更加方便。通过该系统还可以实现QPSK。16QAM等其他多种调制方式,通过DSP对FPGA的不同配置,实现信号不同调制解调方式的切换,来实现中频意义上的软件无线电。