0 引言

在现代电子技术应用领域,A/D转换器是模拟信号转换数字信号的中介,数据采集系统中,一般由单片机或其他微控制器对高精度A/D转换器进行控制,通常采用软件模拟A/D转换器时序的方法,增加了CPU的负担,降低了CPU的工作效率,现场可编程门阵列FPGA" title="FPGA">FPGA(Field Programmable GateArray)的高集成度和高速特性,使之相对于单片机和微控制器更适合用于高速A/D器件的采样控制。另外,在电磁干扰较大的环境中,单片机会出现程序跑飞的问题,在利用看门狗复位的过程中,对采集的数据流而言,会存在数据的丢失问题。相对的,触发沿或电平控制的FPGA,通过设计可靠的驱动,系统采集数据更为可靠。

本文是以一个3通道低频小型数据记录仪" title="数据记录仪">数据记录仪为研究背景,设计了以Actel公司FPGA为控制器的系统,对串行输出A/D转换器ADS8341进行控制,提高了系统集成度和稳定性。

1 ADS8341功能介绍

ADS8341是Burr Brown公司推出的一款低功耗,高性能的4通道,16位A/D转换器,其串行接口降低了系统开发的成本,SSOP-16的小体积封装适合微型设备使用。

1.1 ADS8341的功能

CH0~CH3:4个通道为模拟输入端,可以设置为单通道输入方式,也可以构成CH0-CH1,CH2-CH3,两组差分输入。

![]() :引脚低电平有效,A/D转换器进入低功耗模式。

:引脚低电平有效,A/D转换器进入低功耗模式。

Vref:参考电压输入端。

DCLK:系统的外部时钟输入端,最高输入为2.4 MHz,此时芯片A/D转换速度达到最大值,为100 ksa/s。

![]() :A/D转换器的片选端,低电平有效,高电平时其他引脚呈高阻态。

:A/D转换器的片选端,低电平有效,高电平时其他引脚呈高阻态。

DIN:串行数据输入端,片选信号有效时,在DCLK的上升沿,串行数据按位输入A/D。

DOUT:串行数据输出端,片选信号有效时,在DCLK的下降沿,将A/D转换后的数字信号按位输出。

BUSY:片选有效时,A/D转换器输出一个时钟周期高电平信号。

Vcc和GND引脚分别为电源和数字接地端。

1.2 ADS8341的控制宇及转换时序

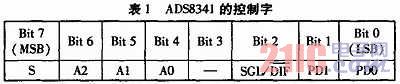

ADS8341的控制字如表1所示:

ADS8341的控制字为8位,S为起始标志位,A2,A1,A0控制通道选择,可以提供单通道或差分输入方式不同通道选择。*****高电平为单通道输入方式,PD1,PD0为电源控制模式位,若为“11”,电源始终处于开启模式。

ADS8341转换的基本时序如图1所示。

由图1可以看出,ADS8341完成一次转换需要24个DCLK时钟,其中在前8个时钟的上升沿,DIN控制字输入,控制字输入完成后,在DCLK的上升沿时刻,BUSY信号输出一个高电平,在这个时钟的下降沿,转换数据按位输出。经过一次完整的转换后,在第25个时钟上升沿,DIN可以再次输入控制字高位,保证了当DCLK外部时钟取得最高频率2.4 MHz时,A/D转换器的频率达到最高100 ksa/s。

2 基于FPGA的ADS8341控制器设计

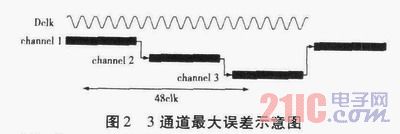

本记录仪系统记录采集信号的频率范围500Hz以下,在系统实际应用中,对被测信号采用过采样方式,采样频率为被采集信号频率的5~10倍。系统采用A/D转换器3通道快速循环采样,近似实现了通道同步采样" title="同步采样">同步采样,是一种准同步采样的方式。经过72个DCLK周期,实现了CH0~CH2通道的顺序切换,当A/D转换器以最大采样频率100 ksa/s工作时,记录仪系统采样的频率相当于单通道频率的1/3,通道1与通道3之间同步误差最大为48clk,如图2所示,最小误差时间约为![]() (此时采样频率最快),满足系统对较低频率信号采集的要求。

(此时采样频率最快),满足系统对较低频率信号采集的要求。

系统采用了基于FLASH架构的Actel公司ProASIC3" title="ProASIC3">ProASIC3系列A3P100" title="A3P100">A3P100,使用Libero" title="Libero">Libero集成开发环境,FPGA的A/D控制模块主要包含以下功能:

●时钟控制器

记录仪系统FPGA的外部时钟频率为48 MPa,对系统时钟20分频得到时钟DCLK即可提供A/D转换器的最大工作时钟。另外通过逻辑控制,时钟控制器提供几个低于2.4 MHz的时钟频率,系统可以选择更低的采样频率。

●不等占空比时钟

本系统设计A/D控制模块中引入clk_div时钟信号,占空比为2:3,做为din的控制电平,当clk_div信号为低电平时,din输出数据,clk _div信号为高电平,din为低电平。

clk_div撑(.duty_factor(duty_factorl),counter_top(counterl)).div_clkl(.reset(clk1_reset),.clk_in(clk_in1),clk_out(clk_out1));//任意占空比分频时钟模块调用

●控制字状态机

记录仪上电以后的工作状态为3个通道循环采样,控制字状态发生器循环生成chO=“1001_1111”,ch1=“101_1111”,ch2=“1010_111 1”,并将控制字转换成串行数据从din引脚输出,实现A/D转换器通道切换。

●控制字并行转串行模块

控制字chO,ch1,ch2需要转化成串行数据,通过din输入至AD,控制通道选择,循环输入控制字则循环选择3通道。将状态控制字ch0、ch1、ch2传输至寄存器,在DCLK时钟下降沿,提取第7位(高位),此时数据比较稳定,然后寄存器向左位移。在DCLK时钟上升沿传输至AD,实现控制目的。

●信号采集模块

A/D转换器采集数据串行输入FPGA后,转换成并行数据,传输至系统的数据总线。根据A/D转换器采样的基本时序可知,在dout引脚串行输出数据时,din引脚应保持低电平,为了3个采样通道近似同步数据采集,在经过24个DCLK时钟周期,对一个通道数据采集转换输出完成后,要在DCLK的第25个时钟的上升沿,进入第二个通道的采集和转换。最终实现记录仪在72个DCLK时钟周期的状态循环时序是A/D模块控制的关键。

3 计算机仿真分析与系统实现

系统FPGA使用Actel公司基于FLASH结构单元的芯片,进一步的降低了系统的功耗,缩小了系统的体积,Actel FPGA的集成开发环境Libero集成了仿真工具modelsim。以AD最高采样频率为例试验,仿真时序波形如图4。

A/D控制模块中,在“clk_div”高电平时,实现寄存器“shuru”至寄存器“A”的数据传递,在“clk_div”低电平实现并行数据到串行数据的转换,并通过“din"输出,图4中显示了“din"输出引脚3个控制字状态的变化。

示波器显示din引脚控制字串行输出三组控制字的循环变化,如图5。

4 结论

系统运用FPGA电平控制多通道A/D转换器不同通道的选通,相比较单片机而言,更为稳定可靠,采集数据流完整,使用基于FLASH架构的Actel公司FPGA进一步降低了微型数据记录仪系统的功耗,同时提高了系统在电磁干扰较强环境的稳定性。