CCD是利用光电转换原理把图像信号转换为电信号,即把一幅按空间域分布的光学图像,转换成为一串按时间域分布的视频信号的半导体元器件。因其具有体积小、重量轻、功耗低、灵敏度高、工作稳定、寿命长、自扫描和便于同计算机接口等优点,被广泛应用于图像传感和非接触式测量。CCD应用的关键问题之一,是驱动时序发生器设计。它直接关系到CCD的信号处理能力、转换效率和信噪比等光电转换特征。针对Sony公司面阵CCD ICX098BQ的工作原理和驱动时序的要求,给出了驱动时序发生器的具体设计,使用VHDL语言对驱动时序发生器的实现方案进行了硬件描述,采用Quartus II 8.0对所设计的时序发生器进行了功能仿真,在该驱动时序发生器作用下,对Sony公司ICX98BQ面阵CCD产生的输出信号波形进行了验证。

1 CCD成像系统

CCD成像系统如图1所示,目标通过光学系统成像在CCD上。在偏置电压和驱动脉冲的作用下,CCD完成光电荷的转移、存贮等工作,将光信号转换成具有直流分量的模拟电信号。形成的模拟电信号经过信号处理器,进行除噪、增益和模数转换后,将数据传输到显示器或计算机上,进行后期处理。在上述系统中,CCD信号采集模块是关键。对此,主要对CCD信号采集进行分析。

2 面阵CCD图像传感器驱动时序分析

2.1 Sony ICX098BQ型面阵CCD

ICX098BQ是Sony公司生产的一款1/4英寸(0.635cm),具有可变电子快门的行间转移型彩色面阵CCD芯片,芯片结构如图2所示。该芯片灵敏度高,暗电流小,具有较好的抗弥散功能。

ICX098BQ芯片由感光阵列、垂直移位寄存器、水平移位寄存器和输出放大器4个主要部分组成。要使该CCD芯片正常工作,需要8路驱动时钟来驱动。分别为4路垂直转移时钟Vφ1、Vφ2A、Vφ2B、Vφ3,控制垂直移位寄存器中的电荷信号向水平移位寄存器移动,其中当Vφ2A和Vφ2B为+15V高电平时作为读出转移时钟,将感光阵列的信号电荷转移到垂直移位寄存器中;两路水平转移时钟Hφ1、Hφ2,控制水平移位寄存器中的电荷信号向前迁移;复位门时钟RG,使水平移位寄存器中的电荷信号顺利输出,其频率为10MHz,直接决定CCD电荷信号的水平输出频率并控制曝光量的电子快门时钟φSUB。

上述驱动信号均由CCD驱动时序发生器产生。由于面阵CCD的驱动信号数量多,相位要求严格,且需要多种电压的驱动,因此进行时序分析并设计出高精度的驱动时序电路是问题的关键。

2.2 驱动时序分析

ICX098BQ芯片的一个工作周期分为4个阶段:感光阶段、垂直转移阶段、帧转移阶段和水平读出阶段。感光阶段进行光电转换,完成感光阵列的电荷积累。垂直转移阶段实现感光阵列积累的电荷包读出转移到相邻的垂直移位寄存器。帧转移和水平读出阶段包括电荷包从垂直移位寄存器向水平移位寄存器并行转移以及从水平移位寄存器向输出放大器的串行输出。

在CCD工作周期中,首先在Vφ1、Vφ2A、Vφ2B、Vφ3的控制下,感光阵列的垂直移位寄存器进行一次电荷转移,将之前残留下来的电荷彻底清除,为下一步做好准备。然后垂直驱动时钟V1将持续一段高电平。此刻,读出时钟V2A、V2B跳变为+15V的高电平窄脉冲,读出时钟迅速将感光阵列中的所有像素电荷并行地转移到相邻的垂直移位寄存器中。在每个行消隐期间,垂直移位寄存器中的电荷在四相垂直驱动时钟Vφ1、Vφ2A、Vφ2B、Vφ3交替作用下逐行地向水平寄存器转移。此时水平驱动时钟Hφ、Hφ2保持不变。在行正程期间,转移到水平寄存器的一行信号电荷受频率为10MHz的两相水平驱动时钟Hφ1、Hφ2控制,向浮置扩散放大器水平转移。输出放大器以复位门时钟RG的频率将像素电荷逐一转换成信号电压后串行输出,在输出端得到与光学图像对应的一行的视频信号。

3 基于VHDL的时序发生器设计

由于面阵CCD驱动时序的复杂性,选用硬件描述语言VHDL设计CCD时序。VHDL采用自顶向下的设计方式,具有较强的硬件描述能力和仿真能力。在程序中,定义的输入输出端包括两个输入端和10个输出端。

整个驱动时序发生器的实现程序为两重嵌套的循环,整个过程采用3段式状态机来完成。一个CCD工作周期流程如下:

(1)对水平寄存器进行清空复位。

(2)垂直转移,将电荷从感光区转移到相邻的垂直移位寄存器。

(3)进行帧转移和水平读出阶段。帧转移一行,水平读出一行,直到整帧读出完毕。

(4)返回,读取下一帧。即返回步骤(1)。

状态转移图如图3所示。

IDLE:为空闲状态;当积分启动后,转到状态1。

状态1:为预读出状态;读出水平寄存器内的电荷,当水平读出700个电荷后,转向状态2,否则,自循环。

状态2:为垂直转移状态;使感光区的电荷转移到垂直移位寄存器,垂直转移后,转到状态3。

状态3:帧转移状态;其中Flag为场有效标志,当Flag=1时,进入积分状态,开始下一帧的工作。

状态4:水平读出状态。

状态5:积分状态,转向空闲状态,开始下一帧的工作。

根据分析,设计出产生上述时序的顶层原理图,如图4所示。

在CCD时序发生器模块中,输入为时钟和复位信号,以及两路同步信号VD和HD;输出除了CCD驱动所需的10路信号外,还包括SHP和SHD两路用于相关双采样的电路以及暗像元、哑像元驱动时序。

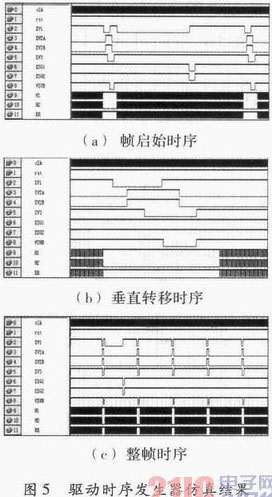

在对VHDL语言描述的时序发生器进行编译后,对驱动时序发生器进行功能仿真,仿真结果如图5所示。

通过对FPGA芯片程序的下载。将功能模块集成于CycloneII系列芯片EP2C8T144C8N中。该时序发生器顶层模块程序资源占用率仅为3%。

4 硬件实现以及测试结果

CCD信号采集驱动电路硬件部分主要分为两个部分,即CCD驱动电路和偏置电压的设计。

4.1 偏置电压电路

对ICX098BQ的数据手册进行分析,Hφ1、Hφ2水平移位驱动工作电压峰峰值为3.3V,分别为-3.3~0V和0~3.3V,Vφ1、Vφ3垂直转移工作电压为5.5 V(-5.5~0 V),Vφ2A、Vφ2B为三电平,工作电压为(-5.5V、0V、+15V)。因而需要-5.5V和+15V作为CCD垂直驱动时序的工作电压。偏置电压+15V和-5.5V采用Linear公司生产的LDOLT3487获得,偏置电压产生电路如图6所示。

LT3487是一款单芯片稳压器,可以在单输入电压(2.3~16 V)基础上,获得正负电压。与其他同类型稳压器相比,其输出断开功能可避免在器件关闭期间出现直流漏电所导致的功率损耗。文中输入电压值为+5V,通过USB接口从电脑得到,其供电能力完全能够满足驱动及CCD电路的电流消耗。

4.2 驱动器电路

如图7所示,CCD工作所需的驱动时序均由CycloneII系列器件EP2C8T144C8N产生。在CCD工作所需的4路垂直驱动时钟Vφ1、Vφ3、Vφ2A、Vφ2B中,Vφ1、Vφ3为两电平,Vφ2A、Vφ2B为三电平。而FPGA产生的信号只有‘0’和‘1’两种状态。对此,可将时序发生器中的XV2和XV3时序分别与XSG1和XSG2时序利用脉冲合成驱动器CXD1267AN进行合成来生成Vφ2A、Vφ2B。

如图7所示,在FPGA产生的时序发生器的10路信号中,XV1、XV2、XSG1、XV3、XSG2、XV4经过脉冲合成驱动器CXD1267AN后,合成为Vφ1、Vφ2A、Vφ2B、Vφ3;而H1、H2和复位脉冲RR通过ACT04反相器后进入CCD进行工作,提升了H1、H2和RG的驱动电压,增加了CCD的水平读出能力。驱动电路在-5.5V和+15V的电压下工作。在电压偏置电路和驱动电路的工作下,产生的CCD信号为包含直流分量大小为几百mV的交流信号。

4.3 硬件测试结果

物体的图像经过光学镜头投射到面阵CCD上,并将上文实现的驱动时序用于面阵CCD的驱动,并用示波器对隔直后的CCD信号进行测量。

图8为CCD输出的某一行中各感光像元电荷信号的波形,每个周期代表一个像元。每个像素单元分为3部分,它们分别是复位脉冲馈入、参考电平和数据电平。每个周期中的尖峰为复位脉冲馈入到CCD的读出电容,在CCD输出波形中形成,每个像素感受到光信号的有效值由参考电平和数据电平的差表示。由此可见,在驱动时序作用下面阵CCD能正常工作。

5 结束语

时序控制方案采用VHDL语言进行设计,用EDA软件对所设计的驱动电路进行了仿真。仿真结果表明,该驱动电路能够满足面阵CCD驱动时序的求。