1 FIR滤波器的基本原理

一个L阶的FIR数字滤波器的基本系统函数见式(1):

![]()

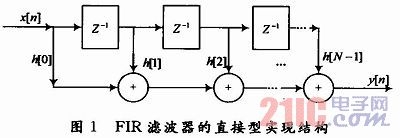

式中:h(n)表示滤波器的系数;x(i)表示带有时间延迟的输入序列,此表达式对应的直接型实现结构可用图1来表示。

可以看出,FIR滤波器是由一个“抽头延迟线”加法器和乘法器的集合构成的。传给每个乘法器的操作数就是一个FIR系数。对每次采样x(n)要进行N次连续的乘法和(N-1)次加法操作,因实际中滤波器的阶数都很高,实现高数据吞吐率就需要很多的硬件乘法器,硬件实现时将占用大量的资源,同时也会因此影响滤波器的速度和性能。为了解决这个问题,人们从多个角度寻求优化方法。从数字滤波器表达式看,对它

的优化操作,实际最终转换成两类改进。一类是针对输入xi的DA操作的改进;另一类是针对系数hi编码的操作。

2 DA算法

分布式算法(Distributed Arithmetic,DA)是为了解决乘法资源问题而提出的经典优化算法这种算法结构,可以有效地将乘法运算转换成基于查找表LUT(Look Up Table)的加法运算,利用查表方法快速得到部分积。

对于低阶而言,由于LUT表地址空间较小,与传统算法相比,分布式算法可极大地减少硬件电路的规模,提高电路的执行速度。然而当FIR滤波器阶数很高时,作为查找表的ROM将很大。阶数每增加1位,ROM容量就增加1倍,这种以2的幂次递增的资源占用是硬件资源不可接受的。因而在滤波器系数较高时,为了减小查找表的规模,常采用一定的方法将大LUT分割为一些小的LUT的方法。如滤波器的多相分解结构、多路复用器和加法器替代查找表的算法等。

3 CSD编码算法

常数乘法可以通过“移位-加”来完成,而乘数中“1”的个数决定了“加”操作的次数,当然“1”的个数越少越好,正则有符号数字量CSD(Canonic Signed Digit)编码就可以实现“1”的个数的最小化。

3.1 CSD编码

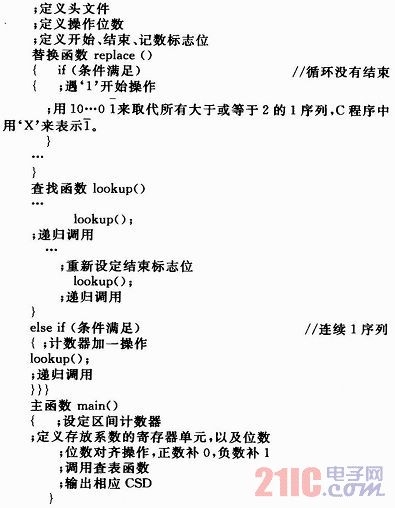

与传统的二进制编码的二值表示法不同,CSD编码的数字值域为0,1和-1。-1常表示成1。这种编码是具有最少非零元素的一种表示法,用CSD编码表示数字的形式具有惟一性。在实际硬件电路中可以采用如下原则生成最佳CSD编码:

①从最低有效位开始,用10…0![]() 取代所有大于2的1序列,此外还需要用110

取代所有大于2的1序列,此外还需要用110![]() 取代1011;

取代1011;

②从最高有效位开始,用011代替10![]() 。

。

最佳CSD编码的特点是:

①在一个CSD数据里,没有两个连续的非零位;

②对同一个数字的CSD编码是独一无二的;

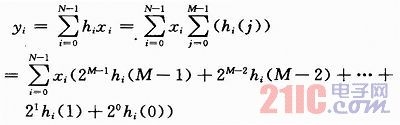

基于CSD编码,可以将式(1)做以下的变化:

从以上式子可看出,应用CSD表示法,由于可以降低系数中非零元素的数量,因而在运算中能减少加法的次数,有利于提高运算速度和减少资源的占用。

3.2 最佳CSD编码设计与结果

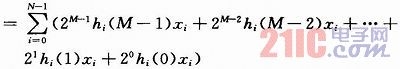

根据前面所列举的最佳CSD编码方法,用C语言生成最佳CSD编码,部分伪代码如下:

③是数字表示法里,所含非零位数最少,相比于二进制补码系统平均减少33%的非零项。

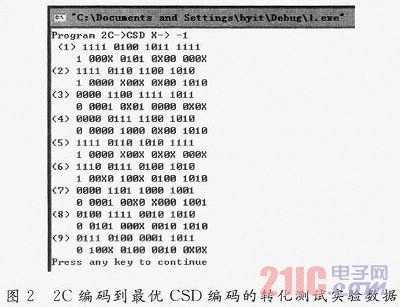

测试实验数据及结果如图2所示。在本C语言程序中用X来指代码,输入数据为16位。

4 实例设计过程与仿真

4.1 FIR系数提取

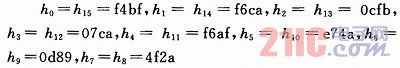

利用Matlab中Fdatlool设计一个16阶低通FIR滤波器,各项性能指标为:采用频率fs=48 kHz,截止频率fstop=12 kHz,通带宽度fpass=9.6 kHz。系数数据宽度为16位;输出数据宽度是16位。为了便于FIR滤波器的FPGA实现,减小误差,将Fdatlool提取的滤波器的系数量化取整后为:

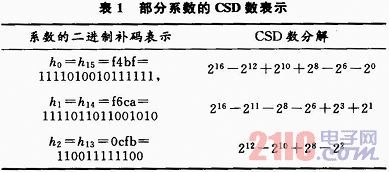

4.2 系数的CSD转换

读入量化系数,进行CSD转换操作,生成CSD码,表1是部分量化后的系数及对应的CSD数。

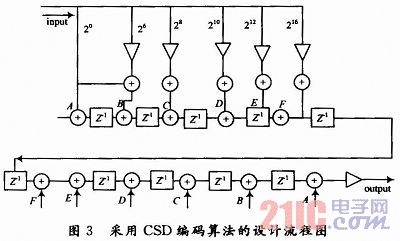

4.3 FIR滤波器实现结构

采用转置形式的FIR滤波器结构,此结构和直接型结构不同的是,输入信号X『n』是同时分别和滤波器系数向量相乘,不需要通过不同的延时单元再和相对应的滤波器系数相乘。这种结构最大的优点是工作频率较高,图3给出了采用CSD编码算法的设计流程图。

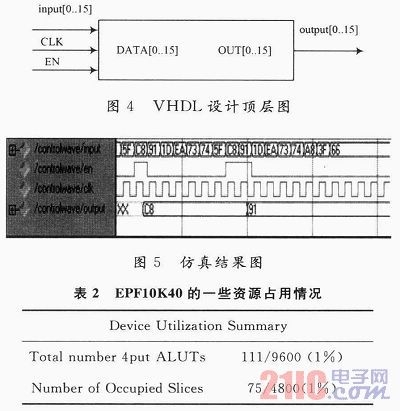

4.4 FPGA实现与仿真

参照图3中给出的设计流程,使用VHDL语言实现了该常系数滤波器的行为描述,图4是滤波器的实现顶层图。FPGA采用AItera公司的EPF 10K40芯片,该芯片最高的单路运行速率为200 MHz。图5是在MaxPIusⅡ中的仿真结果。表2给出了EPF10K40的一些资源占用情况。

5 基于FPGA的FIR试验结果

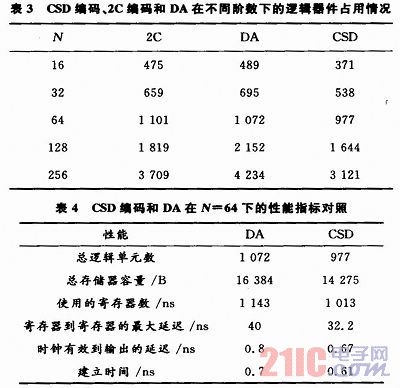

为验证本文提出的算法的普遍性,以并行DA和2C编码方式设计了一系列阶数从16到256阶的FIR滤波器,滤波器在Altera公司的开发软件MaxPlusⅡ中进行编译和布局布线,采用的目标器件为EPF10K40芯片,在系统中对3种实现结构进行测试,测试数据位宽为8位。通过表3的比较结果可以看出,使用CSD编码,资源耗用明显下降。当FIR阶数很高,系数很复杂时,CSD编码的优势会更加显著。表4给出了N=64时DA算法和CSD算法的具体性能指标,从结果来看,CSD编码相对于单纯的DA在系统资源和整个系统延迟上有明显的提高。

6 结语

滤波器用VHDL硬件描述语言实现,采用Altera公司的EPF10K40芯片,在MaxPlusⅡ中进行了仿真验证。从结果来看,文中所提出的CSD编码算法,具有一定的研究价值和实用价值,CSD编码在处理序列较多的情况下,在资源占用、速度处理方面的效果尤为明显。采用CSD编码方式对FIR滤波器进行优化设计,可减少FIR实现的FPGA资源消耗。