机载数据总线技术是现代先进飞机电传操纵系统和航空电子综合化最重要的关键技术之一,它是计算机网络技术在航空电子底层的具体实现,决定着飞机性能和航电系统综合化程度的高低。本书从数据总线技术基础、计算机网络OSI七层参考模型两方面介绍了机载数据总线的基础技术,用于民用飞机上的ARINC-429、AmNC-629和CSDB机载数据总线,以及应用于军用飞机上的MIL-S1D-1553B、MIL-STD-1773、STANAG3838/3910机载数据总线,线性令牌传递总线LTPB、光纤分布式数据接口FDDI和航空电子统一网络中可变规模互连接口SCI,光纤通道FC,以及目前最新全双工交换式以太网AFDX,全面分析了它们的技术特点、协议规范、拓扑结构及通信接口设计方法,并给出了典型的应用实例。

该转换卡采用Top-Down自顶向下的设计方法,并综合嵌入式可配置微处理器技术,来对系统进行模块化设计。顶层模块则采用图形设计方式,底层模块由VerilogHDL语言描述,并利用Quartus lI完成仿真及综合,然后在ALTERA公司的Cyclone II系列EP2C40芯片来实现。此设计提升了系统的处理速度和稳定性。降低了系统的功耗和成本。

1 MIII总线介绍

MIII总线是某型飞机火控电子设备的专用数据通信总线,又称第三级总线。MIII总线是单向地址、双向数据、半双工通信总线。

MIII总线的接口逻辑信号与电信号之间的逻辑关系是:逻辑“1”对应逻辑高电平;逻辑“0”对应逻辑高电平。

MIII总线接口信号线根据功能可分为三组,即数据通信总线、地址通信总线和信号控制总线。其中,数据通信总线包括0pKlK2~15pKlK-2;地址通信总线:0pAl~15pAl。总线的“输入”表示从MIII总线转换板向某飞机火控设备输出数码标志,“输出”则表示从某飞机火控设备向MIII总线转换板输入数码标志。MIII的A1地址选通主要用于跟踪地址数据与选择设备,外部写选通则用于在从MIII总线转换板向某飞机火控设备传输数据和地址时的数码跟踪。外部接收选通则用于在从某飞机火控设备向MIII总线转换板传输数据时的数码跟踪。

2 RS422通信协议

目前通用的串行通信接口标准主要有RS 232,RS 422和RS 485,其中RS 232属于单端不平衡传输协议,传输距离短,抗干扰性差;RS 485与RS 422均为平衡通信接口,但RS 485他只有一对双绞线,工作于半双工模式。RS 422属于一种平衡通信接口,采用全双工通信模式,传输速率高达10 Mb/s,传输距离长2 000 m,并允许在一条平衡总线上连接最多10个接收器[1]。由于该类电路的优异性能,RS 422接口芯片已广泛应用于工业控制、仪器、仪表、多媒体网络、机电一体化产品等诸多领域。

3 转换板总体设计

MIII总线转换板的总体结构如图l所示,由接口电平转换电路、总线接口控制逻辑、双口存储器和RS422转换模块组成。其中总线接口控制单元主要用于地址和数据的收发和寄存,以及接口控制信号和驱动信号的产生等;双口存储器RAM用来存放数据和地址,包括MIII总线发送的数据以及PC机发送到MIII总线上的数据和地址;接口电平转换电路由单双向驱动电路芯片组成,该电路的作用是提供符合MIII总线要求的驱动电平信号。

3.1 总线转换设计逻辑

在总线接口控制单元的设计开发中,在严格执行国军标对地面设备的研制规范等要求下,为了保证系统的可靠性,提高系统的可扩展性和性能,并尽可能采用成熟的技术和器件。

基于上述设计原则,MIII总线接口板的硬件电路应采用FPGA器件来实现。采用FPGA实现,FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

设计从系统的整体出发,应用Ouartus II软件,并采用结构化描述方式来对设计对象的功能特性进行分析,然后自上而下逐步将问题细化,再根据分析的结果划分功能模块,并根据电路功能出发使用VerilogHDL语言对各模块电路进行数据流描述,然后利用Quartus II软件进行各模块的功能仿真,再连接各模块进行逻辑综合及优化,最后下载到FPGA芯片。

3.2 RS422转换模块

此模块采用SP3490芯片进行RS422通信协议转换SP3490是一系列+3.3V低功耗的全双工收发器,它们完全满足RS-485和RS-422串行协议的要求。这两个器件与Sipex SP490、SP491的管脚互相兼容,同时兼容通用工业标准规范。SP3490和SP3491由Sipex的BiCMOS工艺制造而成,可实现低功耗操作,但性能不受影响。它们符合RS-485和RS-422串行协议的电气规范,数据传输速率可高达10Mbps(带负载)。图2所示为RS422转换模块的电路原理图。

3.3 总线接口控制单元

总线接口控制单元的主要功能是MIII总线地址和数据的收发、转换、寄存以及接口控制信号和驱动信号的产生等。SOPC)是一种特殊的嵌入式系统:首先它是片上系统(SOC),即由单个芯片完成整个系统的主要逻辑功能;其次,它是可编程系统,具有灵活的设计方式,可裁减、可扩充、可升级,并具备软硬件在系统可编程的功能。它是用可编程逻辑技术把整个系统放到一块硅片上,来用于嵌入式系统的研究和电子信息处理。 SOPC是一种特殊的嵌入式系统,它是片上系统(SOC),即由单个芯片完成整个系统的主要逻辑功能但它不是简单的SOC,它也是可编程系统,具有灵活的设计方式,可裁减、可扩充、可升级,并具备软硬件在系统可编程的功能。

关键字:FPGA RS422 MⅢ总线

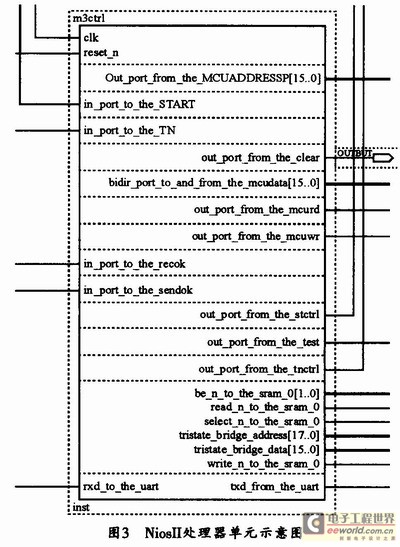

(1)Nios II处理器

Nios 处理器具有32位指令集的第二代片上可编程的软核处理器, 其最大优势和特点是模块化的硬件结构,以及由此带来的灵活性和可裁减性。相对于传统的处理器,Nios Ⅱ系统可以在设计阶段根据实际的需求来增减外设的数量和种类。设计者可以使用ALTERA 提供的开发工具SOPC Builder, 在PL D器件上创建软硬件开发的基础平台,也即用SOPC Builder创建软核CPU和参数化的接口总线Avalon。在此基础上, 可以很快地将硬件系统(包括处理器、存储器、外设接口和用户逻辑电路)与常规软件集成在单一可编程芯片中。而且, SOPC Builder还提供了标准的接口方式,以便用户将自己的外围电路做成Nios Ⅱ软核可以添加的外设模块。这种设计方式, 更加方便了各类系统的调试。采用QuartusII软件SOPC Builder生成的Nios II处理器单元如图3所示。

具体工作时,当数据流向为RS422串口到MIII总线时,NIOSII处理器可将数据从RS422串口接收缓冲存储器中读出,并输出至MIII总线发送缓冲单元中,同时还将数据发送到外部的SRAM中进行存储;而当数据流向为MIII总线到RS422串口时,其方式其之类似,其不同点是由于MIII总线的传输速率远大于串口的传输速率。

(2)MIII总线收发

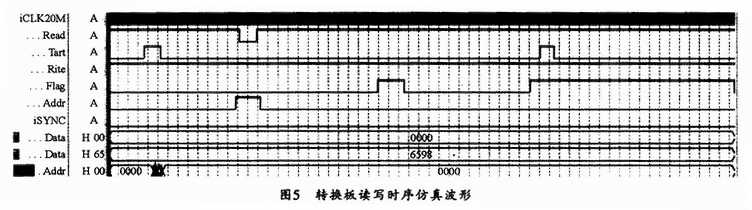

MIII总线收发功能则独立于Nios系统。它充分利用FPGA可灵活配置的特点,并用VerilogHDL语言实现MIII总线的实时性和可靠性要求较高的关键部分,然后模拟MIII总线的逻辑功能,最终实现MIII总线数据、地址的收发以及与Nios系统通过自定义的接口实现通讯。MIII总线的信号时序如图4所示。

该转换板的读写时序可用VerilogHDL语言描述,然后采用有限状态机实现上述操作,并用Quartus II进行时序仿真,其仿真波形如图5所示。

3.4 接口电平转换电路

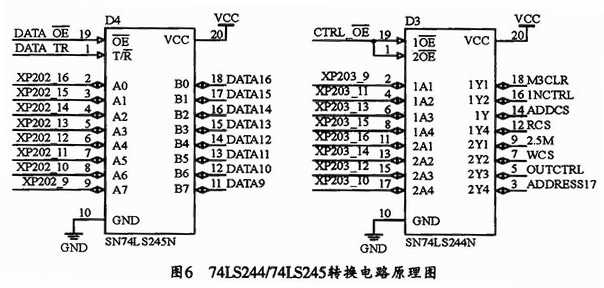

由于FPGA可编程器件的输入/输出电平通常是3.3 V,而对接MIII总线设备是OC门输入/输出。OC门又称集电极开路电路,其内部电压为+5 V。所以,FPGA的输入/输出需要进行两次电压转换。

其中,第一次电压转换是把FPGA输入/输出电平的3.3 V转换为5 V电平。由于数据信号是读写双向的,而地址和控制信号是单向的(由MIII总线发送到对接MIII总线设备),因此,其数据信号应当用74LS245芯片来进行转换,而地址和控制线则应用74LS244芯片来转换,其电路原理如图6所示。

由于对接MIII总线设备内部是OC门输入/输出,而且由于OC门电路的输出管的集电极悬空,使用时需外接一个上拉电阻到电源。一般情况下,OC门会使用上拉电阻以输出高电平,此外,为了加大输出引脚的驱动能力,选择上拉电阻阻值的原则是降低功耗及芯片的灌电流能力应当足够大,从而确保足够的驱动电流足够小。其具体的电平转换电路原理图如图7所示。

FPGA输入/输出的信号,经过以上两个步骤的电平转换,就能符合MIII总线对接设备的输入/输出信号要求。至此,只需MIII总线转换板输入/输出的地址、数据和控制信号按照MIII总线时序进行收发,就可以实现MIII总线通信。

4 结束语

本文介绍了某型火控电子设备的专用数据通信总线(MIII总线)转换板的设计方法,给出了MIII总线的总线通信功能。同时介绍了应用F-PGA实现MIII总线部分电路的实现方法。事实上,利用FPGA可简化系统结构,缩短设计周期,提高系统的性能和可扩展性。目前,该转换板经过与某型火控电子设备联调证明,其功能正常,工作稳定,且已得到了用户好评,收到了良好的社会和经济效益。