AHB总线接口的一种新实现方案

2007-12-10

作者:马天翊,薛 萍,马卫国

摘 要:针对标准AHB总线对具有特定访问时序的设备数据传输效率较低的情况,提出一种新的实现方案" title="实现方案">实现方案。利用AHB总线突发传输时的组合信息,根据某种算法生成地址和控制信号" title="控制信号">控制信号,以提高慢速设备的总线访问效率。

关键词:AHB总线 突发传输

在系统级芯片设计中,AMBA总线已经得到广泛的应用,有效地解决了复杂芯片的互连设计难题。目前AMBA总线的主要实现形式是先进高性能总线(AHB)。AHB总线的关键是对接口和互连均进行定义,目的是在任何工艺条件下实现接口和互连的最大带宽。AHB总线互连的主要形式是带有主模块和从模块的共享总线,将接口与互连分开,主要由总线的中央资源负责仲裁、重传、拆分等操作,这对芯片上各模块的接口设计具有重要意义。AMBA已不再仅仅是一种总线,而是一种带有接口模块的互连体系。

但随着AHB总线的广泛应用,一些问题也暴露出来。例如,对于具有特定访问时序的设备,AHB总线读取数据的效率较低。本文提出一种新的、高效AHB-Slave接口方案,可以在完全兼容AMBA2.0规范的前提下,将突发传输模式下的总线效率提高近一倍(具体提高依应用而定,可参见表1数据)。该方案主要通过判断总线的控制信号,利用某种算法控制地址实现,并可处理突发读数据的忙状态、写数据后立即回读、单周期突发操作等特殊情况。

1 标准AHB-Slave方案

AMBA2.0规范详细定义了标准的AHB-Slave接口,涵盖了绝大部分操作。但是对某些应用的实现不够高效,例如对具有较长延时的Slave设备的突发读操作。另外有些操作并没有定义,例如写之后立即读的操作。标准AHB-Slave实现方案介绍如下(AHB总线描述及信号列表请参阅参考文献[1]。

1.1 标准方案实现

标准的AHB-Slave总线接口首先判断读操作或写操作,如果判断为写,则对单次写和突发写执行同样操作。如果判断为读,对于单次读和突发读也不加区分,但由于突发读时地址段与数据段会自然相互重叠(overlap),所以突发读相对于多笔单次读的效率要高一些。标准AHB-Slave总线接口不支持写操作后立即执行读操作,要求二者之间至少有一个时钟周期" title="时钟周期">时钟周期的间隔,否则会产生错误。考虑接口需求,要求写后立即读的情况并不会很多。但是作为一个典型的存储设备检测方法应该被这种操作支持。

1.2 标准方案时序图

对于AHB总线,一次完整的传输可以分成两个阶段:地址段(Address Phase)和数据段(Data Phase)。地址段负责发送地址和控制信号,数据段则用来传输数据和反馈信号。如果从设备无法在数据段用一个时钟周期完成读写,则可以通过HREADY信号来展宽数据段。

AHB总线为提高传输效率定义了突发传输方式(Burst Transfer)。在一次需要传输多个数据时,将前后数据的数据段和地址段重叠在一起以提高效率。限于篇幅,关于突发传输方式的详细描述请参阅文献[1]。

还有一点需要指出:突发传输时,前次传输的数据段和后次传输的地址段重叠在一起,如果前次的数据段由于某种原因被展宽,后次传输的地址段也会随之展宽。这是AHB2.0协议中降低总线效率的重要原因,也是可以采取方法来改进的地方。

多周期读写时序如图1所示,详细说明如下。图1未示出AHB总线的申请、仲裁、授权机制。

Cycle4~9:AHB总线的突发写时序,图1所示从设备可正常接收,不再详述。

Cycle14:Master获得总线控制权,发出地址A5和控制信号,总线中央资源将其发往相关Slave。突发操作的第一个数据HTRANS信号值为NONSEQ。

Cycle15:Slave采样地址A5和控制信号,并作出判断和响应,如果不能立即存取数据,则将HREADY_OUT信号拉低相应周期数(图1中所示为一个周期),但HRESP信号为OKAY。同时,Master发出第二个传输的地址和控制信号。此时HTRANS为SEQ。

Cycle16:Slave可以完成数据存取,将HREADY_OUT信号拉高" title="拉高">拉高,将数据发送到HRDATA总线,HRESP信号仍为OKAY。因为突发传输时前后两次数据段和地址段重叠,如果前次的数据段由于某种原因被展宽,后次传输的地址段也会随之展宽。图1中所示,Master重复发出上一个时钟周期的地址A6和控制信号。

Cycle17:Master采样反馈信号。因为HREADY_IN信号为高(此时HREADY_IN与HREADY_OUT信号等价),表示Slave已经将数据发出,Master采样数据" title="采样数据">采样数据D5,同时发出地址A7和相应控制信号。Slave采样地址A6和控制信号,因为不能立即存取数据,所以将HREADY_OUT信号再次拉低一个时钟周期,但HRESP信号为OKAY。

Cycle18、19、20:分别与Cycle16、17、16类似。

Cycle21:Master判断HREADY_IN为高,采样数据D7,但不再发出新的地址和控制信号。Slave采样地址A8和控制信号,然后将HREADY_OUT信号拉低一个时钟周期,HRESP信号为OKAY。

Cycle22:Slave将HREADY_OUT信号拉高(无效),将数据D8发送到HRDATA总线,HRESP信号仍为OKAY。

Cycle23:Master采样反馈信号和数据D8,完成本次突发传输操作,之后可选择释放总线。

2 高效AHB-Slave方案

AMBA2.0规范中,对于具有较长延时的Slave设备的突发读操作处理得不够理想。针对这一问题,高效的AHB-Slave方案应运而生。突发传输时,从第二个数据开始的HTRANS信号为SEQ(Sequential,连续),表示当前地址与前一次地址相关,而控制信号与前次相同。这就表明可以利用第一个数据的地址和控制信号根据突发传输的类型来生成其后数据的地址和控制信号。

当然,由于AHB总线的功能丰富,需要考虑的情况比较多,所以高效AHB-Slave接口的实现方案相对复杂。但已经证实,当AHB总线时钟为150MHz时,可以在0.13um工艺条件下实现,且效果显著。

2.1 高效方案实现

根据AHB总线的规则,突发传输过程中,控制信号不会变化,而地址会根据突发方式和传输数据的位宽增减,所以可以依据某种算法生成内部信号HADDR_internal,用于生成超前地址,提高总线访问效率。在AHB-Slave接口设计中,用HADDR_internal代替HADDR。具体实现方案如图2所示。

首先判断读操作或写操作,如果判断为写,则对于单次写和突发写执行同样操作。如果判断为读,则区分三种情况:单次读、写后立即读与突发读。如果为单次读,则执行基本读操作。如果为写后立即读,由于AHB-Slave接口内部处理延时,读操作会多延时一个时钟周期,亦即HREADY_OUT会被多拉低一个时钟周期以通知总线的Master。如果判断为突发读,则需作进一步判断。

当判断为突发读时,需进一步判断四种情况:突发读的首数据、突发读期间的忙状态、突发读忙状态后首数据、突发读基本状态。前三种情况的处理方法如图2所示,如果判断为突发读的基本状态,则内部读地址HADDR_internal每个时钟周期递增一个单元,直到该次突发读结束。对于具有较长读延时的AHB-Slave设备,执行突发读操作时,由于第一个读数据延后n拍送出,所以外部地址HADDR从第2个地址开始延长n拍。假设n=1,从第2个地址起,外部地址HADDR比HADDR_internal延后1拍。内部模块根据HADDR_internal发出数据,此数据可以连续送到外部数据总线上。

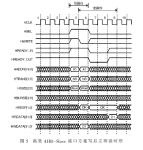

2.2 高效方案时序图

高效方案的多周期读写时序如图3。图中未示出AHB总线的申请、仲裁、授权机制。Cycle14以前各周期的功能不再详述。

Cycle14:Master发出地址A5和控制信号。依据某种算法生成内部超前地址HADDR_internal以代替HADDR,提高总线访问效率。因为Cycle14为突发传输的第一个周期,所以HADDR_internal与HADDR相同。

Cycle15:Slave采样地址A5和控制信号,由于不能立即存取数据将HREADY_OUT信号拉低一个周期。同时HADDR_internal从A5变为A6,增加一个HSIZE信号所指示的单元地址。Master发出第二个传输的地址和控制信号。此时HTRANS为SEQ。

Cycle16:Slave可以完成数据存取,将HREADY_OUT信号拉高,将数据发送到HRDATA总线。此时HADDR_internal递增为A7,超越了HADDR,因为设计中HADDR_internal代替HADDR输出给内部模块,所以数据也会提前输出。

Cycle17:Master采样反馈信号和数据D5,同时发出地址A7和相应控制信号。Slave不再采样地址和控制信号,而是用内部生成的相应信号代替,发出数据D6,并且不再拉低HREADY_OUT信号。

Cycle18:Master采样反馈信号和数据D6,同时发出地址A8和相应控制信号。Slave根据内部信号发出数据D7。

Cycle19、20:分别与Cycle17、18类似。

Cycle21~23:与标准方案的相应时序类似,不再赘述。

在突发传输操作中,Master与Slave之间的交互是连续的,但如果Master因为某些原因无法及时发送或接收数据,则可以将HTRANS信号置为BUSY,使当前传输暂停几个时钟周期。此时Slave应该发送OK的HRESP。在一次读的过程中插入busy的时序如图4。Cycle15以前各周期的功能不再详述。

Cycle15:Master由于某种原因暂时无法接收数据,可以将HTRANS信号置为BUSY,地址递增为A11,控制信号可以保持上一时钟周期的读状态不变。AHB-Slave接口采样到BUSY状态(此次采样为异步采样,不依赖时钟上升沿),则HADDR_internal不再变化,保持上一周期值。数据总线依次送出数据D10,HRESP信号仍为OKAY。

Cycle16:Master恢复采样数据,将HTRANS信号置为Sequencial,但地址保持上一时钟周期A11不变,控制信号也保持为读状态。AHB-Slave接口采样到HTRANS信号恢复Sequencial状态,重新将HADDR_internal与HADDR同步,变为A11。将数据D11送到HRDATA总线,但此数据不被采样。

Cycle17:Master本周期不采样数据。附带指出:Master在Cycle15将HTRANS置为BUSY,即指Cycle17不采样数据,而不是Cycle15不采样。Master发出递增地址A12,控制信号保持为读状态。因为上一周期HADDR_internal与HADDR重新同步,所以Slave无法立即送出数据,将HREADY_OUT拉低一个时钟周期,但HRESP信号为OKAY。同时HADDR_internal从A11变为A12,增加一个HSIZE信号所指示的单元地址。

Cycle18:Slave可以完成数据存取,将HREADY_OUT信号拉高,将数据D11发送到HRDATA总线。Master采样反馈信号并判断后重复发出上一时钟周期的地址A12和控制信号。但HADDR_internal递增为A13。

Cycle19:Master采样反馈信号,判断后采样数据D11,同时发出地址A13和相应控制信号。AHB-Slave接口内部递增地址为A14,并且不再采样AHB总线的地址和控制信号,而是用内部生成的相应信号代替,发出数据D12,并且不再拉低HREADY_OUT信号,HRESP信号保持为OKAY。

Cycle20~23:与前文类似,不再赘述。

对单一寄存器写之后读的时序如图5所示。如前文所述,考虑AHB-Slave总线接口的需求,要求写后立即读的情况并不会很多。但是这种操作作为一个典型的存储设备检测方法应该支持。此时HREADY会多拉低一个时钟周期,详细时序不再赘述。

这一AHB-Slave接口的新方案已经分别通过Cadence公司的Specman和Synopsys公司的Vera两种验证平台验证,并已实际应用于一款芯片。

表1中所示为该款芯片采用两种AHB-Slave接口方案的对比。表中最左边一栏为待传输的数据区块,JD为联合检测(Joint Detection)。其中有些数据需要写入含有AHB-Slave接口的模块,而有些数据要读出。通过AHB总线写入时两种方案完全相同,而读出时高效接口方案所需工作周期只有标准接口方案工作周期的一半。

从表1可以看出,此应用中高效接口方案比标准接口方案节省了大约44%((11804-6630)/11804=44%)的工作周期。如果AHB总线时钟按照150MHz计算,则表1中原始接口方案需要78.73us,而高效接口方案需要44.22us,节省了34.51us,这对于通信、图像处理等实时性要求较高的应用来说是很关键的。

参考文献

[1] ARM.AMBA Specification(Rev 2.0).1999.

[2] 吴欣龙.AMBA总线系统介绍.台湾:工研院内部刊物,2002.

[3] Bruce Mathewson.AMBA总线在复杂系统级芯片片上互连中的应用.电子工程专辑,2004.

[4] 钟文枫,耿彦莉.AMBA片上总线在SOC芯片设计中的应用.电子设计应用,2006.