硅上GaN LED不必受应力的影响,一定量的应力阻碍了输出功率。英国一个研究小组通过原位工具监测温度和晶片曲率,制备出低位错密度的扁平型150mm外延片,并将这些芯片安装到器件中,使得内量子效率接近40%。

美国能源署认为,LED照明的广泛使用,将对成本更低、效率更高的商业器件提出了要求。这两项标准被记录到LED的路线图中,比如,到2015年LED灯的发光效率达到150lm/W,成本低于5美元/千流明。

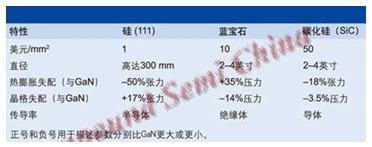

现今LED照明的成本比这个目标高了1倍以上,仅芯片成本这一项就占去了约一半的成本。但是,通过把生产工艺转向更大尺寸、更低成本的衬底,加工的成本得到控制,芯片的成本因此会降低一个数量级。

我们的英国研究联盟是由RFMD英国公司领头,其余成员来自剑桥大学、Aixtron UK、QinetiQ和Forge Europa,利用2007年4月开启的英国政府基金,我们得到了450美元的资助,以求达成上述目标。我们的研究工作致力于在150mm的硅平台上开发出高质量的LED。现在,RFMD已经制备出内量子效率(IQE)近40%的器件。

整项工作有具体的分配。剑桥大学负责前段,开发出制备高质量器件材料的生长工艺;QinetiQ为其提供生长及工艺支持,利用丰富的半导体专业技术来确保材料开发能有效地进行;之后交由LED制造商RFMD扩大生产;当器件制造商启动之后,市场工作就交给LED应用专家Forge Europa公司来打理。

硅衬底在典型生长温度下可保持稳定性,成本低;它的直径可上升至300mm,且硅表面适合外延生长,结合以上特点,硅衬底被选作生长氮化物的平台。硅上氮化物外延片也能用到硅工业中标准的生产设备,使得芯片的生产更具成本效率,芯片能接受绑定,并转变为封装型LED。

一个由英国政府资助、领军企业和研究机构牵头的项目,用MOCVD设备在150mm的硅(111)衬底上开发出硅上GaN LED,包括RFMD英国团队、剑桥大学、Aixtron UK、QinetiQ和Forge Europa。

如今LED生产使用的衬底材料一般是蓝宝石和SiC,比起它们硅有着重要的优势,但也有一个致命的弱点,那就是硅与GaN的晶格和热膨胀系数极度失配。在典型的生长温度1000℃时,若GaN直接被沉积到硅衬底上,自此刻起在生长薄膜中产生了拉应力,而且随着晶片降至室温,两种材料之间不同的膨胀系数导致了拉应力的增大。除非得到正确的控制,这种应力甚至会致使GaN薄膜的破裂。往往产生了晶片翘曲,这会让面向硅加工设计的自动化设备束手无策。作为比较,当氮化物生长在SiC衬底上,彼此的热膨胀和晶格系数相当;然而在蓝宝石上生长时它们会引起GaN薄膜的紧缩,但这不会产生裂缝。

GaN与硅之间的晶格严重失配,致使外延片中的位错密度相对高一些。虽然氮化物LED对高度位错表现出难以置信的适应性,蓝光LED的位错密度还是跌破109cm-2,IQE值也会随之下降。

在初期生长阶段,硅与反应腔中的载气发生反应,在晶体表面产生瑕疵,其表面形貌已不适合随后的GaN生长,这是硅的另一弱点。

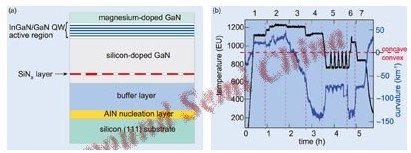

剑桥大学开发的蓝光LED生产工艺可解决所有的这些问题。其中,利用Aixtron的CCS MOCVD设备制备外延结构,设备适合生长单个150mm晶片(或多个2英寸晶片),并配有原位监测仪器用于测量晶片翘曲及温度。在150mm的硅(111)衬底上,先沉积一层复杂的势垒结构,以控制应力和晶片曲率;接着,生长一个带InGaN量子阱和GaN势垒层的多量子阱(MQW)LED结构,能发出460nm的光;最后才是一个掺镁p型GaN(图1a)。

图1.LED的结构包括一个降低位错的SiNx层(a);Aixtron的Argus工具与LayTec提供的Epicurve监测器一起,可测量出晶片翘曲以及晶片温度(b)。生长过程可分为四个步骤:预生长热处理,AlN晶核层、势垒层和n型GaN层,多量子阱区域和p型GaN层,以及退火/冷却。

衬底在氢气氛围内退火之后,移除本征半导体层并形成一个梯田状,并回流至硅表面。生长过程如下:先沉积一个AlN晶核层,确保硅表面不会分解;接着是一个复杂的势垒结构。通过对势垒层的成分和厚度进行仔细的控制以平衡应力;当生长温度降至室温时,热膨胀失配在结构内产生了应力。

为了降低位错密度、提高LED的性能,在势垒层上又沉积GaN和AlGaN层。插入SiNX层是一项用于生长蓝宝石上氮化物薄膜的技术,在很大程度上能降低线位错密度。

原位工具持续地监测晶片的温度和曲率是成功的关键,可再次生长出平整而无裂缝的材料。在剑桥大学,反应室内衬底的温度通过Aixtron的Argus工具进行图形表征,并利用LayTec的Epicurve提供实时的晶片曲率测量。

我们所使用的硅有轻微的凸起翘曲,一经加热和在位式退火之后会变成凹型,这是因为,此时衬底底端的温度比顶面要高(图1b)。AlN晶核层的添加使得凹型翘曲更为严重,但随着势垒层以及掺硅GaN层的生长,表面又呈现凸起状,压应力随之增加。量子阱的生长和势垒层导致曲率发生了少许变化,我们能察觉到,之后往GaN层中掺杂镁元素时,反应腔内的温度会增加,晶片因而变得更加凸起。薄膜的拉应力产生于GaN与硅之间存在的热膨胀系数差异,通过沉积势垒层匹配物,优化其翘曲程度,这样晶片在冷却后还非常平整。

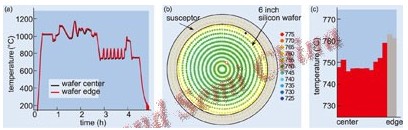

图2.Aixtron的Argus温度分布图显示了整个150mm晶片的剖面温度。通过调整反应腔加热器的放射区,能将任何差异逐一最小化(a, b, c)

生长工艺的开发把150mm外延片的生产带入更佳状态,整个表面的高度变化低于50祄。这些晶片适合用RFMD的高产量生产设备来加工处理。

为确保晶片在冷却时保持表面平整,必须在生长温度时引入翘曲;由于衬底与基座之间有着距离差异,整块晶片的温度会有明显的变动。温度变化对InGaN LED生长不利,他们改变了量子阱中的铟组分以及发光波长。幸运的是我们能用Argus分布图来监测这些温度变化,并通过调整三个加热区的输出功率将这些变化降至最小。

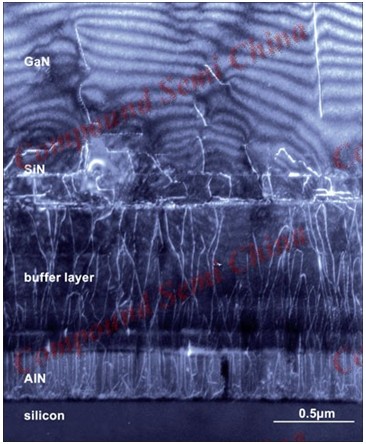

横截面透射电子显微镜图(TEM)显示,器件层结构中的SiNx层会改变缺陷的方向甚至有的消失不见了,因而导致了低位错密度(图3)。与AlN相比GaN的面内晶格参数更大,它产生的压应力使得AlGaN/GaN界面也出现这种现象。

图3.TEM图中的淡线和深色区域展示出,SiN层有助于降低InGaN/GaN LED中的位错密度。图中纯螺旋式/混合型的位错清晰可见。

用TEM的平面图来评估外延片中的位错密度。汇同其它的原子力显微镜图像(在860°C时将表面暴露在硅烷助熔剂下面,可突出凹坑),最终测得硅上GaN材料的位错密度值低于109cm-2。

在曼切斯特大学,研究人员使用光致光测量法PL(受温度的影响)来评估材料的IQE值,在室温下约为50%。使用这种方法的前提是,假定非辐射复合接近零基本予以忽略。生长在蓝宝石上的类似结构,它的位错密度是108cm-2,典型的IQE值是70%;这表明在硅平台上制备高性能LED的时候,硅上氮化物的位错密度不可能成为一个主要的问题。我们在QinetiQ继续制备LED。通过刻蚀一个n型GaN层的台面。接着,往上面沉积一层Ti/Al/Pt/Au合金以产生n型接触;p型接触是一个退火后的半透明NiAu和一个更厚的金接触焊盘。

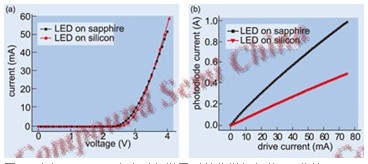

我们最好的0.5×0.5mm LED,它所呈现的I-V特性与蓝宝石上GaN器件极其相似,开通电压约是2.5V(图4),使用相同的光学方法测量两种器件的顶部光输出,结果发现蓝宝石基LED产生的光输出是硅器件的两倍。考虑到硅衬底的光吸收较大,对LED正向的总发光量进行测量,据计算硅上LED的IQE是37%。

图4. 硅上GaN LED产生了与常用器件非常相似的I-V曲线(a);但这种类型器件的光输出不到一半左右(b)

图5 硅、蓝宝石和SiC之比较

硅上LED仍处于早期阶段,但初始结果令我们非常振奋。移除硅衬底可防止光吸收,但它将不再对制造商构成威胁,原因是高亮度LED生产通常会采取倒装焊接和衬底移除。通过使用先进的封装及合适的荧光粉,我们现有的器件的发光效率可达70lm/W,这与基于蓝宝石的LED形成了对照。由于硅的成本低,这意味着,在硅上生长的GaN LED将接近美国能源署关于2012年每千流明成本所需达到的目标。这些将促使我们的器件成为固态照明应用中名副其实的竞争者。随着原位生长技术的提高,带来了更高质量的材料,为此器件的性能只会变得更好。