1 引言

在Altera的Nios嵌入式处理器中。用户可以在Nios指令系统中增加用户自定制指令来满足某种特定的应用需求。自定制指令可以访问存储器或Nios系统外的逻辑资源。增强系统的实时处理能力,特别适用于DSP、数据包处理及对计算密集型软件进行优化。

Altera高性能快速傅立叶变换(FFT)处理器IP核FFT V2.2.0为实现高速FFT算法提供了成功的解决方案,将FFT算法定制为Nios嵌入式处理器的用户指令,用已实现的高性能FFT算法作为Nios嵌入式系统的一个加速模块,使系统可以完成复杂的数据处理任务。

2 Nios自定制指令的软硬件接口

使用用户自定制指令,用户能够向Nios的ALU和指令系统增加用户自定制功能,完整的用户自定制指令包括用户自定制逻辑和软件宏两部分。

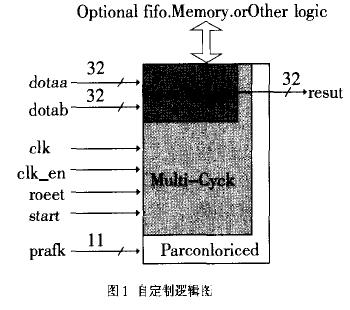

用户自定制逻辑是完成用户操作的硬件部分,Nios最多支持5个用户自定制逻辑作为ALU的一部分。软件宏提供软件接口,Nios将创建相应C/C++和汇编的宏代码,使得用户能够访问用户自定制逻辑。Nios自定制指令支持多种设计文件,主要有Verilog HDL、VHDL、EDIF netlist file、Quartus II Block Design File等。由于用户自定制指令逻辑需要直接连到ALU上.所以Nios提供一套预先定义好名称和功能的接口,如图1所示。Nios配置向导会扫描用户自定义逻辑,搜索需要的端口。并把这些端口连到ALU上,这就要求用户自定制逻辑必须指定所需的端口类型,使用预先定义的端口名称。保证自定制逻辑端口能正确地连到ALU。

当然,Nios也允许用户自定制指令与Nios系统外部的功能模块进行信息交流。如果配置向导没能识别用户逻辑模块的某个端口。它将该端口引出到系统模块的顶层.使得外部逻辑可以访问这些信号,这些端口用export标记。当用户自定制逻辑被集成到Nios处理器的ALU后.可以通过软件访问用户自定制逻辑,Nios系统中包括5个用户操作码,如表1所示,用户可以通过用C/C++或汇编写的宏来调用这些操作码,通过它们来访问用户自定制逻辑。

表1 用户操作码、类型和操作

写C/C++代码时,Nios寄存器的使用是透明的,编译器会自动选择寄存器,而在汇编中则必须指定寄存器。在增加了用户自定制指令后,Nios配置向导会自动创建相应的宏,支持对宏进行手工命名,以提高软件代码的可读性。

在C/C++中通过一个函数调用来访问用户自定义指令。SOPC Builder自动生成的Nios系统头文件(excalibur.h)里包含了C/C++的宏定义,有两种不同的C/C++宏可供使用,其中前一个使用了prefix端口,后一个没有使用prefix端口。

nm_

nm_

3 FFT算法实现

FFT算法由Altera的FFT IP核FFT V2.2.0实现,FFT V2.2.0是一个高性能、参数化快速傅立叶变换(FFT)处理器IP核,对Altera StratixII、Stratix GX、Stratix以及Cyclone系列器件进行了设计优化.可以完成变换长度为2m(6≤m≤14)的基-2/4按频率抽取(DIF)的复数FFT算法,IP核使用模块浮点结构可在

数据处理过程中保持最大数据动态范围,以获得最大信噪比SNR与最少逻辑需求之间的平衡。

此处FFT V2.2.0相关参数设置为:变换长度(Transform Length)选择1024点,数据精度选择16位,旋转因子精度选择16位,I/O数据流选择Streaming形式,复数乘法器结构(Structure)由3个乘法器、5个加法器完成。

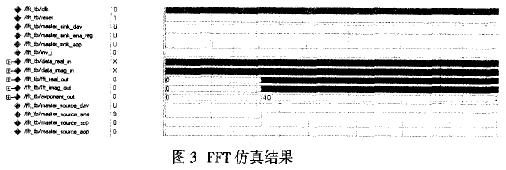

图2给出了FFT算法模块的外部端口,I/O接口协议采用Atlantic接口,输入接口为主设备汇端(Master Sink),输出接口为主设备源端(Master Source),Atlantic接口相关内容可查阅文献3,图3为FFT在Modelsim环境下的仿真结果。

4 定制Nios核的FFT指令

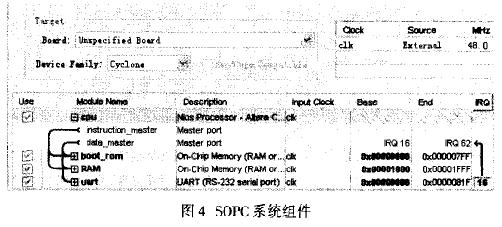

应用SOPC Builder系统开发工具建立一个嵌入Nios软核的基本SOPC系统,系统组件如图4所示。显然,用户可以根据实际应用的需要增加其它SOPC系统组件,这里仅分析定制FFT算法指令相关内容。

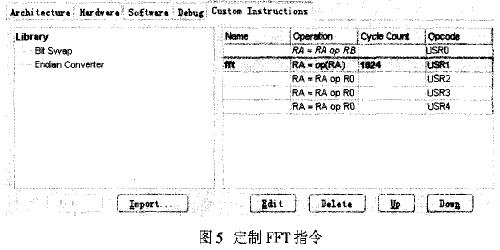

通过自定制指令“Custom Instruction”界面中Import按钮导入设计好的FFT.vhd文件,定制用户指令FFT,这里使用USR1操作码,如图5所示。

在Nios系统中用户自定制逻辑必须与指定的端口类型匹配,对于FFT来说,其输入和输出都是实部和虚部为16位的复数,正好可以用一个32位的值来表示 这样FFT.vhd程序的端口(port)可以按如下方法设置:

PORT(

clk:IN STD_ LOGIC;

reset:IN STD_LOGIC;

dataa:IN STD_LOGIC_VECTOR(31 DOWNTO 0);

result:OUT STD_LOGIC_VECTOR(31 DOWNTO 0);

start:IN OUT STD_LOGIC:=‘0’;

clk_en:IN STD LOGIC:=‘0’

……

);

即将程序中原有16位长的data_real_in,data_imag_in,fft_real_out,fft_imag_out端口换成两个32的输入输出端口dataa和result,另外,还必须加上start和clk_en两个输入端口,虽然这两个端口信号在程序中没有作用。端口例化时再与原有端口对应,如下所示:

data_real_in => dataa(31 downto 16),

data_imag_in => dataa(15 downto 0),

fft_real_out => result(31 downto 16),

fit_imag_out => result(15 downto 0),

FFT其余Atlantic接口信号用export标记,这些端口引出到系统模块的顶层,外部逻辑可以访问这些信号。

重新生成SOPC系统并更新后得到如图6所示的加入自定制FFT算法指令的Nios处理器,将其全程编译并下载到相应FPGA后,结合Atlantic接口逻辑、FIFO存储器电路,用户即可在C或C++中调用nm_fft指令来完成1024点的高速FFT算法。

5 结论

自定制Nios处理器的用户指令方法,使设计者可以为某种特定的应用定制自己的指令,定制指令的方法在降低软件复杂性的同时,明显地提高了Nios处理器的性能.帮助系统完成复杂的数据处理。

本文作者创新点:基于IP核FFT V2.2.0实现了变换长度为1024点的高速复数FFT算法,提出了一种新颖的在Nios嵌入式系统中定制用户FFT算法指令的方法,使系统可以完成复杂的数据处理任务,增强了系统的实时处理能力。

参考文献:

[1]梁曦捷,肖璋.一种基于FPGA的顺序迭代FFT设计 微计算机信息,2005,1-2

[2]Altera DataSheet FFT Compiler Megacore Function User Guide 2.2.0 rev1 2005.10

[3]Altera DataSheet Custom instructions for the Nios embedded Processor User Guide ve1.1.2 2002.9

[4]Altera DataSheet Altera Interface Functional Specificmion Ver.3.0 2002.6

[5]潘松 黄继业 曾毓 SOPC技术实用教程[M]北京清华大学出版社2005年3月131-139