MVB1类设备控制器的FPGA设计

2007-12-27

作者:MVB1类设备控制器的FPGA设

摘 要:以Xilinx公司的ISE为开发平台,采用Xilinx Spartan2e XC2S200-5PQ2081芯片,实现了MVB1类设备控制器" title="设备控制器">设备控制器的功能,并搭建了测试模型,在Modelsim中仿真了其收/发帧及报文分析等功能,得到了符合IEC61375协议的帧波形。

关键词:MVB控制器专用芯片 FPGA MVB1类设备控制器

MVB(多功能车辆总线)控制器是MVB上的核心处理器,它独立于物理层和功能设备,为在总线上的各个设备提供通讯接口和通讯服务。在MVB协议结构层次中,MVB控制器完成链路层的功能,依靠物理层发送和接收具有电气特征的电信号,同时为网络层提供过程数据(包括监视数据)、消息数据的变量接口。该接口采用TM(共享通讯存储器)实现,即应用层的CPU和链路层的MVB控制器一致地访问TM,即对端口中所有数据的读和写在一次不可分割的操作中完成[1-2]。

目前国外厂商垄断着对MVB控制器芯片的制造,致使在国内购买MVB控制器芯片价格昂贵。用FPGA替代MVB控制器专用芯片,是一个很好的解决方案。FPGA作为一种可编程逻辑器件,可以完成数字集成电路的大多数功能,由于其内部有丰富的可编程资源,使模块的修改、验证、功能扩展都十分方便。应用FPGA还可以在内部实现与应用处理器的接口转换,简化外围电路[3]。另外,FPGA低廉的价格也是其替代专用集成电路的一大优势。

在MVB中大量应用具有过程数据传输和设备状态数据传输能力的1类设备。1类设备逻辑不支持CPU或微处理器的操作。它主要作为传感器执行单元,只进行数据的采集和传输,不进行处理,因此可以单独用FPGA和简单外围电子电路实现网络传输和控制功能,不需要CPU[4~5]。在设计好MVB1类设备控制器的基础上,可根据需要采用模块复用技术把MVB1类设备控制器扩展为MVB2、3、4或5类设备控制器[6]。

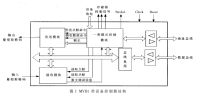

1 总体结构

设计中采用自顶向下的方法。自顶向下的设计是从系统级开始,把系统划分为若干个基本单元,然后再把每个单元划分为下一层次的基本单元,直到可以直接用EDA元件库中的基本元件实现为止。MVB1类设备控制器的顶层结构主要包括发送模块" title="发送模块">发送模块、接收模块" title="接收模块">接收模块和MVB1类模式控制模块" title="控制模块">控制模块[7-8],如图1所示。当MVB1类设备被16位主帧轮询时,1类设备控制器先判断该主帧的第11至4位是否与设备所配置的设备地址相同,如果相同则表明该设备被寻址,需响应从帧或接收其他从设备响应的从帧。

1.1 发送模块

发送模块实现的功能是把MVB1类设备控制器从TM中提取的数据进行并串转换,加上帧头、起始位和CRC校验后再经过曼彻斯特编码发送到MVB上。

1.2 接收模块

接收模块的功能主要有两部分:译码,即对MVB1类设备控制器从MVB上检测到的曼彻斯特码进行解码,串并转换后存储在缓冲区中;线路检测,主要检测线路上的各种错误(包括CRC校验、帧长检测、曼彻斯特码违规等),并向MVB1类模式控制模块提交错误报告。

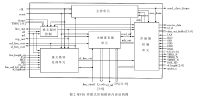

1.3 MVB1类设备控制模块

MVB1类设备控制模块包括报文超时单元、报文错误处理单元、主帧寄存器单元、TM控制单元" title="控制单元">控制单元和主控单元,如图2所示。

1.3.1 报文超时单元

在主帧结束后的一定时间,接收模块没有报告收到正确的从帧,本单元产生应答超时信号;接收模块没有报告接收到正确的主帧,本单元产生线路超时信号。

1.3.2 报文错误控制单元

接收模块报告收到正确主帧时,请求主帧寄存器单元向接收模块发读主帧命令,对错误主帧不处理。收到正确的从帧时,请求主控单元发存储从帧命令,对错误从帧不处理。无应答超时下收到多个主帧,只应用最后一个。两个主帧间有多个从帧,只对第一个从帧处理。

1.3.3 主帧寄存器单元

当报文分析单元收到正确的主帧后产生读取主帧rd_mf信号,通知接收模块把缓冲区的主帧数据送入数据总线供本单元读入到MFR(主帧寄存器)中;比较MFR与设备地址,如果相同则产生设备寻址信号device_sele送往主控单元,表示选中该设备以期进行下一步操作。

1.3.4 TM访问控制单元

TM访问控制单元的功能包括:产生对TM的读写控制和片选信号;判断f_code(主帧高四位),如果在0~4之间,表明该主帧是过程数据请求,如果为15,表明该主帧是设备状态请求。当主帧是过程数据请求时,如果主帧的低四位在0~7之间,表明主帧访问的是源端口(产生source信号),控制器从TM中提取从帧经发送模块发送出去;如果是在8~15之间,表明主帧访问的是宿端口(产生sink信号),控制器等待接收其他从设备发送的从帧数据。对端口15的写操作将触发同步信号strobe_n有效。当主帧是设备状态请求时,由本单元内部产生设备状态报文响应从帧数据,经发送模块发送。状态机如图3所示。

状态机在IDLE状态且read_mf信号有效时,跳转到RECEIVE_MF状态。此时若收到source信号,则跳转到SEND_SF_READY状态,准备发送从帧;如果收到sink信号,则跳转到RECEIVE_SF_READY状态,准备接收从帧。状态机在SEND_SF_READY状态,收到send_slave_frame信号,跳转到SEND_SF,发送从帧。此时TM访问控制单元实现两种功能:f_code为0~4时对外部TM发出读请求;f_code为15时,产生DSR_RD响应设备状态请求。对TM的读请求包括TMCS_N与TMRD_N,如图4所示,当f_code为0~4之间时,TMCS有效,表示对外部TM中进行读/写操作。本单元定义了计数器counter用来产生读请求TMRD_N,如图4中当f_code为0010时,要从TM读取4个word的从帧,计数器从此状态初计数,计到1、3、5、7时TMRD_N为低电平。外部TM每接到一个TMRD_N信号,提取一个字的数据到数据总线。当计数器计到7时,已经从TM中提取了正确长度的从帧,状态机跳转到SEND_SF_OVER状态,表示读从帧结束。f_code为15时,counter计数到1产生低脉冲信号DSR_RD,同时产生设备状态响应。TMRD_N有效时,本单元将向发送模块发送receive_data信号,通知它准备接收数据总线上的数据。状态机在RECEIVE_SF_READY状态时,如果收到应答超时或者从帧错误信号,则跳回到IDLE状态,准备重新接收下一主帧请求;如果收到save_slave_frame信号,则跳转到RECEIVE_SF状态准备接收从帧。状态机在RECEIVE_SF时,TM访问控制单元向外部TM发出写请求。写请求信号包括TMCS_N和TMWR_N信号,其时序图如图4所示。同样,写请求TMWR_N的产生与读请求类似。当向TM中写入正确长度的从帧数据时,状态机跳转到RECEIVE_SF_OVER状态,表示写从帧操作结束。当TMWR_N信号有效时,本单元向解码模块发送rd_sf信号,表示要从该模块提取从帧到数据总线上。在SEND_SF_OVER或RECEIVE_SF_OVER状态将直接跳回IDLE。

1.3.5 主控单元

产生read_mf信号,作为TM访问控制单元读取主帧寄存器的使能信号。

如果收到TM控制单元送来的source信号,则在本单元内产生send_slave_frame信号送往TM控制单元和发送模块,通知TM控制单元从TM中提取数据到数据总线上,再由发送模块提取数据到发送FIFO中以发送;如果收到TM控制单元送来的sink信号,并且报文错误,处理单元报告收到正确的从帧,在本单元内部将产生save_slave_frame信号送往TM控制单元,通知TM控制单元准备接收从帧并存储到TM中。主控单元各个信号的产生时序图如图5所示。

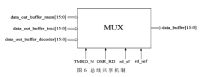

1.4 总线复用器

为了节省资源,在MVB1类设备控制器顶层模块定义了总线复用器,用来实现各个模块的总线共享。为了避免总线冲突,同一时刻只能有一个模块向总线发送数据以供其他模块接收,总线在空闲时呈高阻态。各个模块访问总线机制采用多路选择器的方式,如图6所示。

当TMRD_N有效时,控制器从TM中提取的数据经存储器输出数据总线data_out_buffer_mem被输入到控制器内部公共数据总线上,以供发送模块接收。当DSR_RD信号有效时,由TM控制模块产生16位从帧数据,经数据总线data_out_buffer_tmc发送到公共数据总线上供发送模块接收。当rd_sf或rd_mf信号有效时,接收模块FIFO中的数据经数据总线data_out_buffer_decoder被送至公共数据总线上以供TM或TM控制模块接收。

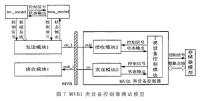

2 测试

MVB1类设备控制器的测试模型如图7所示。测试MVB1类设备控制器的功能包括:测试是否能收到正确的主帧;收到正确主帧后,如果主帧是过程数据请求,并且访问的是源端口,能否从TM提取数据发送到MVB上;如果访问的是宿端口,能否正确接收其他从设备发送到MVB上的从帧,再发送到MVB总线上。为了进行有效测试,如图7所示定义了可以调用发送主/从帧命令的测试模型mcu_model、提供发送主/从帧数据的模型tm_model及MVB1类设备外部TM模型。

图8、图9为部分仿真波形。发送模块1发送主帧0c50。由图8可知,MVB1类设备控制器检测到发送模块1发送的主帧后,通过总线data_out_buffer_mem从外部TM中提取一个字长的数据到数据总线上经发送模块2发送。由仿真图可以看出TMCS_N及TMRD_N有效。

发送模块1发送主帧0c5f后再发送16 位从帧数据。由图9可知控制器检测到发送模块1发送的主帧后,又收到16位的从帧数据,并通过总线data_in_buffer_mem把数据送到TM中。由于是对端口15的操作,由图中可以看出TMCS_N、TMWR_N及同步信号strobe_n有效。

本文在研究MVB的基础上,用FPGA实现了MVB1类设备控制器的设计,具体描述了1类设备控制器各个模块的功能及设计方法。经过仿真验证,该1类设备控制器能够成功收发帧数据,对报文进行分析,并且由于该1类设备控制器采用了自顶向下的设计原则,设计的各个子模块功能相互独立,因此易于扩展。当设计MVB2、3、4或5类设备控制器时,可以在本设计的基础上采用模块(发送模块、接收模块)复用的方法,从而有效地节省资源。经过实践证明使用该设计比购买专用处理芯片MVB控制器大大节省了成本。

参考文献

[1] ADTRANZ. Multifunction vehicle bus controller data sheet(Revision)[Z]. Switzerland: Adtranz.1997.

[2] IEC61357-1 Part 1. Train communication network[S],1999.

[3] 蔡颖.MVB网络接口单元的SOC解决方案.沿海企业与科技,2005,(4):139-140.

[4] JIMENEZ J, JOSE M. Comparison of two designs for the multifunction vehicle bus IEEE transactions on computeraided design of integrated circuits and systems : accepted for future publication. Volume PP, Issue 99, 2005:1-1.

[5] 王锋.基于FPGA的MVB1类设备网卡的设计[J]. 机车电传动,2004,(6):21-23.

[6] BONSEN, G A. The multifunction vehicle bus (MVB) factory communication systems. 1995.WFCS ’95, Proceed-

ings., 1995 IEEE International Workshop on 4-6 Oct. 1995 Page(s):27-34.

[7] JIMENEZ J, MARTIN J L, CUADRADO C et al. A topdown design for the train communication network industrial technology.2003 IEEE International Conference on Volume 2,10-12 Dec. 2003 Page(s):1000-1005.

[8] International electrotechnical commission, IEC 61375-3,Clause 3: Multifunction Vehicle Bus, 1999.

《电子技术应用》2007年第2期