1 Viterbi译码算法

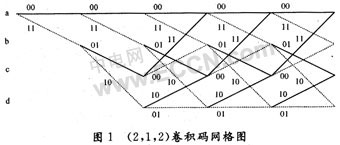

Viterbi 译码算法由维特比在1967年提出。Viterbi译码算法实质上是最大似然译码,他巧妙利用编码网格图的特殊结构,从而降低计算的复杂性。例如图1即为 (2,1,2)卷积码的网格图。这里(n,k,m)分别指码组宽度n,信息元个数k和编码存储度m,称m+1=N为编码约束度。

该算法思想是:计算网格图上在时刻L到达各个状态的路径和接收序列之间的相似度;在形成的多条路径中,去除不可能成为最大似然选择对象的网格图上的路径, 即,如果有两条路径到达同一状态,则具有最佳量度的路径被选中,称为幸存路径。对所有状态都将进行这样的路径选择操作,译码器不断在网格图上深入,通过去 除可能性最小的路径实现判决。

Viterbi译码算法步骤如下:

(1)用数组p(i,j),c(i,j)描述网格图结构。p(i,j)表示到达状态i的第j个前状态,其对应的码字是(i,j)。

(2)计算第L时刻接收码RL相对于各码字睁相似度,亦称作分支量度BM(Branch Metric)。

![]()

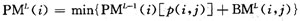

(3)计算第L时刻到达状态i的最大似然路径之相似度,也即路径量度PM(Path Metric)。

(4)译码输出并更新第L时刻、状态i对应的幸存路径。具体步骤是:

①将到达状态i的最大似然路径的前状态j所对应幸存路径作为本时刻状态i的幸存路径,即SL(i)=SL-1(j);

②选择具有最小(最似然)PM那个状态对应的幸存路径最旧的码字作为译码输出;

③将各状态幸存路径最旧的码字从各移存器移出,再将到达各状态的最大似然路径在时刻L所对应的码字从移位寄存器的输入端移入幸存路径SL(i)。

2 FPGA编译码器

编码器结构比较简单,其所选用的系列器件可选性较大,这里选用Altera公司MAX7000器件系列,他的制造工艺是E2PROM,集成度(逻辑门数)为600~10000,管脚延时为6 ns,工作频率可以达到151.5 MHz。译码器的整体结构相对要复杂一些,因此所选用的系列器件要求较高,本文选用Altera公司FLEX10K器件系列,他的制造工艺是SRAM,集成度(逻辑门数)为1万~25万。

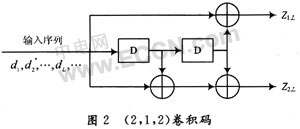

下面以(2,1,2)卷积码为例进行设计,如图2所示。

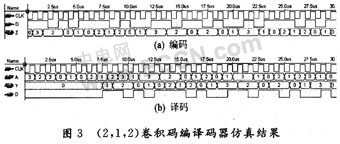

采用VHDL语言进行编程设计,经Max+PlusⅡ编译、仿真,结果如图3所示。图3(a)中D为原始比特信息,Z为编码输出;图3(b)中A为接收码,Y为纠错译码,D为译码输出。对比知该译码器实现了正确译码。

3译码器性能分析

对于(n,k,m)卷积码,其编码存储度(移位寄存器单元的数量)为m,幸存路径有2m条。每条幸存路径(或信息序列)存储器单元数是n*D,其中,n是 卷积码码组宽度,D是需要存储的码组的个数。D的取值一般考虑取m的整倍数,称D为幸存路径长度。编码存储度和幸存路径长度的取值问题关系到芯片规格、传 输时延等问题。若D很大,则译码器的存储量太大而难以实用。一般情况下,当译码进行到第5级(每级包括m个时刻)以后,每个状态幸存路径的前几个分支已基 本重合在一起,这就是说每个路径存储器不必存储D个很大的码序列。译码时,当译码器接收并处理完第D个码组后,译码器中的幸存路径存储器已全部存满,当译 码器开始处理第D+1个码组时,他就对幸存路径存储器中的最顶端的码组做出判决并输出。

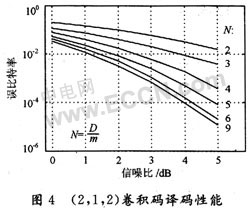

按照上述Viterbi译码步骤,采用Matlab仿真,在AWGN信道下,当D取m的2~9倍时,即D=N*m,N=2,3,…,9,得(2,1,2)卷积码的传输性能如图4所示。

当编码存储度增加时,卷积码译码性能也有所提高。依照上述编译码过程,得出(2,1,3)卷积码的传输性能如图5所示。

对比仿真结果图4与图5,可得出如下结论:

(1)适当增加幸存路径的长度可以提高译码器的纠错能力。图4中N值由2递增到9的过程中,其误比特率逐渐降低。

(2)幸存路径的长度在增加到一定值时,译码器纠错能力趋于稳定。当N值增加到6以上,误比特率降低幅度大为减小,曲线有合二为一的趋势。因此,可以认为幸存路径长度D取编码存储度的6倍以上就可以取得比较好的译码性能。

(3) 增加寄存器数目(即编码存储度m)可以适当提高译码性能。图3(a)与图3(b)中寄存器数目分别为2和3,对比两图可知,在N值和信噪比取值相同的情况 下,后者的误比特率较低。需要说明的一点是,编码存储度m取值不宜过大,在Viterbi译码过程中,他将分别对应2m个状态、路径量度和2m条幸荐路 径,译码器存储单元与计算量将随m成指数地增加。Odenwalder给出的常用卷积码的短编码存储度为2~7。

4 结语

本文探讨了广泛用于远距离实时通信的卷积码Viterbi译码器的实现及其传输性能。采用硬件描述语言VHDL和Altera公司高FPGA芯片使方案设 计具有较强的灵活性。本文对译码算法中幸存路径长度和编码存储度参数的取值问题给出了比较合理的结果,在卷积码编译码设计中具有较好的指导性和实用性。

卷积码是一种前向纠错控制(Forward Error Control,FEC)编码方式,其特点是接收端根据接收码字自动检测和纠正信道传输引入的错误。由于FEC方式不需要反馈信道,译码实时性比较好,控 制电路比较简单,因此,卷积码在卫星通信、数字话音通信等实时性要求较高的场合有着重要的应用。卷积码的编译码器的实现可以利用EDA技术,采用硬件描述 语言VerilogHDL或VHDL等进行FPGA编程设计,这种实现方式在集成度、可靠性和灵活性方面可达到比较满意的效果。在设计卷积码FPGA译码 器时,需要考虑所用芯片规格、成本、系统计算量以及时延等因素。目前现有文献多对卷积码的实现进行研究,而对译码算法中参数设置情况研究较少。本文采用 VHDL语言,在设计实现卷积码FPGA编译码器的基础上,通过仿真对Viterbi译码算法中的参数进行了讨论。