Altera DSTB和DTV系统解决方案

2008-01-18

作者:Altera公司

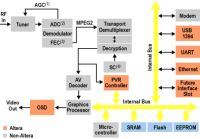

数字机顶盒" title="数字机顶盒">数字机顶盒(DSTB)接收和解码从卫星广播,有线电视和/或地面电视的信源,而数字电视(DTV)则有内置的数字调谐器,解码器和信源译码器,因此,DTV能直接接收数字广播而不需要数字机顶盒(DSTB). Altera公司的低成本Cyclone III,MAX II和MAX 3000A能为音频和视频处理提供高性价比" title="高性价比">高性价比的可编程" title="可编程">可编程解决方案,非常适合数字视频的应用.Cyclone FPGA系列和MAX CPLD系列产品还具有ASSP的系统功能如屏幕视控系统(OSD)和时序显示.本文介绍了采用Altera FPGA的低成本可编程DSTB和DTV解决方案, 以及Cyclone III FPGA开发套件" title="开发套件">开发套件和Cyclone III FPGA入门板的方框图和部分电路图.

Cyclone III FPGA入门板外形图

Digital Set-Top Boxes & Integrated Digital Television Systems

Digital set-top boxes (DSTBs) receive and decode television broadcasts from satellite, cable, and/or terrestrial sources. Integrated digital televisions (DTVs) have built-in digital tuners, demodulators, and source decoders, so they do not require digital set-top boxes that receive digital broadcasts.

Traditional DSTBs are designed to receive standard definition (SD) Moving Pictures Experts Group-2 (MPEG-2) video format broadcasts. However, many of today’s DSTBs are high-definition (HD)-ready. In fact, selected cable television service providers, networks, and local terrestrial TV stations are concurrently transmitting both SD and HD content. Over time, MPEG-4 will displace the MPEG-2 format for both SD and HD.

When MPEG-4 becomes the standard compression standard, systems implementing reprogrammable logic devices (such as Altera® FPGAs) will be able to seamlessly upgrade without having to scrap inventory items or make new hardware. Using FPGAs, manufacturers can design a STB that can decode MPEG-2 video format, and then later upgrade that same STB for MPEG-4 by simply reprogramming the FPGA in-system.

The FCC’s historic plug-and-play agreement between cable operators and consumer electronics manufacturers in September 2003 established HDTV interface standards for DTVs and DSTBs (not including satellite DSTBs). This agreement allows consumers to purchase plug-and-play integrated DTVs that can receive terrestrial digital signals or digital cable signals without using STBs. In addition, this agreement established copyright and consumer protection standards, enabling DSTBs to access future premium services such as video-on-demand (VOD) for cable or Internet access.

High-end DSTBs may also offer personal video recorder (PVR) and/or a DVD recorder functions. Microcontrollers in DSTBs or integrated DTVs can perform a number of functions for these systems, including control panel management and on-screen display (OSD).

Many current DSTBs can be classified either as free to air (FTA) or pay TV versions. A pay TV example would be DSTBs designed for DirecTV or Dish Network (in the USA), which require conditional access to decode the audio and video.

DSTB manufacturers typically design the printed circuit boards (PCBs) for both low-end and high-end DSTB systems and require a flexible solution for implementing their various designs. Figure 1 shows a typical Altera programmable logic device (PLD) solution for DSTBs and depicts one of the wide range of applications that are possible with an FPGA-based solution.

图1.采用Altera FPGA的DSTB和DTV解决方案

低成本可编程DSTB和DTV解决方案

Altera’s low-cost Cyclone III, MAX II, and MAX 3000A devices provide cost-effective programmable solutions for audio and video processing, making these devices ideal for digital video applications. The Cyclone FPGA series and the MAX CPLD series also contain system functions that complement available ASSPs, such as on-screen display (OSD) and timing display.

Cyclone III FPGAs are built on a 65-nm low power (LP) process technology. The Cyclone III family is comprised of eight devices ranging from 5K to 120K logic elements (LEs) and up to 534 user I/O pins. Cyclone III FPGAs offer up to 4 Mbits of embedded memory, 288 embedded 18x18 multipliers, dedicated external memory interface circuitry, and phase-locked loops (PLLs) making them ideal for high-end video and image processing functions.

The Altera Nios II family of embedded processors can be implemented in Cyclone series devices for high-performance, cost-efficient processing solutions. The Cyclone series and its solutions offer digital video designers unparalleled capability at extremely affordable pricing.

Altera’s MAX CPLD series is the industry’s most successful and widely used CPLDs. MAX 3000A devices are optimized for high-volume, cost-sensitive applications. Altera’s latest CPLDs, MAX II devices, are designed for low-cost and low-power applications. The non-volatile and low-cost features of the MAX 3000A and MAX II devices make them ideal for DVD player/recorder functions such as address decoding, system timing, and system bug fixes.

Cyclone III FPGA 开发板" title="开发板">开发板

These hardware-based solutions contain everything you need to create and implement a design in hours.

Altera developed the high-speed mezzanine connector (HSMC) specification to define and standardize the interface between optional daughtercards and host boards (see Figure 1). This specification outlines both the electrical and mechanical properties of the interface between daughtercard and host. You can also create your own HSMC-based prototype daughtercards.

开发板套件包括:

The Cyclone III FPGA Starter Development Kit is RoHS compliant and features:

Cyclone III starter board (See Figure 1)

Cyclone III EP3C25F324 FPGA

Configuration

Embedded USB-Blaster™ circuitry (includes an Altera EPM3128A CPLD) allowing download of FPGA configuration files via the users USB port

Power and analog devices from Linear Technology

Switching power supply LTM4603EV-1

Switching and step-down regulators LTC3413 and LT1959

Memory

256-Mbit of DDR SDRAM

1-Mbyte of synchronous SRAM

16-Mbytes of Intel P30/P33 flash

Clocking

50-MHz on-board oscillator

Switches and indicators

Six push buttons total, four user controlled

Seven LEDs total, four user controlled

Connectors

HSMC

USB Type B

Cables and power

USB cable

External power supply (U.S. compatible plug with EU and UK adaptors)

Cyclone III FPGA Starter Kit CD-ROM

Example designs targeting the Cyclone III FPGA starter board

Create an FPGA design in one hour

Power measurements of a Cyclone III FPGA

A 32-bit soft processor system inside an FPGA

Complete documentation

User guide

Reference manual

Board schematic and layout

Bill of materials

Product and partner information

Download instructions to receive the latest version of the following software (at no charge):

Quartus II Web Edition (FPGA design software)

ModelSim-Altera Web Edition (FPGA simulation software from ModelSim)

Nios II Embedded Design Suite, Evaluation Edition (32-bit microprocessor software)

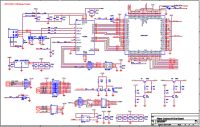

下图为Cyclone III FPGA入门板的方框图和部分电路图:

http://www.altera.com/literature/manual/cycloneiii_sb_3c25.pdf