超高速快速傅里叶变换(FFT)内核是任何实时频谱监测系统的必要组成部分。随着各频段无线设备数量的迅速增长,系统必须相应加强对带宽的监测。因此,这些系统需要以更快的速度将时域转换为频域,这就要求进行更加快速的FFT运算。实际上,大多数现代监测系统往往需要使用并行FFT,实现数倍于尖端FPGA(例如赛灵思Virtex®-7)最高时钟频率的采样吞吐量,充分发挥宽带A/D转换器的优势,其可轻松获得12.5Gsps甚至更高的采样率。[1]

同时,随着通信协议日益数据包化,监测信号的占空比在不断降低。这种情况要求大幅度降低扫描重复时间,这就需要使用低时延FFT内核。并行FFT也能在这方面有所裨益,因为时延会随着采样率与时钟速度之比成比例下降。

鉴于所有这些原因,本文将深入介绍可在运行中配置转换长度的并行FFT(PFFT)设计,并说明使用并行FFT可实现的吞吐量和利用率。

FFT的硬件并行化

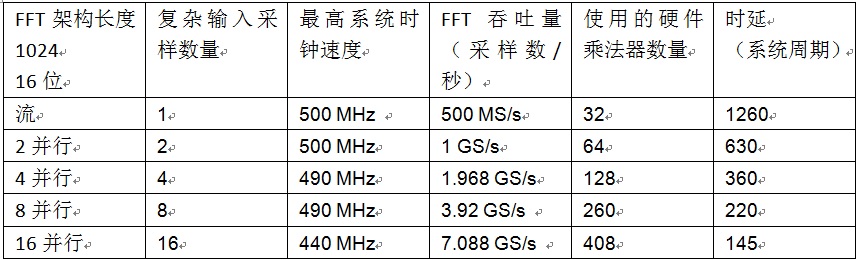

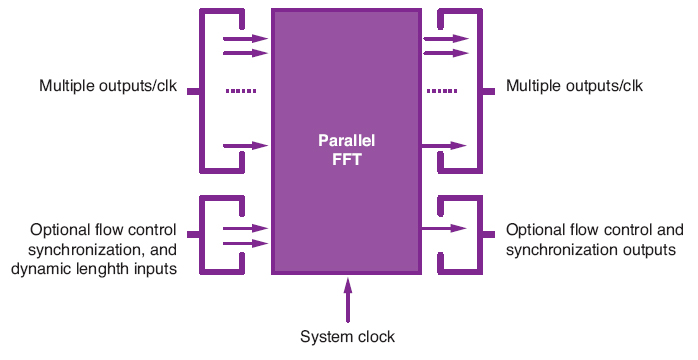

由于在逻辑中直接实现FFT较为复杂,因此大量硬件设计人员使用各个厂商提供的现成FFT内核。[2]但是,大多数现成的FFT内核使用“流”或者“模块”架构,每个时钟周期只能处理一个或者几个采样,这就会把吞吐量限制在FPGA或者ASIC器件所能提供的最大时钟速度内。PFFT能够提供速度更快的架构。PFFT每个时钟周期可接受多个采样,进行并行处理,并在每个时钟周期内输出多个采样。这种架构可让吞吐量达到器件最大时钟速度的数倍,但代价是增大了占位面积并提高了复杂性。因此,要使用PFFT必须在吞吐量和面积之间进行权衡。典型Virtex-7 FPGA设计所需的权衡方案见图1和表1。

在Virtex-7器件上实现并行FFT的典型性能和面积权衡

表1 - 面积的增加因硬件乘法器的使用造成。吞吐量提升与占位面积之比略高于线性关系,总体而言非常适用于将吞吐量增加至数千兆赫兹采样率。

从权衡的角度,可从表中看出一些普遍特点:

1. 随着并行吞吐量的增加,乘法器(面积)的使用也在增加,但增加的速度稍低(好于线性关系)。

2. 随着并行量的增加,系统时钟速度和时序收敛速度的下降会导致吞吐量的提升低于线性关系。不过在现代FPGA上这种劣化现象正在减轻。

3. 鉴于上述两个原因,吞吐量增长与面积增长的比率总体上要高于线性关系。

4. 时延随着并行化的增大而降低。

请注意表1中的测量值只适用于特定的对象和FFT配置。这种情况针对的是长度为1024的情况,且具有16位输入、动态长度可编程(最小可编程长度为4)和流控制。流控制对频谱监测这样的应用而言非常重要,因为,这类应用往往需要在进行采集等其它操作时,使用旁通道信息来改变FFT大小(以改变分辨带宽)或暂停FFT的运行。从理论上说,您可以通过在转换操作前插入缓存的方式来实现流控制。但是对于频谱监测这样的采集驱动型操作而言,难以提前计算出所需要的缓存大小,这样就必须采用容量大、速度快的高成本内存条。

实现架构

虽然实现FFT的方法多种多样,但并行版本的Radix2多路径延迟换向器内核(Radix2-MDC)[3] 作为一个模块化方案在这里非常适用,可用于创建在先进FPGA器件中具有良好扩展能力的可配置并行FFT内核。Radix2-MDC是一种用于创建各种长度流水线FFT的典型方法,图2a是长度为16的FFT。它将输入序列分解为两个并行数据流,并在数据流向前流入蝴蝶算法单元(FFT算法的一个子元)的过程中采用恰当的延迟对数据元进行调度,以确保数据元之间保持恰当的“间距”。如图2b所示,使用较宽的数据路径和矢量运算,Radix2-MDC的并行化就会相对容易。MDC的结构还便于实现流控制和动态长度重配置,相反,单路径延迟反馈(SDF)结构因为加入了流控制(停止)信号,会显著降低最大吞吐量。

图1 - 并行FFT一次可处理多个采样,使吞吐量超过目标器件可实现的系统时钟速率。可选特性包括流控制、同步和动态长度可编程功能。

另一个会影响可扩展性的因素是复杂乘法器的选择,即选择4乘(4M)还是3乘(3M)结构。选择3M复杂乘法器可以减少设计的占位面积,但代价是会降低时钟速度。[4]这方面的权衡也主要依赖于FPGA器件的DSP硬件部分。下面是我们即将介绍的案例研究所使用的最重要的参数和选择:

l 长度=1024

l 输入精度=16位

l 使用4乘5加复杂乘法器的Radix2-MDC架构

l 数据路径精度=每级增加1位(对1024长度为10级/位)

l 包含动态长度可编程功能

l 启用可选的流程控制和同步功能