以之前对电阻噪声的讨论为基础,这次让我们一起学习放大器噪声的一些基本知识。对于低噪声应用来讲,同相放大电路是最常见的,因此我们将主要探讨同相运算放大器。 如图1所示,将输入源等效为一个电压源与一个电阻串联,我们知道源电阻RS的噪声与其电阻平方根值是成正比例关系的(如图2中的直线所示)。低噪声放大器的设计目标是在电阻引入噪声的基础上,尽可能少地引入运放附加的噪声。

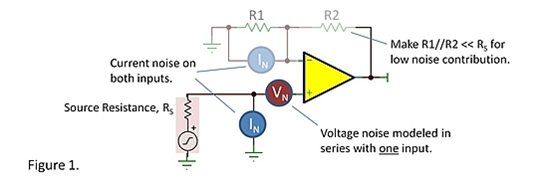

如图1所示,放大器噪声的等效模型为在一个输入端串联一个电压噪声,同时在两端分别连接一个电流噪声源。把电压噪声看作失调电压的时变元件。同样,电流噪声是输入偏置电流的时变元件,在每个输入端各有一个。由于我们总能将反相输入端的电流噪声值降到最低,因此我们将忽略它。

图2给出了BJT做为输入级的OPA209和JFET做为输入级的OPA140这两个运算放大器电路的总输入参考噪声的曲线。在25°C的时候,两条曲线均与源电阻的噪声成比例关系。对每个运算放大器而言,都通过平方和的均方根的方式来对三种噪声源进行了一个求和。你也许会在某些运算放大器的数据手册上看到这样的图形。

当源电阻阻值减小时,它的约翰逊噪声随之减小(由阻值平方根值的倒数决定),在一定程度上,放大器的噪声电压将起到主导作用。总的噪声将等于放大器的电压噪声。当源电阻阻值增加时,流过源电阻的电流噪声将线性增加,而且会增加很快且最终会超过源电阻的噪声。因此当源电阻阻值很高时,电流噪声将会起主导作用。

当源电阻值为2kΩ或者更低时,低噪声放大器的设计会遇到最大的挑战。较低的源电阻噪声就要求放大器有很低的噪声电压。双极性(BJT输入)放大器通常在这方面比较擅长。还需注意的是,如图2所示,在一个最佳位置, OPA209的总噪声与源电阻噪声几乎相等。源阻最佳噪声性能发生在RS=VN/IN。

当源电阻阻值大约为20kΩ时,FET输入的放大器几乎不会引入任何的额外噪声。只有当源电阻阻值达到几个GΩ的时候,FET运算放大器的电流噪声才会产生影响。可以遵循以下准则:当源电阻阻值小于10kΩ时,低噪声的BJT放大器会产生较低的噪声。当源电阻阻值大于10kΩ时,FET或者CMOS的运算放大器才会可能会有优势。

反馈网络中的R1和R2也会产生一定的噪声,但通常情况下是可以忽略的。当R1和R2的并联值小于或者等于RS值的十分之一时,它们将仅仅使总噪声的值产生小于10% (<1dB) 的增量。无论这些电阻的比值是多少,这都会是个事实。在图2中,反馈网络中元件的噪声被设定为零。

当然,还有很多需要了解的,如想了解更多,我推荐我的同事Art Kay写的一本书“Operational Amplifier Noise: Techniques and Tips for Analyzing and Reducing Noise”。

思考点:OPA140在10kΩ 之上有一个非常宽的电阻范围,在这个范围之内,噪声性能很好。是否存在一种方法可以使得较低的源电阻值可以达到同样的效果?

感谢阅读并且欢迎给出建议。