文献标识码: A

文章编号: 0258-7998(2014)08-0044-04

随着科学技术的高速发展,高速处理器、多媒体以及网络技术等要求传输的数据量越来越大,需要的传输速度越来越快,尤其是现在许多设备要求具有长距离传送数据的能力,以确保可以传输千米以上的距离[1]。普通的并行总线由于自身的劣势,无法适用于长距离数据传输的系统中。

基于串行器/解串器构架的LVDS解决方案具有使用简单、传输速度高、抗干扰能力较强和使用节点少等特点,因此可以采用该方案来实现远程高速数据传输功能[2]。但在一些恶劣的环境(如超远距离或高干扰环境)中,LVDS数据仍然可能出现信号衰减或严重失真。基于此,本文给出了一种针对LVDS远程传输的延展卡的设计方案,将双绞线传输和光纤传输相结合,使数据传输距离可达几千米远。

1 系统方案设计

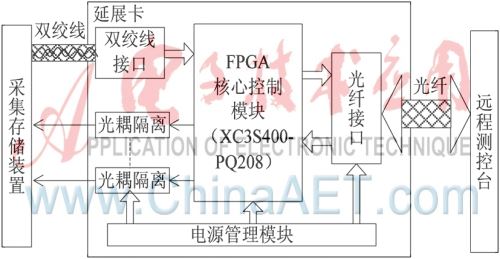

设计要求信号以400 Mb/s的速度传输2 km以上的距离。根据设计需求和方案合理性,采集存储系统到延展卡之间采用100 m双绞线通信,延展卡与远程测控台之间采用2 km光纤通信。总体设计如图1所示,分为FPGA核心控制模块、双绞线接口模块、光纤接口模块、光耦隔离模块、电源管理模块等几部分。系统指令由光模块接收,并通过光耦隔离并行发出;数据由双绞线传输并通过光模块转发。

图1 系统总体设计

2 硬件设计中的关键点

2.1 双绞线接口设计

双绞线传输伴随着信号大幅度衰减。图2中波形1为一组随机LVDS信号通过100 m电缆传输后的波形。显然有部分电平越不过零点门限,在接收端加上电缆均衡器CLC014,将之与SN65LV1224搭配使用,可以解决这个问题。CLC014最大可以均衡120 m的第五类未屏蔽双绞线。

图2 无均衡器时波形(上)与加均衡器后波形(下)

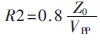

如图3所示为添加均衡器后的双绞线接收模块电路,R1和R2为匹配电阻,可参照公式

计算阻值。本系统双绞线特性阻抗Z0为100 Ω,R1、R2的阻值根据输出电平调整为25 Ω。隔直电容C1的容值为0.01 μF,为经双绞线衰减后的信号提供交流耦合。CLC014的输出取自输出晶体管的集电极,由正电源通过二极管和50 Ω的电阻建立PECL电平,从而获得理想的输出波形。电阻R3为媒质终端匹配电阻,阻值为100±20 Ω,用于防止信号在媒质终端发生反射,减少电磁,布局时要靠近接收器输入端放置。图2中波形2为增加均衡器之后的信号波形,可见波形恢复正常,高低电平明显。

图3 双绞线接收

2.2 光纤接口设计

光模块选用OCM3723,其输入信号电平范围为1.5~2.3 V,而LVDS串化器SN65LV1023的输出幅值约800 mV,所以需要增加驱动器CLC006,将信号增强到2 V之后再输入光模块。接收命令时,解串器SN65LV1224与均衡器CLC014搭配,将光模块输出的命令信号重新组构,并恢复其强度。光纤接收与发送部分电路如图4所示。

(a)光纤接收

(b)光纤发送

图4 光纤接收与光纤发送电路

OCM3723属于LVPECL接口电平,而CLC014和CLC006属于PECL接口电平,所以采用交流耦合方式连接。PECL/LVPECL的输出共模电压需固定在VCC-1.3 V上,直流偏置电阻需提供14 mA到地的通路,所以R4=(VCC-1.3 V)/14 mA,当VCC=3.3 V时,R4=142 Ω,应用中为了让输出波形达到最佳,R4可以从142 Ω~200 Ω之间选取。PECL/LVPECL输入直流偏压要固定在VCC-1.3 V上,输入阻抗应等于传输线路阻抗,可列出方程 =VCC-1.3 V且R5||R6=50 Ω,当VCC=3.3 V时,R5=82 Ω,R6=130 Ω。因为CLC014输入和CLC006输出在其芯片内部有偏置电路,所以无需设计外部偏置网络。

=VCC-1.3 V且R5||R6=50 Ω,当VCC=3.3 V时,R5=82 Ω,R6=130 Ω。因为CLC014输入和CLC006输出在其芯片内部有偏置电路,所以无需设计外部偏置网络。

光纤发送端和接收端数据波形如图5所示。可以看出通过2 km光纤之后,信号波形仍然比较标准。对比双绞线端接收的数据波形,不难发现光纤比双绞线的传输效果好很多。

(a)光纤发送端 (b)接收端

(横轴坐标为50 ns/格,纵轴坐标为500 mV/格)

图5 数据波形

2.3 光耦隔离接口设计

因为系统指令切换的频率较数据传输的速率低得多,所以为了简化电路,增加指令传输的可靠性,经过FPGA重组后的指令由5条并行线传输。指令接口部分采用高速10 MB/s光电耦合器HCPL-2631进行电气隔离,6.3 mA电流即可导通工作,双通道单向传输,真正实现前后级互不干扰,提高了接口的可靠性。图6所示为HCPL-2631的单路传输接口电路。当FPGA接口为逻辑0时,HCPL-2631内部电路导通输出低电平;当FPGA接口为逻辑1时,HCPL-2631内部电路不导通,输出高电平。

图6 光耦隔离接口电路

3 逻辑设计中的关键点

3.1 防止指令误判

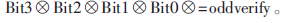

为了防止接收端指令的误判,首先对指令进行奇校验。设计时将指令中1的个数定为奇数个。接收指令的奇偶性判断是通过对指令的各个数据位进行异或操作(XOR)实现的,即:

只有当oddverify为1时,才认为当前传输的是有效指令,并用5位数组f_state重新定义当前指令[3]。新定义的f_state指令信号需再经过双重计数器消抖才能最终输出。外部计数器对所有有效指令进行消抖计数,而内部计数器针对某一个指令进行消抖计数,消抖后的state指令为最终的5线指令。

图7所示为部分指令判别的时序仿真图。从图中可以看出,“0110001111”经过奇校验后被过滤,指令切换时出现的误指令“0101100110”被外部计数器隔断,之后传输中的误码指令“0110011111”也被内部计数器过滤。

图7 指令判别时序仿真图

3.2 LVDS接口时钟与采集速率匹配问题

LVDS接口时钟是固定的,而采集设备的采集速率根据需求可控,二者速度不匹配,所以数据链路中经常出现传输空白;如果数据采用间歇式传输,则LVDS芯片中断后再同步会有500 μs的数据丢失。

针对这一问题,设计中引入无效数与有效数交替发送的模式。当链路中无数据传输时,FPGA自编译无效数据,使链路保持通信状态。LVDS芯片有10位数据管脚,有效数据占用了其中的低8位,高2位作为区别有效数和无效数的标志位。定义“01”为有效数标志,“00”为无效数标志。实验证明无效数发送“00011111”同步稳定性高,原因可能是“00011111”配合标志位“00”正好构成同步码“0000011111”,而LVDS芯片同步的过程就是不断识别同步码的过程。所以这样不但解决了速度匹配问题,也提高了系统数据链路的可靠性。

3.3 光纤接口LVDS失锁问题

光模块与LVDS接收模块之间连续传输“FF”数据出现失锁,表现为SN65LV1224的锁存标志LOCK出现高电平脉冲。经分析,交流耦合电路中的耦合电容隔断了信号的直流分量,因此LVDS接收端只能观察到输入信号的前后沿。当数据1连续出现时,电容会造成接收端电压下降,信号产生抖动[4]。所以连续传输“FF”数据容易造成LVDS失锁。一种高效的解决办法是使用8B/10B编码实现直流平衡,或者选用带有8B/10B编码的串/并转换芯片[5]。为了配合前端逻辑设计,同时考虑到只有传输“FF”时才会出现失锁的情况,本设计中采取的优化措施是将“FF”数据转变为“1F”数据发送,即将二进制8位数据“11111111”转变为“00011111”发送,且高两位标志位定义为“10”,发送的10位LVDS数据为“1000011111”,这与同步码数据近似。光纤数据链路中共有3种数据类型,图8为优化后的数据编码发送流程图。经过大量测试,优化后的数据编码方式能够有效解决LVDS失锁的问题。

4 试验方法与测试

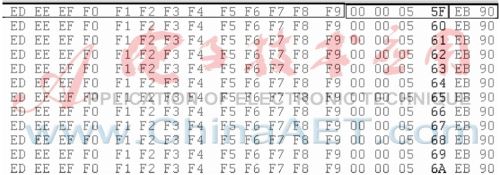

针对总体设计方案,配合数据采集存储装置和远程测控台,对系统进行恶劣环境下数据传输的性能测试,双绞线长度为100 m,光纤长度为2 km。采集存储装置启动自发数模式,测试数据帧格式为:1~250 B是0~249的递加数,251~254 B是32 bit二进制帧计数,255~256 B为同步字EB 90。图9所示为上位机接收到的部分数据截图,帧结构严格对齐。采用上位机分析软件对数据进行分解,分解报告显示传输数据无误码,无丢帧。

图9 测试数据部分截图

基于LVDS技术的远程数据传输延展卡的设计充分发挥了双绞线、光纤以及光电耦合器的接口传输优势,并且解决了速度匹配和光纤接口LVDS芯片易失锁的问题,有效保证了指令的可靠下发以及数据传输的准确性,成功将数据传输距离扩展至几千米远。该卡抗扰能力强,传输稳定性高,为高速数据超远距离传输开辟了新的领域。

参考文献

[1] 刘利生,苏淑靖,张凯琳.基于LVDS的远程数据传输系统[J].仪表技术与传感器,2011(12):38-39.

[2] 姚永兴,焦新泉,马培娇.高可靠性远程数据传输系统设计[J].计算机测量与控制,2011,19(8):1968-1971.

[3] 刘欣,张会新.基于LVDS总线的分布式数据综合器测试系统[J].科学技术与工程,2013,13(34):10354-10358.

[4] 刘泳锐,张彦军,刘龙飞.8b/10b编码实现LVDS交流耦合传输中的直流平衡[J].科学技术与工程,2012,12(35):9693-9696,9701.

[5] 何林飞,田佳月,张晓林.基于光纤传输的多路高速数据采集系统[J].电子技术应用,2013,39(3):77-79.

(收稿日期:2014-03-27)

作者简介:

甄国涌,男,1971年生,副教授,硕士生导师,主要研究方向:测试系统集成技术与应用软件技术。

瞿林,男,1989年生,硕士研究生,主要研究方向:电路与系统、高速数据采集。

刘东海,男,1982年生,硕士研究生,主要研究方向:高速数据采集。