摘 要: UTMI定义了USB2.0底层信号的物理约束,为实现USB2.0高速(480 Mb/s)通信提供了可靠的保障。实现了协议中串/并转换、位填充/剔除、非归零编解码等内容,并在SMIC 0.13 ?滋m CMOS工艺库下完成了收发器电路设计。仿真结果显示,该收发器设计功能正确,满足协议要求。

关键词: USB2.0; 收发器; UTMI

通用串行总线USB(Universal Serial Bus)以其简单易用、连接灵活、高带宽等特点已经成为计算机连接外部设备最常用的一种方式[1]。如今,越来越多专用集成电路(ASIC)和嵌入式系统都内置了USB接口。很多公司采用其他公司生产的收发器(USB2.0 transceiver)IP核,再配合其他自行设计的电路模块来进行相关产品的开发。本文在SMIC 0.13 ?滋m CMOS工艺下采用Verilog HDL描述电路,通过仿真、综合、布局布线等流程完成收发器电路设计。

1 UTMI整体结构

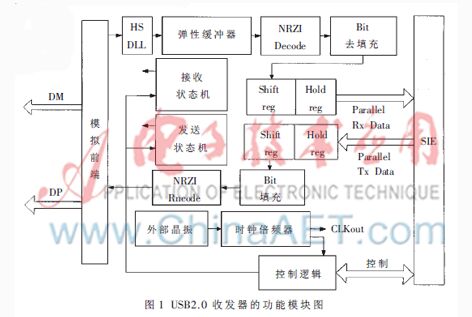

USB收发器在USB总线中的位置处于各种USB设备与USB总线的接口处。它的作用是处理USB物理层的协议和信号,其中接收部分接收USB总线上的串行数据,经过NRZI(Not Return to Zero Inverse)编码、“0”比特剔除,最后转成并行数据后交给串行接口引擎SIE(Serial Interface Engine);发送部分完成相反的操作,接收SIE的并行数据,经过并/串转换、“0”比特添加、NRZI编码后发送给USB总线[2]。

图1所示为USB2.0收发器的功能框图,主要完成的功能为:

(1) 支持480 Mb/s高速、12 Mb/s全速两种不同的数据传输速率。

(2) 同步字包头SYNC(Synchronization)/包尾EOP(end of Packe)产生和检测、比特填充/去填充、比特填充错误检测、非归零编码等。

(3) 能够在高速和全速终端/信号之间切换,支持USB2.0测试模式。

(4) 支持USB协议中唤醒、挂起检测、恢复逻辑等检测。

从中可以看出,收发器是一块具有一定复杂度的数/模混合电路。设计时将数字电路和模拟电路分开,分成以下三部分:

(1) 数字逻辑部分。该部分完成串/并、并/串转换,比特填充/去填充以及相应的发送与接收状态机等协议的逻辑功能,这也是本文所要阐述的电路设计内容。

(2) 时钟产生与数据恢复电路。其功能是产生本地高速时钟,并从USB总线的串行数据流中恢复出时钟和数据,以便于后级电路进行相应的操作。

(3) 发送与接收接口部分电路。USB总线有比较严格的电气特性要求,比如USB高速信号是±400 mV的差分信号,对地电阻为45 ?赘,还有电缆断连检测、squelch检测等,这些电气特性要求均由模拟接口电路实现[3]。

2 模块设计

2.1发送电路模块

根据UTMI规范的功能要求,USB收发器的发送部分应该包括并/串转换、比特“0”填充、非归零编码以及发送控制状态机四部分。四部分的关系如图1中发送部分(Tx)所示。

比特“0”填充规则为:对发送的串行数据进行“111111”序列检测,每检测到6个连续的“1”序列后,在该序列后插入一个比特“0”。NRZI编码规则为:逻辑“1”用电平的不变来表示,逻辑“0”用电平的翻转来表示。比特“0” 插入与NRZI编码配合使用,可以有效防止传输的数据中出现连续的没有电平变化的序列,避免导致接收部分PLL(Phase Locking Loop)时钟失锁的情况出现。

串行数据中插入填充比特,会使发送的数据多于要发送的数据。为了平衡比特插入前后的数据个数偏差,设计时在串行数据中每插入8个“0”后,使发送状态机输出TXready为低电平,让SIE等待一个时钟周期,即8 bit串行数据的时间(因为SIE的时钟为60 MHz,串行数据速率为480 MHz。8 bit串行数据的传输时间正好等于一个并行数据的传输时间)。在本文的电路设计中,比特“0”插入操作使用了两个计数器,其中一个对串行数据中连续“l”进行计数,用来检测“111111”序列;另一个对已经插入到串行数据的“0”进行计数,这两个计数器都采用移位计数器来实现。发送电路比特填充和数据平衡的实现如图2所示[4]。

![XJ}~_CG[~F{D[DZ8]RH@D82.jpg XJ}~_CG[~F{D[DZ8]RH@D82.jpg](http://files.chinaaet.com/images/2015/05/04/6356635012356800007547228.jpg)

发送部分的状态转移图如图3所示。复位进入Reset态,复位结束后进入TX Wait态等待TXValid信号的到来,当收发器接收到SIE发送数据的指令时(即TXValid信号为高电平),进入Send SYNC态,发送电路开始发送传输数据包的包头,即同步字SYNC。全速数据包的SYNC字为8 bit的“KJKJKJKK”序列,高速数据包的SYNC字为32 bit的“KJKJKJK…JKJKJKK”序列,序列中的“K”对应于USB差分信号“DP逻辑低电平,DM逻辑高电平”的总线状态,序列中的“J”对应于 “DP逻辑高电平,DM逻辑低电平”的总线状态。同步字发送完成之后,进入Data Load态且置TXready为高电平,收发器开始从SIE读取8 bit的并行数据到Hold Reg中,当Hold Reg中的数据没有被shift reg读取时,状态机将会跳转到Data Wait态;当shift reg中的数据做完并/串转换, Hold Reg中的数据会被shift reg读取,此时状态跳转到Data Load态。当收发器检测到SIE停止发送数据的指令(TXValid信号为低电平),状态机进入Send EOP态,开始发送EOP数据且置TXready为低电平, 全速数据包的EOP为总线上2 bit的“SE0” (“SE0”对应于USB差分信号“DP和DM均为逻辑低电平”的总线状态)状态以及其后1 bit的“J”状态,高速数据包的EOP为8 bit的“01111111”数据序列,这个数据序列没有像正常发送过程的数据一样进行比特“0”插入操作,以便区别于一般的数据。当EOP发送完,状态机进入TX Wait态,否则停留在Send EOP态继续发送EOP数据。

2.2 接收电路模块

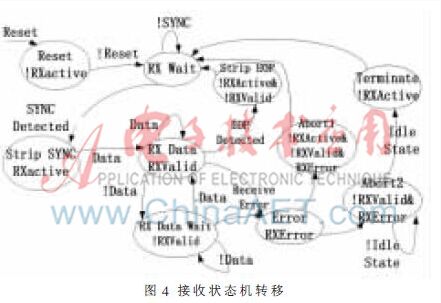

收发器的接收电路与发送电路相反,将数据从总线上的差分信号中提取出来,交给USB SIE进行后续的协议处理。这部分电路包括NRZI解码、比特“0”去除、串/并转换以及一个接收状态机。这部分的相互关系如图1中接收部分(Rx)所示。接收部分的状态转移图如图4所示。

复位进入Reset态,复位结束后进入RX Wait态,开始同步字SYNC检测,若未检测到同步字,则在原状态循环;当检测到同步字后进入Strip SYNC态,同时使 RXactive 有效,由于高速SYNC有32 bit,所以在Strip SYNC态会维持数个时钟周期。当SYNC检测完毕并抓到第一个字节后,跳转到RX Data态。由于去比特填充造成数据速率的下降,使得状态在RX Data和RX Data Wait之间跳转,每次去掉8个填充位后,状态机跳到RX Data Wait态,同时拉低RXvalid信号。

当检测到错误时,进入Error态,如果此时数据线DP和DM上已经没有数据传输了,则进入Abort1态,再直接跳转到RX Wait态;如果此时数据总线DP和DM上还有数据在传输,则跳转到Abort2态,直到数据总线上的数据传输完才跳到Terminate态,再直接跳转到RX Wait态。

去比特“0”填充的过程就是将发送过程中插入到数据包的“0”比特从数据包中去除,也就是将数据包中“1111110”序列中的“0”去除,以恢复出正确的数据。这里同样需要进行数据平衡,通过RXValid信号来实现。接收电路去比特的实现如图5所示。

![O@U3SX~G[5R]M3T20IPKZCD.jpg O@U3SX~G[5R]M3T20IPKZCD.jpg](http://files.chinaaet.com/images/2015/05/04/6356635016354300005500018.jpg)

3 仿真及验证

发送数据时,UTMI置drive_enable为低电平,以使驱动器处于发送状态。当TXValid为高电平时,表明并行数据线上有数据等待发送。UTMI首先发送同步字SYNC,然后读取并行数据线上的数据到Hold Reg中,完成串/并转换后依次进行位填充和NRZI编码,再把数据发送到数据总线上(即DP和DM)。完成1 B的发送后,UTMI应该置TXReady为高电平,表明 UTMI可以继续发送下一个字节。数据发送完成后,UTMI应该继续发送EOP信号, 表明1个数据包发送完毕。高速模式下的部分发送波形如图6所示。

![G}1B`E2A@}]D%MGNFD9%])A.jpg G}1B`E2A@}]D%MGNFD9%])A.jpg](http://files.chinaaet.com/images/2015/05/04/6356635018654900001260161.jpg)

接收数据时,UTMI首先匹配SYNC字段。匹配完成后,系统进入接收数据状态,此时RXActive为高。UTMI对接收到的串行数据进行NRZI解码,剔除填充位(此时drop_bit为高),送到转移寄存器和保持寄存器,满8位后输出到并行数据线(此时RXValid为高)。UTMI检测到EOP以后,拉低RXActive,表明接收完一个数据包。高速模式下的部分接收波形如图7所示。

将此设计在SMIC 130 nm CMOS工艺下进行综合,布局布线,可满足UTMI协议中480 Mb/s的数据率要求。经仿真验证分析,该设计符合UTMI接口协议,正确实现了收发器逻辑电路的功能。

本文结合UTMI协议,对USB2.0收发器整个体系结构和工作原理进行了分析。完成了USB收发器逻辑电路的设计,满足协议要求。仿真结果表明,所设计的收发器功能正确,适用于USB系统开发。

参考文献

[1] 黄菁,刘青春. 通过 USB 接口控制数/模转换器的电路设计[J].微型机与应用, 201231(14):27-30.

[2] Intel Corporation.USB2.0 Transceiver MacrocellInterface(UTMI)specification[S].Version 1.05,March 29,2001.

[3] Compaq, Hewlett-Packard. Universal serial bus specifica-tion[S]. Revision 2.0, April 27, 2000.

[4] Huang Kai. A multiprocessor prototype and its SoC designmethodology[J]. DianziXuebao (Acta Electronica Sinica), 2009(2):305-311.