摘 要: 首创一种新型的脑电检测技术。将多路ERP脑电信号分别经各自的前置放大电路、模/数转换电路进行采样和A/D转换,形成多路并行数据流,最后经数据汇集装置汇集成一路高速串行数据流,再经光纤介质传输到计算机进行分析处理。采用该技术的脑电检测装置可以满足对多路ERP脑电信号同时进行高速率(10 kHz每通道)、高精度(24 bit)采样的要求。软硬件测试表明,该装置具有稳定性好、抗干扰能力强、频带范围宽等特点。

关键词: 脑电检测; ERP脑电信号; 前置放大; 信号采集; 数据汇集

脑电信号是人类最早研究并应用于临床医学的生物电信号之一,对它的分析在提高脑部疾病诊断效率和准确性方面有着十分重要的意义。脑电图(EEG)是通过把电极放到头皮或大脑皮层上运用脑电采集仪记录到的脑部生物电活动的波形图,脑电信号主要频率在0.5~100 Hz,信号幅值范围为5~300 μV[1]。事件相关单位(ERP)是一种特殊的脑诱发电位,主要用于对大脑高级心理活动(如认知过程)作出客观评价,ERP脑电信号的主要频率在0~2 kHz,信号幅值范围为零点几微伏到几微伏。这就要求ERP脑电检测装置拥有更宽的频带将慢波细节描述得更清楚,同时需要具有更强的噪声抑制能力。目前国内脑电图检测技术已经相对成熟,但是ERP脑电信号检测装置还要依靠国外进口,价格昂贵,所以尽快研制出价格便宜、性能优越的ERP脑电检测系统是当务之急。

由于微伏级ERP脑电信号相当微弱,很容易被毫伏级外界干扰和内部噪声所淹没,将ERP脑电信号放大的同时也不可避免地将干扰信号放大。要想在16 bit以下的采样系统中分辨清楚,就必须至少放大1 000~ 10 000倍,而这样干扰信号又会使放大器饱和。此矛盾在常规的放大器中难以解决。有效的解决方案是减小放大倍数同时提高A/D转换的精度,经过计算采用24 bit的转换精度,放大倍数只要5~10倍就能满足要求。大的干扰信号可以在采样经A/D转换后通过数字滤波的办法来去除。

但是,提高采样精度又带来新的问题。现有的高精度A/D采样芯片大都是∑-⊿型的,它是通过过采样方法牺牲采样率来实现高精度的,因此采样率不高。

常规数字化脑电图仪是将由电极线引入的多路脑电信号先分别进行模拟放大和滤波,然后经过模拟开关分时切换,形成一路模拟信号进行A/D转换,再把转换后的数据通过各种通信介质传送到计算机中进行处理。对于每个通道4 kHz的采样率,即使按照16个通道计算,一片A/D转换器的采样率也要达到64 kHz,这对于24 bit精度的∑-⊿型A/D转换器是无法做到的。同时,∑-⊿型A/D转换器在进行高精度转换时,要求输入的模拟信号必须是同一路连续不断的,不能经过开关的切换。因此现有的常规数字化脑电图仪并没有同时解决好对多路ERP脑电信号进行宽带宽(0~2 kHz)、高精度(24 bit)、高采样率采样的问题。

本文提出了一种全新的技术方案[2]。并且应用此方案研制了一款70通道、每通道采样率高达10 kHz、带宽为0~2 kHz、采样精度达24 bit的ERP脑电检测装置,较好地解决了技术背景中描述的问题。

1 系统电路设计

1.1 系统整体方案设计

本文提出一种硬件与软件结合的ERP脑电检测方案,由前置放大电路、模/数转换电路、数据汇集电路、数据传输装置、计算机等部分组成[3]。先分路进行高频率采样和高精度A/D转换,每路用一片成本较低的24 bit A/D转换芯片ADS1251进行10 kHz的采样和A/D转换。然后用一种高速的汇集电路将各分路转换后的数据流按照一定的帧结构汇集成一路高速的数码流,再经过光纤隔离并通过USB2.0接口传输进入电脑进行分析和处理。系统整体设计框图如图1所示。

这种ERP脑电信号采集技术可以在不加入50 Hz工频陷波器的条件下有效地抑制50 Hz工频干扰,可应用于70导台式/便携式ERP脑电检测系统。

由于本方案中的A/D采样只是针对一路的模拟信号,因而可以采用低成本高精度的∑-⊿型A/D转换器,使得每一路信号在高频率(10 kHz)采样时的转换精度都能达到24 bit。采用传统方案是无法实现的。

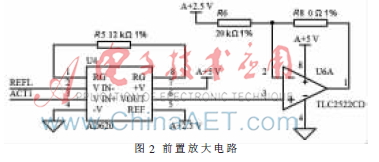

1.2 前置放大电路设计

ERP脑电信号首先通过贴在人体头皮上的电极引入到前置放大电路,伴随着脑电信号会有很多干扰和伪迹,这些无用信号往往比有用的脑电信号大几百甚至上千倍。这就要求前置放大器既能放大ERP脑电信号又有抑制干扰信号的能力[4]。因此选择了高共模抑制比和高输入阻抗的仪表放大器AD620。为了不让干扰信号将放大器饱和,就要使放大器处于低增益状态,放大倍数被控制在5~10倍。这样可以使输入信号的动态范围扩大到±300 mV。前置放大电路如图2所示。

1.3 抗混叠滤波电路设计

为了使后面的A/D采样电路工作在10 kHz采样率下满足抽样定理的条件,必须限制输入到A/D采样电路信号的频率范围。本文采用了一个二阶低通有源滤波电路,将输出信号的频带限制在0~2 kHz。抗混叠滤波电路如图3所示。

1.4 A/D转换电路设计

采用高精度的A/D转换来满足分辨微伏级信号的要求,每路各采用一片低成本高精度的∑-⊿型A/D转换器ADS1251来进行模/数转换[5]。这样就避免了模拟信号的通道间切换给∑-⊿型A/D转换器带来的致命影响。因此可以使每一路的采样率达到10 kHz的同时转换精度能达到24 bit。

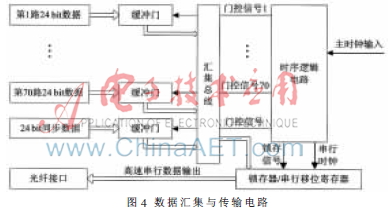

1.5 数据汇集与传输电路设计

由于本文是对多路ERP脑电信号分别进行高速采样和高精度A/D转换,因而会同时产生多路高速的数据流。这些大量的多路数据必须按照一定的数据格式形成一路更高速度的数据流才可以方便地输入计算机进行处理[6]。本文采用一种高速数据汇集电路,将70路转换后的数据汇集成一路高速的数据流,同时插入同步信息,经过光纤隔离电路再通过USB2.0接口传输给上位机,完成采样数据的接收和控制命令的下发。该部分电路是这一新型ERP脑电检测技术得以实现的核心电路,电路框图如图4所示。

2 测试结果比较分析

2.1 基于VC++测试平台的设计

本文采用基于VC++的软件测试平台进行电路性能参数测试。该平台以软件的方式代替硬件,方便修改、维护和添加新功能,具有极强的灵活性。程序有通道选择(1~70通道)、低通/高通滤波、50 Hz工频陷波、波形显示等功能。

2.2 系统测试分析

测试项目包括电压、通频带、噪声电平、共模抑制比、共模电压输入范围、差模电压输入范围、采样率、分辨率等测试。

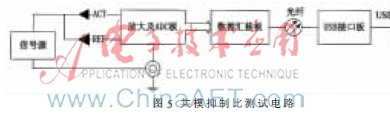

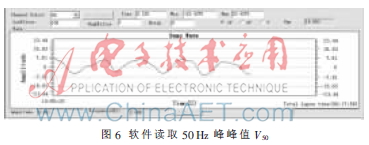

共模抑制比测试电路如图5所示。将信号源地与放大器地连接,放大器两个差分输入端(ACT与REF)短接并与信号源输出连接,运行测试程序进行采样,关闭软件50 Hz陷波,信号源输出2 V/50 Hz信号,读取对应的50 Hz峰峰值V50为14.583 μV,如图6所示。根据公式CMRR=20log(2/V50)计算出共模抑制比为102.7 dB。

在测试噪声电平时,将输入端对地短路,运行测试程序进行采样,低通滤波截止频率分别设定为10 Hz、100 Hz、1 kHz、2 kHz,读取对应的噪声峰峰值SVpp如图7所示。根据公式Srms=SVpp/6.6计算出有效值噪声Srms值。

经计算,低通滤波截止频率为10 Hz时,SVpp为0.395 V,Srms为0.06 V;低通滤波截止频率为100 Hz时,SVpp为1.622 V,Srms为0.25 V;低通滤波截止频率为1 kHz时, SVpp为6.942 V, Srms为1.05 V;低通滤波截止频率为2 kHz时,SVpp为9.324 ,Srms为1.41 V。

同理,测得电压精度为98.2%;通频带完全达到1~2 kHz(2 kHz电压幅度仅下降0.7 dB);差模输入范围为0~480 mV;采样率为10 416 S/s;放大器增益为8时的分辨率为0.037 ?滋V。

本文设计的ERP脑电信号采集装置成本较低, 针对每一路模拟信号真正实现了24 bit转换精度,从而可以大大降低前置放大器的增益,简化电路设计,大大提高了输入动态范围。针对每一路模拟信号真正实现了10 kHz的采样率,从而大大提高了所采集脑电信号的带宽,为脑电信号中高级认知电位(事件相关电位)分析提供了技术支持。混合在有用信号中的大幅度的干扰信号可以在转换后的数据中通过计算机软件处理的方法(如软件滤波和叠加平均)加以去除,从而提高抗干扰的效果,降低抗干扰的成本。

软硬件测试表明,系统稳定可靠。系统已经进入样机生产阶段,不久就能量产。

参考文献

[1] 聂能,尧德忠,谢正祥.生物医学信号数字处理技术及应 用[M].北京:科学出版社,2005.

[2] YAZICIOGLU R G, MERKEN P, PUERS R. A 200 μV eight-channel EEG acquisition ASIC for ambulatory EEG systems[J]. IEEE Journal of Solid-state Circuits, 2008,43 (12):3025-3038.

[3] 王三强.脑电信号采集系统设计及在脑-机接口中的应用研究[D].重庆:重庆大学,2006.

[4] 甘建伟,秦付军,王鹏. 基于FPGA的高速多通道数据采集系统设计[J].电子技术应用,2013,39(4):55-57.

[5] 朱岸青,陆裕奇,王会进.脑电监护分析系统的软件设计与实现[J].暨南大学学报(自然科学版),2007,28(1):56-60.

[6] 黄河涛,杜玉晓,董建.μV级脑电信号采集系统的关键技术[J].实验室研究与探索,2009,28(9):72-76.