创新 赋予Stratix 10超出想象的性能提升

2015-06-09

作者:王伟

创新,是Altera公司成功的因素之一,也是FPGA产品在多个领域备受关注的原因所在。就像Altera公司亚太区副总裁兼董事总经理Erhaan Shaikh所介绍的,微软宣布将使用Altera的FPGA产品来实现Bing搜索引擎的加速;2014年Intel的开发者大会上,Intel表示使用FPGA的产品配合实现CPU的加速;IBM和Altera将在OpenCL方面进行合作;Altera与中国移动研究院共同发展下一代5G网络,即5G-RAN……

Altera公司亚太区副总裁兼董事总经理Erhaan Shaikh

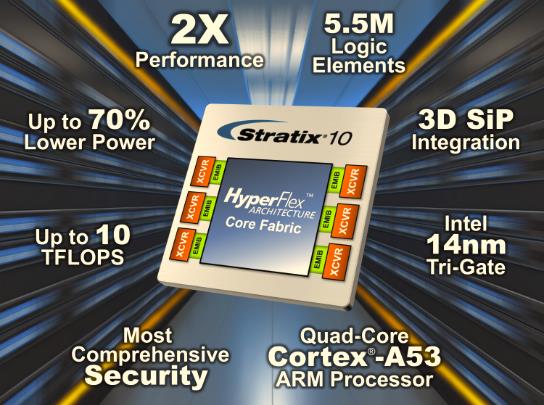

而Stratix 10,这一可编程世界中的又一个巨大突破,给我们带来的将是哪些改变?它与原有的28nm产品相比性能提高了2倍,这又是如何实现的?

Altera公司产品营销资深总监 Patrick Dorsey解答了上述疑惑:“Stratix 10之所以能实现这样的性能提升主要基于两大技术,一个是Intel 的14 nm三栅极技术,第二个就是Altera公司创新的HyperFlex架构。正是由于这两个大技术的使用,我们才实现了新一代产品性能的极大突破。”

Altera公司产品营销资深总监 Patrick Dorsey

HyperFlex:十多年来最大的FPGA体系结构创新,解决布线难题

在传统的架构当中,系统性能能否得到提高,很大程度上受制于实现连接的速度有多快。Patrick Dorsey表示:“布线延时是系统性能瓶颈的主要因素。通常我们采用的更宽的总线无异于饮鸠止渴,它绝不是解决问题的根本方案,反而会增加拥塞。要从根本上解决问题,我们就要从布线上寻求创新。”

HyperFlex体系结构解决了布线难题

HyperFlex体系结构的核心是“无处不在”,它在所有内核互联布线段上引入了寄存器,使得Stratix 10 FPGA和SoC能够受益于成熟可靠的性能增强设计方法,例如寄存器重新定时、流水线和其他设计优化方法。这些设计方法在传统的FPGA体系结构中是不可能实现的。HyperFlex体系结构帮助设计人员避免了关键通路和布线延时,其设计能够迅速达到时序收敛。内核逻辑性能提高2倍后,不需要很宽的数据通路,也不需要竞争体系结构由于其他偏移导致的设计结构,极大的提高了器件利用率,降低了功耗。HyperFlex体系结构支持高性能设计降低逻辑面积要求,功耗从而降低了70%。

异构3D SiP集成的新时代:单片FPGA内多个裸片封装

Stratix 10 FPGA和SoC系列的所有型号都采用了异构3D SiP集成技术高效经济的集成高密度单片FPGA内核架构(高达5.5M逻辑单元)以及其他先进的组件,从而提高了Stratix 10 FPGA和SoC的可扩展性和灵活性。单片内核架构避免了使用多个FPGA管芯来提高密度的竞争同构器件的连接问题。Altera的异构SiP集成技术是通过使用Intel的专用嵌入式多管芯互联桥接(EMIB,Embedded Multi-die Interconnect Bridge)技术实现的,与基于中介层的方法相比,进一步提高了性能,降低了复杂度和成本,增强了信号完整性。

“我们之所以选择使用Intel的这项封装技术,出于三方面的考虑。第一,数据的吞吐量,急速提升,从十几Gb/s到五十几Gb/s。通常在单一芯片当中很难实现如此大量的数据传输。第二,客户希望能够尽快地受益于HyperFlex架构,同时要求这些芯片支持那些尚未被确定为标准的协议,所以这对于我们来说面临着一个两难的选择。第三就是调制格式的问题,随着要求越来越高,芯片之间的对话方式也变得更加具体化,我们必须要使得一个逻辑与另外一个器件进行对话的时候,它使用到的引脚得到很大程度的优化,从而使得这两个芯片能够以一种很具体的方式来实现沟通。”Patrick Dorsey解释道。

初次发布的Stratix 10器件将使用EMIB来集成高速串行收发器和协议块以及单片内核逻辑。通过异构3D SiP方法实现高速协议和收发器,Altera将能够快速交付Stratix 10器件型号,满了不断发展的市场需求。例如,使用异构3D SiP集成技术为Stratix 10器件提供了途径来实现更高的收发器速率(56 Gbps)、新出现的调制格式(PAM-4)、通信标准(PCIe Gen4、多端口以太网),以及模拟和宽带存储器等其他功能。

创新的安全设计管理器:提供业界最全面的安全功能

第十代的FPGA产品,其中会涉及到500多万个逻辑单元,相比当前一代产品在逻辑单元数量上提升了5倍之多。Patrick Dorsey分析:“通过创新的安全设计管理器,我们可以把这些FPGA的逻辑单元分离开来,在每一个单元上面都可以有单独的一个芯片,使它的安全性能得到很大的提高。对于云提供商来说,他们可以把某一个客户的应用和另外客户的应用区分开,最大程度地保障客户应用的安全性。”

除了上述创新的性能提升之外,Altera还提供了全面的设计环境和Enpirion电源模组来支持Stratix 10的应用。