文献标识码: A

文章编号: 0258-7998(2015)04-0029-03

0 引言

PCM(Pulse Code Modulation)是一种有效成熟的数字化的编码系统,广泛应用于航空、航天、地面遥测站、移动遥测试验等国防领域中[1-3]。数据综合器是弹上遥测设备的数据综合设备,不同型号导弹根据测试参数数量的不同配置不同数量的数据综合器,分布在导弹的弹头、弹体及弹尾。数据综合器控制弹上各种采编器、中间变换器。各采编器采集到的参数经中间变换器变换后发送到内部数据总线上,数据综合器在时序的配合下,接收这些数据并按照预先约定的帧结构进行编帧,之后以综合数据流的形式输出给遥测发射机进行调制和功率变换。由于应用场合的特殊性,数据综合器通常不具有通用性。不同的数据综合器通常具有不同的码型、码率、帧格式、接口。研制一种码率、码型、帧格式、位宽等可以柔性调整的通用数据综合器测试仪,可以在保证测量效果的前提下,实现不同产品复用一台测试仪,从而提高可靠性,降低研发成本,加快遥测系统研制配套周期[4-5]。

1 系统总体结构

测试系统硬件采用总线背板与模块化插卡方法,如图1所示,主要由背板总线模块、主控模块、综合数据流测试模块、模拟源模块及电源模块组成。上位机使用LabWindows/CVI 编写,该软件是建立监控检测系统,自动化测试环境与数据采集系统的理想开发环境。

测控计算机配置各模块的相关参数,包括码型、码率、帧同步码、帧长,并对测试仪解码后上传的数据进行分析、处理及显示处理结果;主控模块是整个测试仪的核心控制模块,上位机下传的数据和命令以及其他模块上传数据都受主控模块的控制;背板总线是主控模块与各功能模块之间的通信桥梁,电源模块也通过背板总线向测试仪内部各模块供电;综合数据流测试模块接收不同的待测数据流并进行解码,然后上传到上位机进行后续处理,是实现通用测试功能的核心;综合数据流模拟源模块由上位机配置数据流参数,输出不同的数据流,用作系统自检,同时可作为其他外部设备的标准源。

2 主控模块

主控模块是联系测控计算机与测试仪的关键节点。与上位机之间的通信通过USB接口实现,与其他各模块之间则通过高速LVDS总线进行通信。主控模块电路方案如图2所示,通过USB接口电路接收上位机下发的命令和数据,由FPGA进行数据格式变换后,在120 MHz时钟控制下,通过LVDS模块DS92LV18进行串化后发送至背板总线,总线上的其他模块按地址接收数据并响应。综合数据流测试模块对接收到的数据流进行解码后,将数据通过背板总线发送到主控模块,主控模块把接收到的数据经DS92LV18解串、FIFO缓存,通过USB接口上传给上位机。

3 背板总线模块

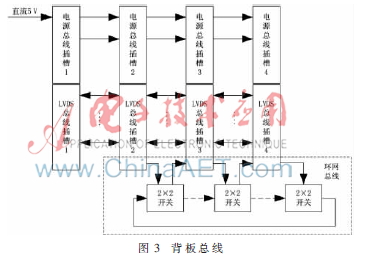

背板总线模块是测试仪内部各模块间的桥梁,包括电源总线和信号总线两部分。电源模块通过电源总线为测试仪内部供电;信号总线完成系统内部各模块之间的通信任务。其中信号总线选用低压差分信号技术LVDS总线,该总线具有低功耗、低误码率、低串扰和低辐射的优点,且可以高达数千Mbps的速度传送串行数据。

背板总线模块模块硬件原理如图3所示,由4对总线插槽和3个2×2模拟交叉开关组成。4个插槽分别对应电源模块、主控模块、综合数据流测试模块和数据流模拟源模块。插槽、槽上的功能模块以及插槽间的高速2×2模拟交叉开关共同形成自适应的LVDS环网总线,作为测试仪内部信号传输总线。

4 综合数据流测试模块

综合数据流测试模块是实现系统功能的核心单元,主要由阻抗匹配及电平转换接口、位同步器、码型变换、帧同步器及参数识别和逻辑控制模块组成。其原理图如图4所示。

本设计中,除输入端的阻抗匹配及电平转换接口电路和输出端的LVDS接口电路,其他功能均通过一片PFGA实现,电路简洁,方便升级更新。LVDS控制器实现对上位机命令参数的接收、解码数据的上传以及位同步和帧同步状态的上传。位同步模块、码元变换模块以及帧同步模块配合实现对不同数据流的解码,完成通用测试的核心功能。

要实现对不同码速率的数据流的解码,就要求系统可以快速准确地生成对应的恢复时钟,完成位同步。码同步模块采用DDS+鉴相器的方案实现同步时钟的提取[6]。原理框图如图5所示。

使用64位的累加器保证DDS分频精度和分辨率,频率控制字K由式(1)计算得到。

K=fo×264/fR(1)

其中fR为输入参考时钟频率,fo为待测数据流的码速率。当接收到参数K时,DDS可快速生成与待测数据流码速率相同的时钟。之后还需完成时钟与信号的对齐,这直接关系到系统的误码率及信噪比。当输入信号出现跳变时,读取DDS中累加器的sum值、即时相位,可得到时钟与信号的准确关系,根据超前量或滞后量,对sum进行加K或减K操作,加K即使下一个同步时钟提前一个参考时钟周期,减K即使下一个同步时钟滞后一个参考时钟周期。同时使用抖动容限值L,当超前或滞后超过L时,直接对同步时钟进行复位。此种时钟同步方案完成同步仅需1个时钟周期,不仅满足不同码速率的数据流的测试需求,而且进入同步状态快速稳定。

待测数据流码型不尽相同,码型变换模块根据码型参数对其进行运算转换为NRZ-L码。完成码型变换之后,帧同步器将码型变换后的数据信号流中提取字同步和帧同步信号,产生帧同步和字同步保护信号,从而完成数据分离并获得正确的数据格式。帧同步信号频率由位同步信号分频即可方便得出,然而每帧的开头和末尾不能由此得到,为实现帧同步,在数字信息流中插入一些特殊码组作为每帧的头尾标记,接收端根据这些特殊码组的位置实现帧同步。

本系统要求通用性,因而帧格式是可编程的,在工作时,上位机通过USB接口进行参数配置,包括帧同步码组、帧同步误差容限、帧同步保护系数和帧同步检码系数等,下位机将这些参数存入寄存器,串行数据经移位寄存器移位后锁存,锁存后的数据与本地同步码组送入相关检测器进行检测。相关检测器直接关系到帧同步器的速度和精度。一个N位长的数字相关器,U={u1,u2,…,uN}是同步码组,R={r1,r2,…,rN}是数字相关器任意时刻接收的数据流通过移位寄存器的内容,R与U进行异或运算,得到ri与ui不一致的个数W。W与相关检测门限ε比较,若W>ε,则认为没有检出同步码,容错判决输出;若W≤ε,则同步码被检出。

5 模拟源模块

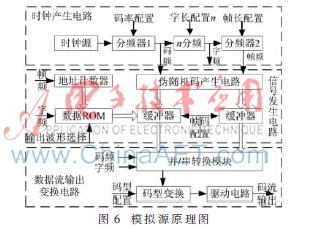

模拟源产生需要的数据流,实现综合数据流测试模块的自检和其他遥测设备的检测,由时钟产生、信号发生和码型变换3个核心部分组成。时钟产生根据上位机配置的码率和帧格式信息产生对应的码频、字频和帧频信号;信号发生部分在字频信号控制下从数据ROM中读出需要的特定波形数据,与同步码组按指定格式进行编帧;码型变换部分按照上位机下发的参数将NRZ-L码变换成NRZ-L/M/S、Bi-φL/M/S。原理图如图6所示。

6 结束语

使用LabWindows/CVI编写了对应的上位机软件,主界面如图7所示,通过该软件对下位机进行参数配置、解码数据的读取以及数据的后续处理。模拟源可生成1~10 Mb/s码速率的PCM数据流,帧格式按IRIG-106标准可编程[7],可输出正弦波、方波、三角波、锯齿波、随机数和固定值6种波形数据,编码格式NRZ-L/M/S、Bi-φL/M/S 6种可选,单端、差分可选。综合数据流可实现上述可编程PCM码流的解调。

参考文献

[1] 喻金科,徐精华,邹雄.基于FPGA的可编程PCM解调器的设计[J].微计算机信息,2010,12(2):136-138.

[2] 毕海,李永新,李柯.一种PCM遥测同步解调器的设计[J].电子测量与仪器学报,2000,14(1):66-70.

[3] 甄国涌,林华亮.串行PCM码流解码电路设计与应用[J].航空计算技术,2005,35(1):79-81.

[4] 张天平,许斌.基于FPGA的遥测解调系统设计[J].电子元器件应用,2007,9(9):43-46.

[5] 朱旖,杜建军.国外军用电子自动测试系统发展综述[J].电子测量技术,2008,31(8):1-3.

[6] 刘东华,王元钦,袁嗣杰,等.基于瞬时测频的PCM/FM信号解调方法研究[J].系统仿真学报,2005,17(10):2463-2466.

[7] 李国民,周富大,高维路,等.基于IRIG-106标准的可编程PCM编码数据采集系统[J].遥测遥控,2003,24(4):27-30.