文献标识码: A

文章编号: 0258-7998(2015)04-0087-04

0 引言

应用于航天遥测中的视频摄像技术可以真实地还原航天器的飞行状态、动作和现场环境等多项关键指标。航天器的飞行试验要求图像具有较高的空间分辨率和时间分辨率,才不致丢失重要细节,通常使用高速摄像机作为采集系统前端。在该领域,现场的场景必须完整、真实地还原出来,而航天器有时可能不在地面监测范围之内,一些在轨试验数据只能先存入记录器中,进入监测范围内再将数据回传。记录装置的容量、带宽以及其可靠性和稳定性等因素都将影响数据能否准确保存,并关系到整个试验的成败[1]。

数据存储技术的进步主要体现在存储介质的发展和各种通信总线的应用上。存储介质从磁带到硬盘再到半导体器件,逐渐向微小型化、低功耗、高集成度和密集化发展,而半导体存储器件已广泛应用于航天遥测领域。随着1553B、光纤接口、以太网接口等高速总线的应用,存储带宽也得以提高。LVDS接口凭借其低噪声、低功耗和极高的传输效率等特点在测试计量、图像处理方面发挥重要作用。本文旨在设计一种高可靠性的数据记录器以实现对高速数字视频信号的采集、存储和回传。

1 设计思路

结合当前数据记录器的研究现状和发展趋势,采用FPGA作为数据记录装置的中控逻辑单元,用Flash作为核心存储芯片,使用LVDS作为数据传输接口,特点是功耗低、可控性高,并且数据不易丢失。设计时,采用自上而下的设计思想,分成多个模块进行编码和调试。

已知数字视频信号参数:画面分辨率为VGA(640×480),帧率100 f/s,采样位数为8 bit,采样频率为40 MHz。经计算得出接口处的数据流为30.72 Mb/s。应用于航天遥测的精密仪器对设备出现误码、数据丢失等情况有严格的限制,其可靠性和稳定性应得到保证。确保设备研制成功的关键技术有三:一是数字视频信号的完整采集,二是选择合理的Flash工作方式并严格控制其时序约束,三是准确高效地回传混有帧标记的图像。

2 关键技术

2.1 图像采集

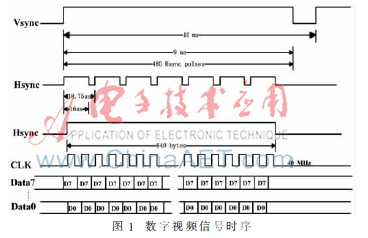

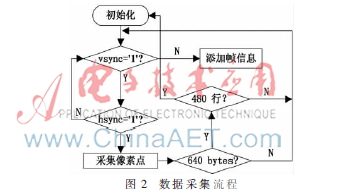

摄像机输出的数字视频信号的时序如图1所示。垂直同步信号vsync是实现图像帧同步的标志,当vsync为1时,摄像头有数据输出,vsync上升沿是获取一帧数据的初始时刻;当vsync为0时,无数据输出,可以利用这段时间在一帧图像采集完成后加入其他信息,如时标、帧计数和帧标记等。水平同步信号hsync的上升沿为采集每一行的初始时刻,当hsync为1时,完成此行640个像素点的采集。重复操作480次,即可获取一帧完整的图像。数据采集流程如图2所示。

在高速数据处理过程中,不同模块在各自的同步时钟下工作,为解决跨时钟域问题,要在数据交换接口处添加异步FIFO,以匹配不同传输速率的数据流。由图1可知,在一个水平同步周期(18.75 s)内,采集并写入FIFO的数据量为640字节,若以33 MHz的速率读FIFO,则在这一时间内,流出FIFO的数据量为618.75字节。数据差值将在Vsync下降沿时达到最大,为10 200字节,若采用半满即读的方式,则FIFO容量应大于20 400字节,否则就可能溢出。摄像机在时钟上升沿发数,记录器用时钟下降沿取数。存到记录器中的数据是图像和信息的组合,为了区分两种类型的数据,采用9位的FIFO缓存数据,低8位用以写入数据流,最高位(MSB)用来标识数据类型。部分代码如下:

writeclk<=((not clk) and hsync) and vsync);

---写FIFO时钟

fifo_in<=′0′ & information when vsync=′0′ else

′1′ & image_data;

---加 ′0′表示信息,加 ′1′表示图像

2.2 数据存储

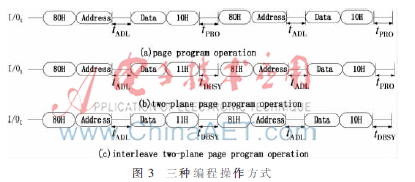

Nand Flash有多种编程方式,如页编程(Page Program)、双平面页编程(Two-plane Page Program)和交叉双平面页编程(Interleave Two-plane Page Program),如图3所示。这三种工作方式最终导致Flash写入数据的速度不同[2]。

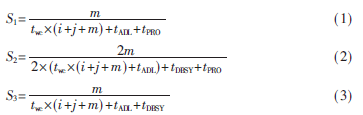

由表1可以看出,影响Flash编程时间的主要因素为tPRO。前两种方式都花费了大量的时间用在tPRO上,tPRO会随着工作电压和温度的不同而变化。写完一整页需要i个命令字周期、j个寻址周期和m个数据周期。

在三种工作方式下,若不考虑其他影响因素,Flash的持续写入速率计算如下:

事实上,在出厂时芯片就存在无效块,而且在使用过程中还会产生新的无效块。无效块的存在一定程度上影响了Flash的写入速度,按照“判一块写一块”的方法显然是行不通的。为此,本文采用一种“无效块动态管理算法”,即:在执行写操作前对无效块进行检测,在RAM中建立无效块地址列表;写入数据时,将当前块地址与列表中的无效块地址按顺序对比判断;若一致,则认为当前块无效,继续判断下一块;否则,认为当前块有效,可以进行写操作[3]。读取RAM无效块列表的时间与无效块检测的时间相比微乎其微,在理论上和实际应用中都得到了验证。

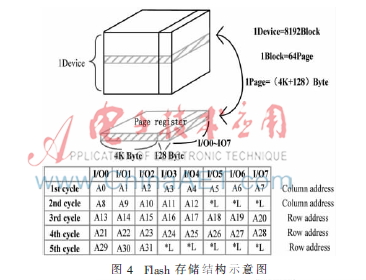

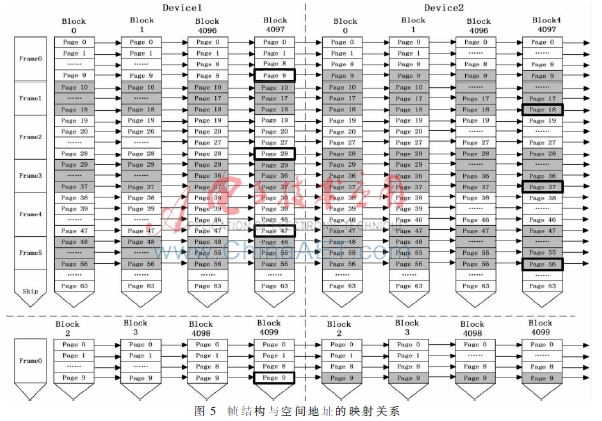

Flash的编程编码算法本身并不复杂,但如果不对其做任何处理,一旦数据产生误码或丢失,在图像回传时,可能导致后续图像紊乱影响全局。因此,有必要对Flash存储空间进行特殊配置,以空间地址来记录帧结构。Flash每个Device存储空间结构如图4所示,用A13~A31指定页地址, 总共524 288页,2个Device共1 048 576页[4]。一帧图像数据为307 200字节,占用75页,若按试验要求,飞行器每次工作记录的5 000帧图像数据仅占用了全空间的36%,有足够的空间来配置地址,甚至完成地址的选择和跳跃。空间地址配置方式如图5所示:白、灰两色背景分别表示一帧数据,图像数据累计写满75页,紧跟在第76页写入信息,这样就完整地记录了一帧数据,其中,代表信息的一页用黑色加粗边框标出。采用交叉双平面页编程的工作模式,写入顺序如黑色箭头方向所示。Flash每一行有8个块,每块有64页,共512页,每行可以完整写入6帧数据,然后跳过56页进入下一行继续按照以上方法写数[5]。以此类推,每连续6个数据帧就有了统一的存储结构,便于对图像的恢复。这样做的另一个优点是可以实现数据的检错和纠错:数据从FIFO中流出被写入Flash时,假若最高位为0,而计数器并非76,说明传输时有数据丢失,则在写完信息数据后,直接跳到指定位置写下一帧,将错误限制在一帧内,而不影响后序数据帧[6]。

2.3 图像回传

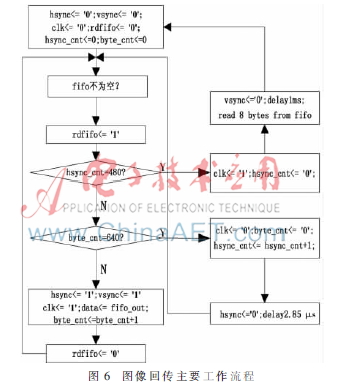

图像回传的本质就是按照图1的时序将Flash存储的图像数据通过LVDS接口发出。由于每帧数据的附带信息并非回传所需,因此可以将第76页直接跳过;但这样做的缺点是回传读数和普通读数要被分为两个不同的进程,增加了程序占用的资源。因此,可以合并这两个进程,由后续模块提取图像数据[7]。这个过程将包括两部分:一是按照图5所示黑色箭头方向读取数据并写入FIFO低8位,同时根据存储空间地址判断数据是图像还是信息,用FIFO的最高位加以区分。二是FIFO非空即读,若为图像则合理产生vsync、hsync和clk信号,并在clk上升沿时推送数据;否则将vsync、hsync和clk信号全部置为低电平,且不把数据推送至LVDS接口处。过程一相对比较简单,这里不再叙述;过程二的工作流程如图6所示。

3 系统验证

为了验证本文设计的记录器的整体性能和可靠性,专门设计了一套检测设备,包括硬件平台和测试软件。该设备的主要功能有:(1)模拟前端摄像机,输出垂直同步信号、水平同步信号、时钟信号和8位位宽的数据流;(2)接收记录器回传的图像;(3)测试软件可以直接读取记录器中的完整数据(称为“长线读数”),也可以读取回传至测试设备中的图像数据(称为“备用读数”);(4)判定帧结构是否完整,检测数据是否正确;(5)显示图像。

由于一帧图像数据有300 KB,若采用递增模式的信号源,模拟摄像机输出的数据格式为:1 200个“00h~FFh”+8字节的附加信息(“14 92”+帧计数+时标+状态信息)。

计算机软件执行“长线读数”或“备用读数”命令后,将在线读取完整数据或图像数据,存入一个后缀名为.dat的文件,经多次考查,记录装置存储的数据与检测设备发送的数字量一致,符合设计要求。

4 结束语

本文主要介绍一种高速数字视频信号记录装置,从程序编码方面入手,选择了稳健、高效能的算法,重点介绍了图像采集、存储和回传三项关键技术,并设计了一套专用的检测平台。经单机测试,设备稳定性良好、功能齐备、满足任务要求。由于采用的Flash芯片所限,本文所提出的编码算法仅适用于码率在40 Mb/s以下的数据存储。

参考文献

[1] 洪应平.高速图像数据固态存储器的研制[D].太原:中北大学,2011.

[2] 谢民.NAND型Flash在大容量存储回放系统中的应用[J].集成电路应用,2006,3(4):94~98.

[3] SAMSUNG Electronics.K9WBGU1M Flash Memory:10-13.

[4] 孟令军,严帅,龚敬,等.基于FPGA的高速图像采集存储系统设计[J].自动化与仪表,2011,9(26):40-42.

[5] 常璐.基于NAND Flash阵列的数据存储技术研究[D].太原:中北大学,2011.

[6] 齐亚军,赵凤军.一种专用高速数据记录器的设计与实现[J].微计算机信息,2007,23(1):107-109.

[7] 王小艳,张会新,孙永生.Camera Link协议和FPGA的数字图像信号源设计[J].国外电子元器件,2008(7):59-61.