摘 要: 介绍一种基于gm/ID参数特性的模拟电路优化设计方法,并以CMOS两级运算放大器的设计为例具体阐述该方法的基本设计步骤和与传统设计方法相比的优势。该方法以晶体管的跨导和漏电流的比值gm/ID与反型系数IC的特性曲线作为设计参量来对电路进行设计。基于gm/ID的设计方法对晶体管工作在所有的工作区域均有效。实验仿真结果很好地验证了gm/ID设计方法的有效性。

关键词: 运算放大器;gm/ID 设计方法;反型系数

0 引言

便携式电子设备已深入到人们生活的各个方面,由于受电池的限制,低电压低功耗电路的应用不断增加。随着电压和功耗的不断降低,模拟集成电路的设计难度也随之增加。为了获得最佳工作点,就需要复杂的计算和长时间的设计综合。而利用gm/ID方法进行设计不仅可以大大提高设计效率,而且允许在所有的晶体管工作区域内用统一的设计方法,从而达到简化模拟电路的设计过程。gm/ID设计方法是基于EKV模型而提出的。该方法与传统的设计方法的不同是选择了漏极电流、反型系数、沟道长度作为设计的三个自由度。该方法选择的三个自由度与电路性能直接相关,从而可提供较好的设计直觉。因此基于gm/ID的设计方法避免了手工计算因忽略大量调制因素而带来的越来越大的设计误差,同时也大大缩短了调适设计的周期。

1 传统设计方法

模拟集成电路设计可以分成两个明显与设计相关的步骤,即构造电路的基本结构和选择直流电流和各晶体管的尺寸。构造电路的基本结构在本文中不作详细讨论,而对于选择直流电流和各晶体管的尺寸,在典型情况下,模拟电路设计者任意地选择电路支路的偏置电流开始设计,根据所选择的偏置电流和相关的工艺参数确定晶体管的尺寸。几乎无法避免的是,设计者要不断地重复调整电流值和器件的尺寸以达到设计指标。

传统的设计方法是假设晶体管工作于强反型区而将晶体管的栅极过载电压VOV作为关键的设计变量[1],其中VOV=VG - VTH。另外,当晶体管工作于弱反型区时,根据简单的指数关系的I-V特征曲线进行设计[2-3]。

然而随着晶体管沟道长度的不断减小,短沟效应越来越显著。适用于长沟道器件的平方律模型不再适应。另外当器件工作于弱反型区和强反型区中间的中等反型区时,平方律模型和弱反型区的指数模型均失效。而该区域在现代设计中越来越重要,这是因为它对于高效率和低电压设计,能够在高跨导效率、低漏-源饱和电压、最小速度饱和以及中等带宽之间提供一种优化折中。

2 EKV模型理论

gm/ID设计方法是基于EKV模型而提出的。EKV模型[4-5]是一种用于设计低电压、低电流电路的MOS晶体管模型。EKV模型以衬底为参考电位,体现了晶体管固有的对称性。在这个模型中,所有的大信号和小信号变量在不同的工作区域都是连续的。对于这个模型所有方程的推出都采用同样的方法。其结果表明反型层电荷Qinv是由Vp-Vch这一电压差决定的,其中Vch是沟道电压。而Vp为Vch的特定值,即对于给定的栅极电压,当反型层电荷为零时的Vch值。Vp只依赖于栅极电压,因此可以认为Vp是栅极电压对于沟道所产生的等效效果。MOS晶体管的不同工作区域的方程用VP-VS和VP-VD的函数来表达。若采用的晶体管模型假设沟道内是均匀掺杂的,则漏极电流ID可以被表达为正向分量电流IF和反向分量IR的差值。而这两个分量通过一个特定的电流IS分别与VP-VS和VP-VD的函数成正比。这个函数在弱反型层为指数函数,在强反型层为二次函数。而在中等反型层的电流是通过一个适当的插值函数建模得到的,这个插值函数使得电流从弱反型层到强反型层都有一个连续的表达式。

3 gm/ID设计方法

gm/ID的比值反映了电流(即功耗)转化成跨导的效率,比如当电流恒定时,gm/ID越大意着著跨导值越大。选择gm/ID作为设计参数是因为以下三个依存关系:

(1) 与模拟电路的性能直接相关;

(2) 能反映晶体管的工作区域;

(3) 提供了一个可确定晶体管尺寸的工具。

在gm/ID设计方法中引入了反型系数IC[6]来表征晶体管工作在哪个区域,IC定义如下所示: ,其中n和u都随着IC的增大而减小,因此,可以定义一个固定的IC0如下所示:

,其中n和u都随着IC的增大而减小,因此,可以定义一个固定的IC0如下所示:

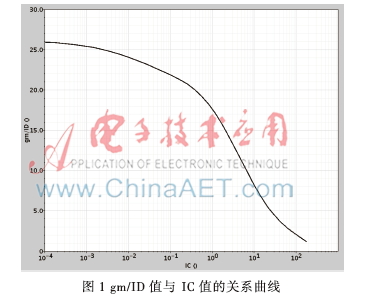

其中 。跨导效率gm/ID与反型系数IC的关系曲线与器件的尺寸无关。所以对于给定的设计工艺,只需要仿真出一条gm/ID-IC曲线,就可以适合所有的设计,给设计带来了便利。如图1所示,借助gm/ID和IC的关系曲线可以由gm/ID确定晶体管的工作区域[7-8]。

。跨导效率gm/ID与反型系数IC的关系曲线与器件的尺寸无关。所以对于给定的设计工艺,只需要仿真出一条gm/ID-IC曲线,就可以适合所有的设计,给设计带来了便利。如图1所示,借助gm/ID和IC的关系曲线可以由gm/ID确定晶体管的工作区域[7-8]。

IC值与晶体管的工作区域的关系[9]如下:

⑴IC<0.1,晶体管工作在弱反型区;

⑵0.1<IC<10,晶体管工作在中等反型区;

⑶IC>10,晶体管工作在强反型区。

由以上关系再对照图1可知,当晶体管处于强反型区时,gm/ID值最小,当晶体管处于弱反型区时,gm/ID值最大。中等反型区处于两者之间,是一个过渡区域。

基于gm/ID的设计方法实际上就是以晶体管的偏置工作区域作为设计基础。众所周知,晶体管偏置于弱反型区具有更好的直流增益特性,而偏置于强反型区具有更好的带宽特性。作为两者的过渡区域,中等反型区兼容了两者的优点,是多种性能的折衷。

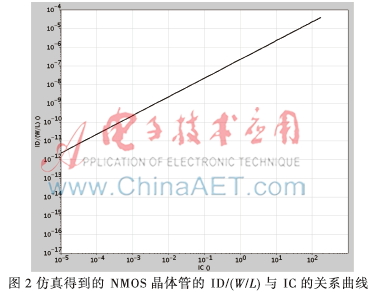

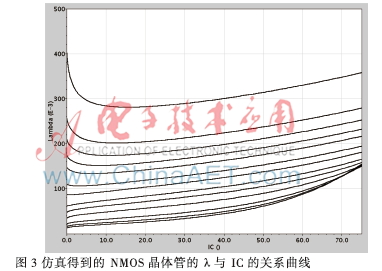

基于gm/ID的设计方法是基于图表的思想。这里主要考虑两组函数曲线。一组是图2所示的标准化电流ID(W/L)的IC为变量的函数曲线。首先选择IC的值,也就是确定器件的工作区域,晶体管的宽长比W/L就可以从这组曲线中得到。另外一组重要的关系曲线是如图3所示的IC和沟道长度调制因子λ的函数关系,一旦λ和IC的值确定,晶体管的长度就可以确定。

考虑上述gm/ID设计方法的特性可知设计过程包含两个基本的设计维度。首先,从ID/(W/L)-IC和gm/ID-IC曲线确定每个晶体管的宽长比W/L;然后考虑IC和λ的关系,从而得到L的值。

由上可以得到gm/ID方法的设计步骤如下:

⑴选择合适的电流:通过电路性能的要求估算出各个支路的电流。

⑵选择合适反型系数IC:比如对于电流镜中的MOS管,为了更好地匹配和减少噪声,一般选择其工作在强反型区;对于功耗要求高的电路,选择MOS管工作在中等反型区。反型系数IC直接决定gm/ID,而直流增益正比于gm/ID,所以仅从直流增益考虑gm/ID越大越好。

⑶选择合适的沟道长度:沟道的长度需要在器件的面积、电路的稳定性和直流增益之间做一个权衡。根据不同沟道长度的λ-IC曲线来选取。

4 基于gm/ID的设计方法在OTA设计中的应用

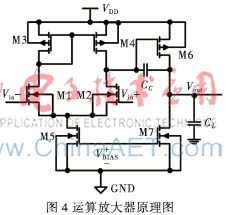

这一部分将前面所介绍的gm/ID设计方法应用于一个两级运算跨导放大器的设计中。该运算放大器的电路原理图如图4所示。

4.1 运算放大器的设计

设计要求达到的性能指标如下表1所示。

⑴电流的确定

首先确定补偿电容CC的值。从相位裕度关系式,由60°的相位裕度可得 可选CC为3 pF。

可选CC为3 pF。

由摆率要求可得I5:![`4M2U1TQNCG11QV_O1UX]0U.png](http://files.chinaaet.com/images/2015/09/11/6357759157548800004776785.png)

![]4LH0RYS(7O[1E}{XC7~W6Q.png ]4LH0RYS(7O[1E}{XC7~W6Q.png](http://files.chinaaet.com/images/2015/09/11/6357759159223300003672793.png)

⑵S3的求解

M3和M4构成电流镜,为了确保更好地匹配和减少噪声,并且考虑ICMR最大值的要求,选定IC3=15。

根据NMOS管的gm/ID和ID/(W/L)与IC的关系曲线,得到:

(gm/ID)3=6.33 μs/μA

(ID/(W/L))3=1.509 μA

根据晶体管的λ与IC的关系曲线,得到: λ3=0.29 V-1

⑶S1的求解

I1=I3=15 μA,gm1=2πCC×GB=94.25 μs

得:(gm/ID)1=6.3 μs/μA

根据NMOS管的gm/ID和ID/(W/L)与IC的关系曲线,得到:

IC1=17,(ID/(W/L))1=3.757 μA

同上可得: λ1=0.141 V-1

⑷S5的求解

I5=30 μA,考虑M5的匹配和噪声,M5应该工作在强反型区,选定IC5=20,根据NMOS管的gm/ID和ID/(W/L)与IC的关系曲线和λ与IC的关系曲线,得到:

(gm/ID)5=5.68 μs/μA

(ID/(W/L))5=4.42 μA

⑸S6的求解

RHP零点Z1要高于10 GB,所以:

gm6≥10 gm1=942.5 μs。

选定gm6=942.5 μs,为了达到第一级电流镜负载的正确镜像,就要求 VSG4=VSG6,从而得到:

Von4=Von6=189.1 mV,IC6=9

同上可得: λ6=0.266 V-1

根据NMOS管的gm/ID和ID/(W/L)与IC的关系曲线,得到:

(gm/ID)6=10.1 μs/μA,(ID/(W/L))6=0.9 μA

I6=(gm)6((gm/ID)6)=93 μA

⑹S7的求解

I7=I6=93 μA,考虑到Vout最小值的摆幅要求,选定IC7=20。从而得到:

(gm/ID)7=5.69 μs/μA,(ID/(W/L))7=4.42 μA

根据晶体管的λ与IC的关系曲线,得到:λ7=0.144 V-1。

4.2 运算放大器验证

⑴幅频特性和相频特性

经过仿真验证得AV=76.366 dB,相位裕度ΦM=49°,增益带宽GB=5.1 MHz

⑵ICMR

经过仿真验证得ICMR最小值为0.101 9 V,最大值为4.893 V。表2为gm/ID方法与传统方法设计仿真结果的对比。表中明显显示出了gm/ID方法的优势。

5 总结

本文提出了基于晶体管gm/ID特性的模拟电路设计方法,这种设计方法利用gm/ID和标准化电流ID/(W/L)与IC的关系,调制因子λ和IC的关系来对电路进行设计。gm/ID-ID/(W/L)-IC之间的关系与器件的尺寸无关,只要仿真一条gm/ID-ID/(W/L)-IC的关系曲线,就可以应用于所有的设计,极大地方便了设计者。与此同时也适用于晶体管工作于所有的工作区域,对于低电压、低功耗的设计具有极大的优势。另外,它的一个很大的优点是从手工计算到SPICE仿真,不会像传统方法那样忽略过多的不确定的调制因素而产生较大的设计误差。

使用该设计方法设计的运算放大器得到了很好的仿真结果,验证了所提出的设计方法的可行性,向模拟电路的快速准确和高性能要求的设计方向迈出了很大一步。

参考文献

[1] ALLEN P E, HOLBERG D R. CMOS模拟集成电路设计,(第3版)[M]. 冯军,李智群, 译. 北京:电子工业出版社,2005.

[2] BAKER R J. CMOS电路设计、布局、仿真(第2版)[M]. 刘艳艳,张为,译. 北京:人民邮电出版社,2008.

[3] 拉扎维. 模拟CMOS集成电路设计[M]. 陈贵灿,程军,张瑞智, 等, 译. 西安:西安交通大学出版社,2003:13-18.

[4] Enz c c, Krummenacher F, Vittoz E A. An analytical MOS transistor model valid in All regions of operation and dedicated to low-voltage and low-current applications[J]. analog Integrated circuits and Signal Processing, 1995,8(1),83-114.

[5] 柳美莲. 基于EKV衬底驱动MOSFETs的超低功耗运算放大器设计[D]. 北京:中国科学院研究生院,2006.

[6] 吴贵能,周玮,李儒章. 一种基于跨导电流比-反型系数-过驱动电压的设计方法[J]. 微电子学, 38(5):656-659.

[7] 陈德斌,常昌远. 基于gm/ID参数的运算放大器设计[J]. 电脑知识与技术, 2007(1):1020-1022.

[8] 李新,王业飞,杨国坤. 一种基于gm/ID方法设计的可变增益放大器[J]. 电子设计工程, 20(24):146-149.

[9] SILVEIRA F,FLANDRE D,JESPERS PG A. A gm/ID based methodology for the design of CMOS analog circuits and its application to the synthesis of a silicon-on-insulator micropower OTA[J]. IEEE J Sol Sta Circ. 1996,31(9):1314-1319.