文献标识码: A

文章编号: 0258-7998(2014)11-0012-04

0 引言

在传统的雷达仿真训练系统中,通常以工控机作为硬件平台,在Windows操作系统下采用高级语言(VC++等)编程的方法实现目标信号的产生及PPI显示。该方法具有仿真逼真程度高及硬件通用性好等优点,但受平台影响,存在体积大、重量重、便携性差及系统组成复杂等不足。

本文介绍一种基于FPGA的雷达PPI显示设计及实现方法,能克服传统方法的不足。

1 雷达PPI显示原理

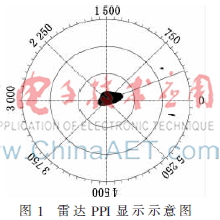

平面位置显示器(PPI),属于径向圆扫描显示,采用长余辉电磁偏转阴极射线管或静电偏转示波管实现。PPI显示器的优点为目标数据直观,易于理解,通常用于搜索警戒和作战指挥。其显示效果如图1所示,图中扫描线的指向为雷达天线的方位,扫描中心点与回波信号间的长度代表目标的距离,回波的形状能够体现目标的回波特征[1]。

2 PPI显示研究与设计

2.1 PPI显示仿真原理

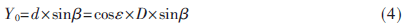

根据雷达的工作原理,在其探测到目标后,可从回波中提取目标的位置信息。在直角坐标系中,目标主要包括斜距(D)、水平距离(d)、高度(h)、方位角(β)及高低角(ε)等信息,如图2所示[2-3]。

由于雷达波以光速传播,目标斜距D与传播时间tr的关系如下:

目标水平距离d为:

设水平距离d在正北方位的投影为X0,则有:

设水平距离d在正西方位的投影为Y0,则有:

在LCD显示器中进行PPI仿真显示时,首先,根据式(1)求出斜距,再根据式(2)求出目标在以雷达为原点的投影。其次,如图2所示,假设以正北方位为X轴,以正西方位为Y轴,根据式(3)、式(4)可将目标三维坐标信息转换为以雷达为原点的二维坐标信息。最后,根据LCD显示器像素等比例缩放,设N个像素点表示水平距离d,比例因子为K,有:

根据上式,可将以雷达位置为坐标原点的目标平面位置参数(X,Y)转换为以LCD显示器平面左上角为原点的平面坐标位置参数(x,y),则:

仿真时,为了实现如图1所示的显示效果,通常将LCD显示器像素点(x0,y0)作为原点。由于LCD显示器原点为左上角,通过坐标平移来实现该效果,有:

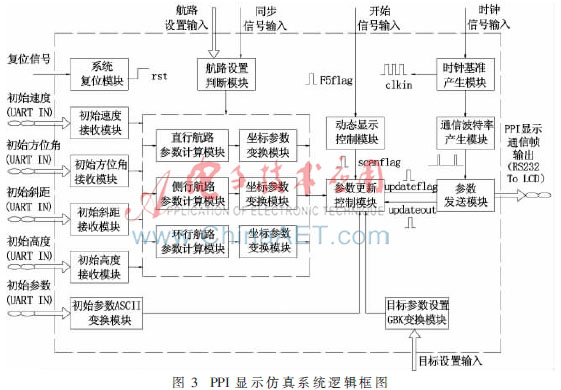

2.2 PPI显示仿真系统设计

根据某型雷达仿真训练系统功能需求,并结合FPGA处理器硬件资源,采用自顶向下的设计方法开展系统顶层设计。PPI显示仿真系统顶层设计为:系统复位模块、目标初始参数ASCII码变换模块及直行航路参数计算模块等19个功能模块。如图3所示,系统通过串行通信接收初始参数,计算目标参数,并进行坐标变换;动态显示控制模块产生参数更新触发脉冲;参数更新控制模块将目标参数信息组合为通信报文,并产生参数发送触发脉冲;参数发送模块通过RS232总线发送报文数据,发送完毕后产生脉冲信号,参数更新控制模块等待下一个参数更新触发脉冲。由此,系统完成了PPI显示及目标参数信息更新功能[4-5]。

2.3 PPI显示的IP核设计

根据PPI显示仿真原理,结合系统逻辑框图开展IP核设计。IP核主要完成目标坐标参数转换,将信息转换为LCD显示器字库码,RS232通信及目标参数周期更新等功能。

2.3.1 目标坐标参数转换

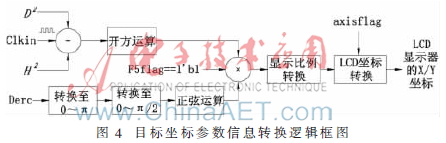

根据PPI显示仿真原理,先计算目标的水平距离,再进行比例缩放换算为LCD坐标参数。根据LCD分辨率,将(300,300)设置为原点,根据式(7)、式(8)实现该功能。根据上述关系,目标飞行航路PPI显示的逻辑图设计如图4所示。

Derc为目标的方位角,D为斜距,H为高度,axisflag为目标位置寄存器。当初始水平距离大于飞行距离则axisflag为“1”,否则为“0”。目标坐标参数信息转换主要包括开方、乘法及除法等算术运算[6],关键为方位角的转换及坐标平移的实现。采用数据流级建模实现方位角的转换,求出方位角的余角。方位角余角的正弦与水平距离的乘积则为目标的x坐标值。建模语句为:

assign DercMulti=(Derc>13'd3000)?(13'd6000-Derc):Derc;

assign TempDerc=(DercMulti>13'd1500)?(13'd3000-

DercMulti):DercMulti;

assign dercwire=13'd1500-TempDerc;

方位角正弦与水平距离的乘积则为目标的y坐标值。建模语句为:

assign Dercmulti=(Derc>13'd3000)?(13'd6000-Derc):Derc;

assign dercwire=(Dercmulti>13'd1500)?(13'd3000-

Dercmulti):Dercmulti;

对目标坐标(x,y)进行比例缩放后,得到其在LCD上的(X,Y)坐标值。采用数据流级建模完成X坐标的平移。当axisflag为1,且方位角大于1 500密位小于4 500密位时,或者当axisflag为0,且方位角小于1 500密位或大于4 500密位时, X取值为(11'd300-xasis),否则为(11'd300+xasis)。建模语句为:

assign XaxisCode=(((axisflag==1'b1)&((Derc>13'd1500)& (Derc<13'd4500)))|((axisflag==1'b0)&((Derc<13'd1500)|(Derc>13'd4500))))?(11'd300-xasis):(11'd300+xasis);

在对Y坐标进行平移时,采用数据流级建模完成坐标平移。当axisflag为1,且目标方位小于3 000密位时,或者当axisflag为0,且目标方位角大于3 000密位时, Y取值为(11'd300-xasis),否则为(11'd300+xasis)。建模语句为:

assign YaxisCode=(((axisflag==1'b1)&(Derc<13'd3000))|

((axisflag==1'b0)&(Derc>13'd3000)))(11'd300-yasis):(11'd300+yasis);

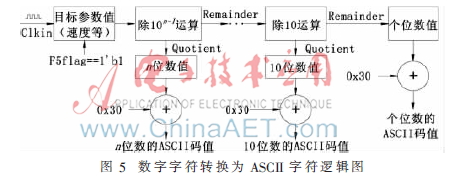

2.3.2 目标信息转换为LCD显示器字库码

航路目标参数主要包括速度、方位角、高低角、斜距、高度及水平距离等。在LCD显示器上显示时,需将数值转换为ASCII码值。其逻辑图如图5所示,采用除法运算求出各个位的数值。由于数字‘0’的ASCII值为0x30(48),数字加48得到其ASCII码值。

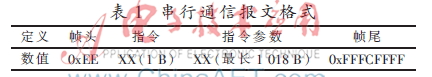

2.3.3 RS232通信及目标参数周期更新

航路目标PPI显示,由FPGA处理器通过RS232总线向LCD显示器发送报文实现。通信报文格式如表1所示,帧头长度为1 B,指令长度为1 B,指令参数最多可达1 018 B,帧尾长度为4 B。

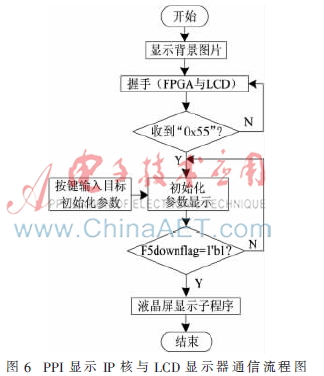

根据仿真系统功能需求,LCD显示器中显示的内容主要包括扫描线、刻度、目标航迹及目标参数信息等,并周期性更新。FPGA控制单元与LCD显示器进行串行通信的流程图如图6所示。

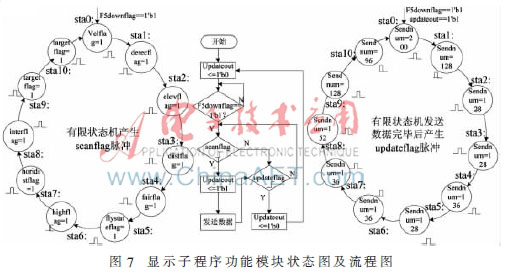

图6所示的液晶屏显示子程序中包含动态显示控制、参数更新控制、参数发送3个核心功能模块。其状态图及流程图如图7所示。动态显示控制模块采用有限状态机方式实现,当F5downflag为高时,动态显示控制模块、参数更新控制模块及参数发送模块工作。其中,动态显示控制模块开始计时,并周期性产生scanflag脉冲;参数更新控制模块捕捉到scanflag脉冲后,将updateout置为高电平,并开始判断updateflag的状态;参数发送模块捕捉到updateout上升沿后,通过有限状态机方式选择目标参数报文,实现参数周期更新,发送完毕后将updateflag置为高电平;参数更新控制模块捕捉到updateflag上升沿后将updateout置为低电平,等待下一个scanflag信号。由此,完成了PPI显示及更新。当动态显示控制模块产生地scanflag脉冲周期小于参数发送模块完成发送产生地updateflag脉冲的周期时,可实现PPI参数的周期性实时更新。

3 仿真试验与性能测试

3.1 仿真试验

使用Verilog HDL完成各功能模块的IP核设计,部分功能模块的IP核仿真如图8~图10所示。

图8为将以雷达为原点的目标的x坐标值缩放并平移至为以LCD显示器(300,300)像素点为原点的X坐标值仿真试验结果,与计算结果一致。

图9为根据目标的实时斜距及高度计算目标的高低角,并将高低角转换为ASCII值仿真。仿真结果与理论计算结果一致。

由仿真结果可以看出,PPI显示IP核将目标状态参数周期性的组合为报文,并通过串口发送,从而实现了目标参数PPI显示及更新。

3.2 性能测试

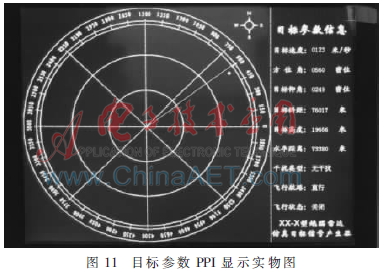

将IP核下载至FPGA,控制LCD显示器进行PPI显示[7],显示效果如图11所示,显示扫描线、目标的飞行轨迹及参数等信息,效果逼真。

4 结论

本文提出了一种基于FPGA的雷达PPI显示原理及实现方法,并应用于仿真训练装备。该方法继承了传统基于Windows系统PPI显示逼真度高等优点,并克服了其不足,成为某型雷达重要的仿真训练器材,受到了雷达部队官兵的好评。

参考文献

[1] 倪国旗.雷达模拟仿真训练原理及应用[M].北京:解放军出版社,2008.

[2] 丁鹭飞,耿富录,陈建春.雷达原理(第五版)[M].北京:电子工业出版社,2014.

[3] 夏宇闻.Verilog数字系统设计教程(第3版)[M].北京:北京航空航天大学出版社,2013.

[4] 王金明.数字系统设计与Verilog HDL(第4版)[M].北京:电子工业出版社,2011.

[5] 李如年,倪国旗.某型雷达系统仿真[J].火力与指挥控制,2008,33(3):111-114.

[6] 陈国军,万明康,王大鸣,等.乘除法和开方运算的FPGA串行实现[J].微计算机信息(嵌入式与SOC),2008,24(2-2):167-168,192.

[7] Microsemi Corporation.ProASIC3 Flash family FPGAs datasheet[Z].USA:Microsemi Corporation,2014.