文献标识码: A

文章编号: 0258-7998(2014)11-0032-04

0 引言

车辆牌照图像识别是计算机智能化的关键技术之一,涉及到模式识别、图像处理、人工智能、信息论、计算机等多个学科,有着极其广泛的实际应用价值[1]。

车牌识别系统主要由数据采集系统和软件识别系统两个主要部分组成,由于车牌清晰程度、摄像机性能、气候条件等因素的影响,牌照上面的字符可能出现不清楚、扭曲、缺损或污迹干扰,这都给识别造成一定难度[2]。因此,在复杂背景中快速、准确地进行车牌定位成为车牌识别系统的难点。

本文设计了一种智能车牌识别系统,系统采用FPGA平台,相对于单片机、CPLD为核心的平台提高了系统的集成度,大大节约了系统面积,降低了成本,提高了系统识别速度和效率,具有便携性好、易于维护等优点。

1 系统总体架构

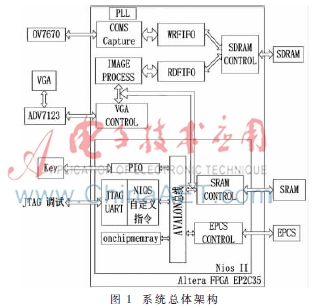

系统采用CMOS摄像头为前端图像采集器件,用以采集车牌图像信息,以Altera FPGA作为系统核心完成CMOS摄像头初始化,图像采集和处理、图像定位以及图像识别等任务。系统整体结构如图1所示。图中SDRAM用于存储OV7670采集的图像数据,SRAM用于识别部分缓存一帧采集得到的图像数据,便于Nios II处理器处理数据。而EPCS16则用于存放FPGA的配置数据。

2 系统硬件设计

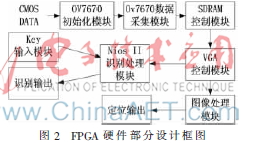

系统FPGA硬件设计部分如图2所示, 通过SCCB编程接口初始化OV7670 CMOS摄像头,由OV7670数据采集模块实时采集摄像头采集的数据,并将数据缓存在一片深度为512×8 bit的FIFO中,待FIFO存储满,由SDRAM 控制模块将数据发送到SDRAM存储。SDRAM 存储空间为640×480 B。同时,SDRAM等待VGA控制模块的读请求信号,从而将数据输送到另一片同样大小的FIFO中进行缓存,以备VGA控制模块读取。VGA控制器按照标准640×480@60 Hz时序将图像数据输出。图像处理模块接收VGA数据并通过对图像进行车牌粗定位、图像灰度化、中值滤波、Sobel算子边沿检测、图像二值化、车牌精定位等算法,实现对车牌的定位。同时,SOPC系统Nios II软核处理器也采集VGA控制模块的数据并缓存于SRAM中,从而实现对图像字符的分割、识别,并通过JTAG将识别结果反馈到控制台。

2.1 MATLAB算法验证

中国国内车牌大多数以蓝底白字为主,大小为440 mm×140 mm。车牌粗定位即利用车牌特有的蓝色背景为前提,通过将RGB图像转化为HSV制式的图像。根据深蓝色在HSV颜色空间中分布在V=0.4、S=1、H=240度处,淡蓝色分布在V=1、S=0.4、H=240度处[3]。通过扫描H、S、V分量,从而实现分离图像蓝色成分,即可实现车牌的粗定位。

图像灰度化:将粗定位后的彩色车牌图像灰度化,以减少图像数据的存储量,便于图像的存储及后续对图像的处理。图像灰度化后的车牌图像如图3所示。

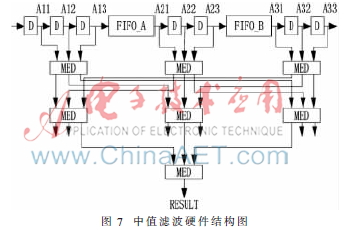

在FPGA中实现中值滤波,出于实际处理速度、处理效果和器件资源考虑,本系统选用3×3邻域窗口。这种方法比传统的冒泡排序法减少了逻辑资源的占用,却和其一样能找出中值,且只需经过3级的比较(即3个时钟周期的延时)就可以找出中值[4]。

系统采用Altera公司的DSP builder来完成该滤波器的设计。利用Verilog硬件描述语言,描述一个8位的3输入比较器,其功能可将输入的3个8位宽数据进行排序,分别以最大值、中值、最小值的形式输出。

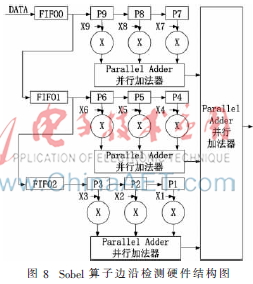

系统中图像边沿检测模块,采用的是Sobel算子,实现3×3领域像素的图像边沿检测。该算子是在以F(x,y)为中心的3×3邻域上计算x和y方向的偏导数,是一种将方向差运算与局部平均相结合的方法[5]。其边缘检测算子的卷积算子如图4所示。

系统采用3个深度为640的FIFO对数据进行缓存,在进行边沿检测时,以便于实时操作采集图像3行之内的数据,从而使得能够同时读取到图像3×3领域的像素值,以达到能够进行图像边沿检测算法的条件。通过设置灰度化后的像素阈值,从而实现图像的二值化,为后续的图像处理进一步减少存储容量,以利于后续的定位识别处理及存储。车牌图像二值化后的图像如图5所示。

在车牌定位部分的车牌精定位模块,采用图像在水平方向和垂直方向上进行投影的方法来实现车牌的精确定位。通过缓存的粗定位后的图像数据,实时扫描采集图像的两行与两列,对每行每列像素点1的个数进行统计,并计算相邻两行、两列的差值。通过利用车牌形态学特征,设定差值的阈值,从而可判断出车牌的准确长度与宽度[6],并通过设置长度与宽度的比例,进一步增强车牌定位的准确性。车牌精定位后的图像如图6所示。

2.2 FPGA硬件实现

FPGA硬件实现上,采用两片深度为512 bit的8位宽FIFO作为数据输入与输出缓存,图像数据采集模块将数据采集到写FIFO中,待FIFO写满,SDRAM控制器便将数据全部读出,并写入SDRAM,SDRAM的存储地址设定为640×480个。在图像处理算法模块部分的中值滤波模块,采用两个640像素的FIFO对前两行内数据进行缓存,通过7个3输入比较器对数据进行排序,取得其中值,该值即为此3×3领域中心的像素值[7]。该方法很好地滤除了图像高频噪声信号。中值滤波硬件结构图如图7所示。

在图像边沿检测模块,采用3个640×8 bit的线性FIFO缓存对3行内的数据进行缓存,同时采用9个乘法器对这3行内的3×3领域的各个像素进行加权,然后通过4个加法器求和,得到该3×3领域中心像素值。依次对整幅图像进行处理,从而实现图像的边沿检测。其Sobel边沿检测硬件结构图如图8所示。

在图像的二值化模块,通过采用一个比较器,对灰度化后的图像数据设定一个比较阈值,从而实现灰度图像的二值化。在图像的精定位模块,同时缓存图像粗定位后的两行两列数据,分别统计两行两列数据中的像素1的个数,同时设定阈值范围,判断得到图像精定位的上下左右边界值[8]。然后通过设定图像边界长度与宽度的比例,从而精确地实现车牌的定位。

3 系统软件设计

为更加灵活地实现车牌识别的功能,本设计采用Altera的32位处理器Nios II软核对图像数据进行进一步的分割识别处理。

图像数据由数据输入端口输入,经三态桥缓存于SRAM中,待Nios II处理器处理。按键PIO实现开始一帧图像处理的控制,控制车牌识别结果的输出。片上存储器OnchipMemory以及EPCS控制器用以实现Nios II 软核的正常运行。

在对车牌进行定位后,考虑到车牌字符的排放特点与字符间的微小间隙,采用垂直灰度法进行车牌字符的分割。字符识别部分采用的是模板匹配的方法。我国的车牌,字符标志的首位为汉字的省名缩写,次位为英文字母,再次位为英文字母或阿拉伯数字,末4位均为数字。由于实际可能出现的英文字母和数字字符数目不多,再基于Nios II软核的运算能力考虑,采用模板匹配方法进行字符识别。即将待识别的车牌字符矩阵与库内的标准字符矩阵对比,相似度最大的则认为一致[9]。

当车牌上的待识别字符归一化以后,依次与标准库中的模板进行匹配,即矩阵对应位依次做差,分别计算总的相同像素个数,则有最大相同数目的那一组数认为是相似度最大,用此时的标准模板所对应的数字或字母作为最终识别的结果。

4 测试分析及结论

系统测试根据对不同天气、拍摄角度、拍摄距离、车牌完整性等因素给出了综合测试与分析。测试结果显示在极端环境下,图像的对比度较低,识别率不高,一般情况下图像对比度较强,识别率较高。整体测试显示,本系统在较为理想的环境下,识别率可达到94%,白天识别率可达到98%;平均识别时间约为0.05 s。相比参考文献[9],其平均识别率提高了3%,识别速度提高了50%。

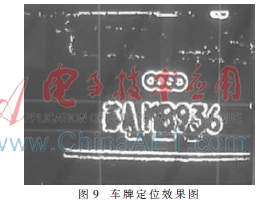

设计通过了Altera FPGA平台EP2C35实际板级验证测试,顺利地实现了对所采集的车牌图像进行车牌的定位与识别,其识别效果如图9所示,并从控制台得到了来自JTAG的车牌识别结果。由设计的整体资源消耗报告分析可知,其占用的FPGA内部逻辑资源相对较少。验证测试结果表明,该设计实现了小面积高速智能车牌的定位与识别。

参考文献

[1] 迟铁军,高鹏.国外智能交通系统发展状况分析及对我

国的启示[J].黑龙江交通科技,2009,32(2):111-114.

[2] Jia Wenjing,Zhang Huaifeng,He Xiangjian.Region-based

license plate detection[J].Journal of Network and Computer

Applications,2007,30(4):1324-1333.

[3] Wang Feng,Man Lichun,Wang Bangping,et al.Fuzzy-based algorithm for color recognition of license plates[J].Pattern Recognition Letters,2008,29(7):1007-1020.

[4] 张玲,刘勇,何伟.自适应遗传算法在车牌定位中的应用[J].计算机应用,2008,28(1):184-186.

[5] 谭熙,黄樟灿.基于自适应性的车牌定位新方法[J].计算机技术与自动化,2008,27(3):73-77.

[6] 谢剑斌,刘通,文特,等.基于多特征和加权模式相似性测度的车牌字符识别方法[J].计算机工程与科学,2008,30(8):36-38.

[7] CHANG S L,CHEN L S,CHUNG Y,et al.Automatic license plate recognition[J].IEEE Transactions on IntelligentTransportation Systems,2006,5(1):42-52.

[8] 梅林,刘锋.基于边缘检测与垂直投影相结合的车牌定位方法[J].甘肃科技,2009,25(3):16-17.

[9] 李姗姗,刘纯.基于FPGA车牌识别系统的设计与实现[J].软件,2012,33(3):72-74.