0 引言

随着计算机网络和嵌入式系统的快速发展,信息安全已成为广大用户关注的重点,而加密技术作为信息安全的利器,正发挥着重要的作用。加密系统目前已广泛应用在安全电子支付、金融智能卡、身份识别、生物特征识别、电子护照和可信计算等安全领域。传统的加密方法是通过在主机上运行加密软件来实现的,不仅占用主机资源,而且速度较慢。因此,基于芯片级的硬件解决方案成为保证信息安全的最可靠的途径,把所有关键数据的存储、运算都通过硬件实现,不占用主机资源,速度快、安全性高、成本低。以FPGA为代表的可重构硬件既具有物理安全性和高速性,又有软件的灵活性和易维护性[1],已经成为加密算法硬件实现的研究热点。

本文研究的是加密算法的一种可靠的、高效的硬件实现方案,采用了目前流行的电子设计自动化技术(Electronic Design Automation,EDA),在现场可编程门阵列(Field Programmable Gate Array,FPGA)上实现一种可重构的加密系统,提出一种基于可重组体系结构的设计原理和方法,该方法使得用户通过编程来改变芯片内部的电路结构,以匹配不同的加/解密算法,从而支持不同的加/解密算法在同一块FPGA芯片上的实现,以提高密码芯片的安全性和灵活性。

1 开发工具介绍

1.1 QuartusⅡ开发软件简介

QuartusⅡ是Altera公司推出的新一代开发软件,适合于大规模逻辑电路设计。它支持图形编辑输入法、基于硬件描述语言的文本编辑输入法以及内存编辑输入法等多种设计方法。作为一种可编程逻辑的设计环境,其强大的设计能力已经成为广大设计人员首选的开发工具。本设计采用的是Quartus II 9.0版本作为开发平台。

1.2 FPGA简介

1.2.1 工作原理

FPGA是目前应用最广泛的通用可重构器件,是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物,作为专用集成电路(ASIC)领域中的一种半定制电路而出现,既解决了定制电路的不足,又克服了原有可编程器件门电路数量有限的缺点。

1.2.2设计流程

基于EDA技术的FPGA设计流程如下[2]:

(1)设计输入:包括原理图输入法和HDL语言输入法。

(2)综合:依据给定的硬件结构和约束条件进行编译、优化、转换和综合,以获得门级电路甚至更底层的网表文件。

(3)适配:将网表文件配置于指定的目标器件中,使之产生最终的下载文件。

(4)仿真:让计算机根据一定的算法和仿真库,对EDA设计进行模拟,以验证设计,排除错误。

(5)编程下载:将适配生成的下载文件,通过编程器或编程电缆向FPGA芯片下载,以便进行硬件调试和验证。

(6)硬件测试:将载入了设计的硬件系统进行统一测试。

2 AES算法基本原理

AES(Advanced Encryption Standard,AES)是密码学中的高级加密标准,又称Rijndael加密法,代替了原先的DES算法,成为目前对称密钥加密中最流行的算法之一。AES是一个迭代的、对称密钥分组的密码,它可以使用128、192和256位密钥,并且用128 bit即16 B分组加密数据和解密数据,通过分组密码返回的加密数据的位数与输入数据的位数相同。迭代加密使用一个循环结构,在该循环中重复置换和替换输入的数据。大致步骤如下:(1)密钥扩展(KeyExpansion);(2)初始轮(Initial Round);(3)重复轮(Rounds),共9轮且每一轮又包括字节替代、行位移、列混淆、轮密钥加;(4)最终轮(Final Round)[3]。

以10轮算法为例,前9轮结构相同,除了第10轮由字节变换、行移位变换、轮密钥加3步组成外,其他9轮都由字节变换、行移位变换、列混淆变换、轮密钥加4步构成。

(1)SubBytes变换

在AES算法中,SubBytes变换是唯一的基于S盒的非线性置换,输入字节按照如下方式映射为一个新的字节:把该字节的低4位作为列值,高4位作为行值,在S盒中找到对应行列号的元素作为输出。所以S盒的性质直接决定了整个算法的成败。SubBytes变换的逆变换是InvSubBytes,它是通过建立并查找逆S-盒来实现的。

(2)ShiftRows变换

ShiftRows变换即行移位,将某个字节从一列移到另一列中,移位的线性距离是4 B的倍数,这种转换在一定程度上确保了某列中的4 B被扩展到了4个不同的列中。解密中ShiftRows的逆变换是InvShiftRows。

(3)MixColumns变换

列混淆变换MixColumns实现的是逐列混合,符合以下变换公式:

s′(x)=c(x)·s(x)mod(x4+1)(1)

其中,c(x)={03}x3+{02}x2+{01}x+{01}

列混淆变换的系数{01}、{02}、{03}是基于AES算法的执行效率考虑的,这些系数的乘法需涉及一次移位和一次异或运算。

(4)AddRoundKey变换

轮密钥加变换用于将输入或中间态S的每一列,与一个密钥字ki进行按位异或,即:

AddRoundKey(S,ki)=S?茌ki(2)

式(2)中ki由原始密钥k通过密钥扩展算法产生[4]。在解密过程中,AddRoundKey变换是自身的逆。

3 AES算法的硬件设计

AES算法中各运算部件都具有良好的统计特性,并行执行能力强,加、解密执行速度快,效率高。由于算法本身不需要繁琐的乘法运算,所有运算部件都可以通过查找表和组合逻辑来实现,使得AES算法的硬件实现方案成为可能。因此,本文采用FPGA芯片来进行设计和测试。

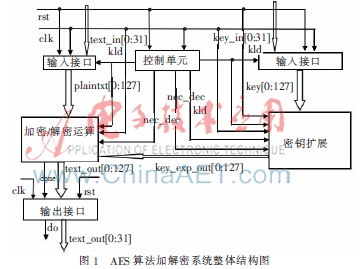

根据AES算法的基本原理和结构,结合自顶向下的设计步骤,将整个加解密系统分成4个相对独立的子模块,即接口模块、控制单元模块、加解密运算模块和密钥扩展模块。总体结构如图1所示。

3.1 接口模块

明文和密钥被输入接口模块分别传送到加解密运算模块和密钥扩展模块。因为明文和密钥输入都要求是128 bit,为避免整个模块输入/输出端口过于繁杂,分别使用4个32位的数据寄存器,在时钟的控制下,每次输入一组数据,需要利用4个时钟周期得到128 bit的数据,并进行串并转换。显然这种方法可大大减少硬件资源的消耗。解密运算结果由输出接口模块输出,利用并串转换在4个时钟周期后得到结果。

3.2 控制模块

控制模块负责启动加解密运算模块和密钥扩展模块工作,在时钟脉冲控制下,控制模块产生信号以控制加解密模块中的SubBytes、ShiftRows、MixColumns、AddRoundKey各部件有序工作。信号的控制由状态机实现,每一次输入新的明文或密钥时,动作是否完成由状态机的信号来进行判断。状态机信号为忙状态,表示加/解密运算正在进行,需等待;信号为空闲状态,则加/解密运算已完成,加解密运算模块与密钥扩展模块启动,分别接收原始明文和密钥,开始新一组数据的加解密运算。

3.3 加解密运算模块

为了尽可能减少硬件资源的消耗,采用基本迭代反馈方式,只用一个轮变换模块进行迭代,在10个时钟周期内完成一个分组运算。

用VHDL语言中的元件例化语句描述出各子模块之间连线关系,部分代码如下:

addkey1:addroundkey port map(regout0,reg10(0),data0);

sbox1:sbox4word port map(clk1,contr1,sboxout1);

shiftrow1:shiftrow port map(sboxout1,shiftout1);

mixcolumn1:mixcolumn port map(shiftout1,mixout1);

在加解密运算模块中,要尽可能地使用时序逻辑,以保证每个元件的输出信号是稳定的,从而避免毛刺现象的产生,以提高整个系统的可靠性。

3.4 密钥扩展模块

AES算法中每一轮的操作都包括与当前轮的轮密钥进行轮密钥加的操作。除第一轮的密钥为初始密钥外,其他每一轮的轮密钥都是由子密钥扩展而成的,也称为扩展密钥[5]。密钥扩展模块负责通过输入的初始密钥生成每一轮轮变换所需要的轮密钥。采用流水线方式进行设计,即轮密钥的生成与加密过程中的轮变换并行完成,在进行某一轮轮变换的同时,也生成了下一轮的128 bit轮密钥。以此类推,在分组进行第k轮(k<10)运算时,并行计算第k+1轮所需的轮密钥[6]。由于这种流水线方式采用了时间并行技术,大大提高了加密速度,节省了FPGA芯片的存储器资源,是一种可行的方案。

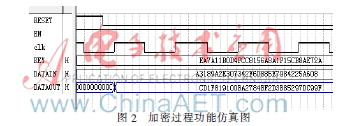

4 仿真分析

本文实验环境为Intel Core 2.0 GHz,2 GB内存,Windows 7操作系统,系统元件设计采用VHDL语言和原理图方法,在Quartus II 9.0环境下进行综合、适配和仿真,最终的硬件载体是CycloneIII系列的FPGA芯片,型号为EP3C40F780C8。图2是本系统的仿真波形图。

输入128 bit明文datain为:

A3189A2E307342F6D885E7984225A608

输入128 bit密钥key为:

EA7A11B0D4FCC8156A8A1F15CB8AE72A

输出128 bit密文dataout为:

CD1F819100BA2784BF2D3B85297DC99F

从得到的仿真数据可以看出,输出的密文数据正确、有效,验证了本文中利用FPGA实现的加密算法能够有效地运行。

5 结论

本文介绍了基于AES标准加密算法的FPGA设计方案,通过QuartusII软件平台实现对AES算法的设计与仿真,并进行加密验证,将低成本、低功耗的FPGA芯片作为最终硬件载体,该芯片具有高速并行处理能力和可重构能力。结果表明,用硬件实现加密算法并且封装到芯片中,不易被外部攻击者读取或更改,有较高的物理安全性,且能最大化加密速度和最小化电路面积,利用诸如流水线和查找表等优化技术,可极大地提高系统效率。利用该加密算法所设计出来的加密系统以其可重构性、高性能、低功耗的优势,势必在信息安全市场上取胜。

参考文献

[1] 赵峰,马迪明,孙炜.FPGA上的嵌入式系统设计[M].西安:电子科技出版社,2008.

[2] 潘松.EDA技术实用教程[M].北京:科学出版社,2005.

[3] 孙瑜.基于FPGA的数据加解密系统设计[D].大连:大连海事大学,2010.

[4] Dong Xiaoli, Hu Yupu, Wei Yongzhuang, et al. A new method for meet-in-the-middle attacks on reduced AES[J]. China Communications, 2011(8):21-25.

[5] 韩津生,林家骏,周文锦,等.基于FPGA的AES核设计[J].计算机工程与科学,2013,35(3):80-84.

[6] 张慧,汪烈军,于海涛,等.基于可编程器件的Rijndael加密算法优化实现[J].新疆大学学报(自然科学版),2013,30(4):455-459.