文献标识码: A

DOI:10.16157/j.issn.0258-7998.2015.11.014

中文引用格式: 刘博,刘欣,樊晓华,等. 一种超低静态功耗LDO的设计[J].电子技术应用,2015,41(11):51-53,57.

英文引用格式: Liu Bo,Liu Xin,Fan Xiaohua,et al. An ultra-low quiescent current LDO[J].Application of Electronic Technique,2015,41(11):51-53,57.

0 引言

近年来,各种便携式电子产品的普及以及功能的日益增加,对电源管理IC提出了更高的要求,如高集成度、高效率以及低成本等。在整个电源管理IC领域中,LDO以其电路结构简单、占用芯片面积小、输出电压相对稳定等优点,牢牢占据着电源管理IC市场很大的份额。随着电子产品功能的日益复杂与多样化,消费市场对其续航要求也在日益增高,这就要求电源具有更高的电流效率,其定义如下式所示[1]:

其中ILoad为负载电流,Iq为静态电流。电流效率说明了LDO电路的存在对电源工作时间有一定程度的降低。由上式可知,当负载电流很大时,电流效率主要由负载电流决定。然而,对于很多应用来说,电路通常工作在一个低负载电流的情况下,这时静态电流的大小直接决定了电源的工作时间。

为解决上述问题,本文设计了一种超低静态功耗的LDO电路,其典型静态工作电流为500 nA,这样极大地提高了在低负载情况下整个电路的电流效率,延长了电源寿命。此外,本文还采用了一种新颖的补偿方式,在不增加静态电流的情况下保证LDO的稳定性。

1 LDO电路的基本原理与设计

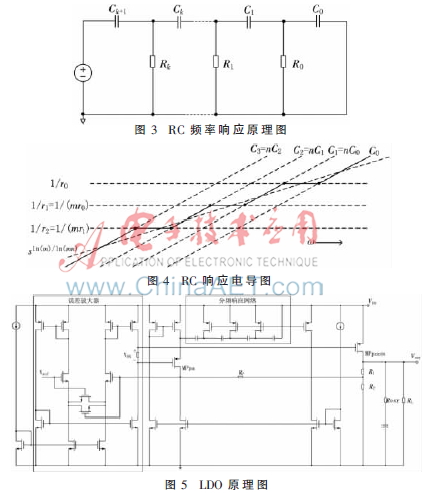

图1是本文设计的LDO的基本结构框图,主要包括带隙基准电路(Bandgap)、误差放大器(EA)、调整管(Pass Transistor)以及反馈电阻(R1、R2)。其中带隙基准电路为误差放大器提供低温漂、高精准的参考电压Vref,误差放大器将输出反馈电压与参考电压进行比较,并放大其差值来控制调整管的导通状态,从而得到稳定的输出电压。输出电压值由下式所示:

2 误差放大器的设计

图2给出了误差放大器的原理图,采用一种对称性运算跨导放大器(Operational Transconductance Amplifier,OTA),其中包括一个差分对和三个电流镜。输入差分对的负载是两个相同的电流镜,并提供了一个增益为A的电流增益。显然由于整体电路的对称性,在版图设计时会有很好的匹配。M3与M4工作在线性区,提高了误差放大器的线性度[2]。其低频增益为:

AV=gm1ARout(3)

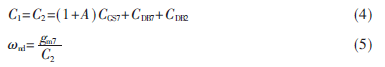

由于只有输出节点是高阻,其他节点电阻约为1/gm左右,因此主极点位于输出节点,在节点1、2、3处产生非主极点。从图中可以看出,C1与C2都是交流接地的,对于对称的差分电路来说,它们的交流通路是相同的,因此有相同的极点。对于节点3,注意到它是位于单端输出另一端的节点,在这一节点会产生一个极-零点对,零点大约是极点的两倍,因此对于相位裕量的影响可以忽略[3]。事实上,电路只产生一个非主极点。因此有:

可以看到次级点要受到A的影响,A越大,次级点频率越低,这也限定了A的最大值。

对于普通采用PMOS作为导通管的LDO来说,通常需要一个电压缓冲(buffer)电路来驱动导通管,以便将由其栅极电容产生的极点推到环路带宽外。然而,这种方式却不适用于低静态电流LDO,因为buffer本身会消耗较大的电流。因此,可以在LDO的反馈环路中加入一个零点以抵消导通管栅极处的极点或者输出电容产生的极点。如图1所示,C1是导通管MPpass栅源电容与沟道电容总和,Cc是栅漏电容,gmi为误差放大器的等效跨导,ro为其等效输出电阻,gmo为导通管MPpass的跨导,CL与RL分别为负载电容与电阻。显然,在导通管栅极与输出端各产生一个极点,其传输函数为:

为了补偿次级点,在电路中添加一个并联在导通管MPpass两端的MOS管MPpa,其宽长比相对于导通管的比例很小,这样导通管栅极电压通过MPpa转化为电流注入到反馈电路中,可以得到一个零点ωz为:

通过适当选取 Rf+R2/R1的值,可以对电路进行有效的补偿,并且不随负载电容的变化而变化。当该值大于1时,零点的频率低于次级点的频率,补偿效果会很好,但是当这个值过大时会影响交流信号通过导通管的主支路,从而导致输出电压瞬态响应变差;当这个值远小于1时,又会使补偿效果变差。因此,在实际电路设计中要进行折中。

这种补偿方式可以解决交流补偿,但在直流方面还存在问题。首先,MPpa会将直流电流注入到反馈电路中,并且这个电流会随着负载的变化而变化,因此会造成输出电压失调,并且降低了负载调整率。此外,当负载电流很小时,gmp的值也会很小,无法为电路提供有效的环路补偿。对于后一个问题,可以在MPpa和MPpass管的栅极间添加一个电阻,为Mpa的栅极提供一个电压VOS,这样即使MPpass进入亚阈值区,并联路径仍然会通过MPpa管提供一个有效的电流信号。为解决前一个问题,可以在MPpa源漏端加入两个电流源,这样通过MPpa的电流大小不会随负载的变化而变化,同时也几乎不会有电流流入反馈网络而造成输出电压失调。对图1 的电路作小信号分析可知,由于电流源的高阻特性,需要在MPpa源极接一个较大的电容Cp以保证交流信号从其栅极转换到漏极,可以等效为一个高通滤波器,其截止频率为gmp/Cp。若当Cp较小时,截止频率位于零点ωz的右侧,会造成一个增益凹陷,导致系统不稳定。因此需要有:

如果在空载情况下,流过Mpa管的电流为1 nA,gmp=40 nA/V,gmo=200 nA/V,CL=1 F,则可得到Cp约为40 nF,这样大的电容在片上是很难实现的。

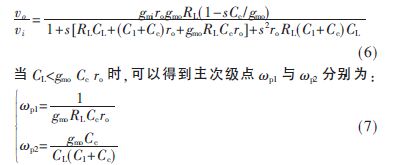

上述提到的增益凹陷来自于两个信号,一个是MPpass漏极信号,它对于电容CL有一个1/s的频率响应,另一个是MPpa的漏极信号,它对于电容Cp有一个s的频率响应,这两个信号在电路反馈端互相抵消。为了解决这个问题,本文采用了一种RC频率响应网络的方法来代替Cp。在RC网络中,Ck+1=nCk,Rk+1=mRk,其中k为该网络的级数,如图3所示,电容为串联关系,而电阻为并联关系。图4给出了每个元件在对数坐标下的电导图,斜线为电容的电导线,直线为电阻的电导线,它们分别为平行且等间距,电容与电阻的曲线相交。在高频情况下,电容C0的电导值在串联电容中起主导作用,随着频率降低,该值不断降低,直到遇到电阻R0的电导曲线。当频率继续降低时,电阻R0的电导值起主导作用并不随频率变化,直到遇到电容C1的电导曲线。以此类推可以得到该网络的频率响应曲线,可以看出该曲线是在电容与电阻之间变换的分段线性曲线,频率范围为1/R0 C0到1/[n(mn)kR0 C0]。该网络频率响应可以近似为一个sa的分频响应网络,其中a=lgm/lg(mn)[4]。随着网络级数的增加,低频的电导交点会继续下延。为得到更好的近似曲线,应该使用较小的m与n和较大的k值,但这样做会增加电路的复杂性与面积,这里采用m=n=k=2,则有a=1/2,这使得MPpa漏极的频率响应变为s1/2,可以很好地避开增益凹陷。同时,按照前面的假设,并设R0=1/2gmp,高通截止频率为gmp/C0,则C0只需要大于2.5 pF即可实现足够的频率补偿。为节省面积,采用MOS管代替网络中的电阻,整体电路如图5所示。

3 仿真结果

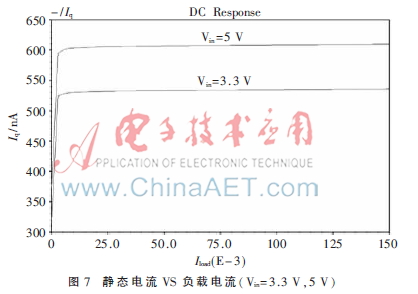

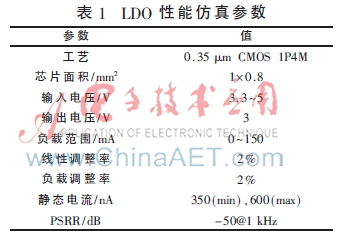

电路采用CSMC 0.35 μm工艺,使用Cadence Spectre对设计的LDO进行仿真。图6为电源电压变化下LDO电路在空载与满载下的静态电流,图7为负载变化下的静态电流,表1给出了整个LDO系统的性能仿真参数。

4 结论

本文设计了一种超低静态功耗的LDO电路,正常工作下最大静态电流为600 nA,最小静态电流为350 nA,有效地提高了电源的工作效率,显著延长了工作时间。同时,本文采用一种新颖的分频响应网络对电路进行补偿,在保证电路稳定工作的基础上尽可能降低了静态功耗。本文设计的LDO采用0.35 μm标准CMOS工艺,输入电压为3.3 V~5 V,输出电压为3 V,最大负载电流为150 mA。

参考文献

[1] RINCON-MORA G A,ALLEN P E.A low-voltage,low quiescent current,low drop-out regulator[J].IEEE J Sol StaCirc,1998,33(1):36-44.

[2] KRUMMENACHER F,JOEHL N.A 4-MHz CMOS con-tinuous-time filter with on-chip automatic tuning[J].IEEE J Sol Sta Circ,1988,23(3):750-758.

[3] KAY M.Design and analysis of an LDO voltage regulator with a PMOS power device[Z].Preliminary paper pending publication,Texas Instruments.

[4] CHAREF A,SUN H H,TSAO Y Y,et al.Fractional systemas represented by singularity function[J].IEEE J Trans.On Auto Control,1992,37(9):1465-1470.