文献标识码: A

DOI:10.16157/j.issn.0258-7998.2015.11.016

中文引用格式: 朱述伟,黄锐敏, 杨清河. 基于FPGA CFGLUT5的可变FIR滤波器的实现[J].电子技术应用,2015,41(11):58-60,64.

英文引用格式: Zhu Shuwei,Huang Ruimin,Yang Qinghe. The variable FIR filter implement based on FPGA CFGLUT5[J].Application of Electronic Technique,2015,41(11):58-60,64.

0 引言

在现代软件无线电的数字信号处理系统中,例如脉冲压缩体制雷达[1],需要在不同的工作模式下切换。不同工作模式对应着不同的频率响应特性,对应一组滤波器系数;因此在实现结构上要求滤波器可以动态变化。如果把每种模式的滤波器单独实现,不但需要占用大量的面积,而且会使得系统结构松散、资源浪费和时序难以一致。然而,该系统不同的工作模式具有相同的实现结构和数据通路,且输入数据是一致的,因此可以作为一个整体实现,即将其设计为由一个输入数据端口、多套系数存储器以及一个数据输出端口组成的可变滤波器。它的优点是不用离线重新设计一个新的滤波器便可获得动态可变的滤波特性。本文将介绍如何在传统可变滤波器基础上利用Xilinx FPGA CFGLUT5的动态配置功能实现可重用结构共享来减少资源的消耗,提高可变滤波器的硬件效率,达到通过简单的控制实现软件无线电系统不同工作模式之间的切换。

1 传统的可变FIR滤波器设计方法

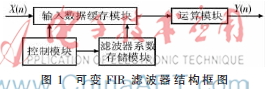

可变FIR滤波器一般可以分为4个模块:输入数据缓存模块、滤波器系数存储模块、运算模块及控制模块。输入数据缓存模块及运算模块在整个系统中可以共享以便节省资源,同时为了保证采样频率与系统时钟频率之间关系的一致,设定每组滤波器的系数长度相同,为此将长度较短的滤波器系数补零。整个可变FIR滤波器的结构框图如图1。

滤波器系数存储模块设计原则是根据滤波器基本结构[2]如串行、并行尽可能少的占用存储资源,同时便于读系数的设计,为此设计方法采用分段存取。例如有4套滤波器系数,每组滤波器系数长度均为16,则存储空间深度可以定义为64。0~15号地址存储第一套滤波器,16~31号存储第二套滤波器系数,32~47号存储第三套滤波器系数,48~63号存储第四套滤波器系数。这样,滤波器系数地址可以由一个模值为16的4位计数器和2位控制位共6位构成。当控制位为00时,地址变化范围为0~15,为01时地址变化范围为16~31,当控制位为10时,选中地址范围为32~47,当控制位为11,选中地址范围为48~63。

控制模块完成的主要工作是系数的切换,输入数据的读取与写入。不同的结构需要不同的控制数据。

2 改进的可变FIR滤波器设计方法

2.1 DA算法结构滤波器

基于FPGA的DA算法[3]是一种以实现乘加运算为目的的运算方法,由于传统的乘加运算消耗较多的硬件资源,转而改进采用基于FPGA的LUT查找表[4]和移位相加来实现。由于FPGA基本模块正是由LUT构成,而且移位和相加算法实现起来更加容易有效。所以DA算法可以极大地减少硬件电路的规模, 提高电路的工作执行速度。其主要原理如下。

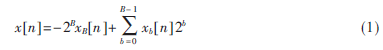

式(1)中x[n]是二进制补码表示的有符号输入信号,表示x的第n次采样值,输入的数据位宽为M=B+1位。xb[n]表示x[n]的第b位。假设滤波器系数为序列h[n],滤波器输出为y[n],得到滤波器输出可以表示为:

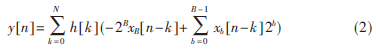

将式(2)展开,重新分别求和得

式(3)的h[k]xm[n-k](m取B或b)的部分可以通过查找表映射来计算出。对于长度为N的FIR滤波器,只需构造一个深度为N的存储器查找表,通过M次查找表运算,M-1次移位运算和M-1次加法运算即可完成整个乘加运算。这种结构极易使用流水线结构,且运算速度受限于加法和查找表运算速度,与乘加运算的数据长度没有关系。

本文采用Xilinx公司的XC6SLX75T器件为例,设计长度为32的线性相位可变FIR数字滤波器。利用线性相位的对称性可以将滤波器系数减半为16个滤波器系数,假定滤波器输入信号位宽为11位,滤波器的系数量化为12位,滤波器输出数据位宽30位,共有4套滤波器系数。为防止滤波器系数相加溢出则需要15位宽的存储器。4套滤波器系数需要控制位为2位。由此得到滤波器系数存取模块如图2所示。

2.2 CFGLUT5的基本原理

FPGA内部资源CFGLUT5[5]是一个5输入的动态可重构查找表,能够在电路运行时改变电路的LUT的逻辑功能。其结构图如图3所示。采用CDI输入引脚,一个新的初始值可以同步串行移位输入存储到CFGLUT5中。CE为使能输入CDI的接口,O5、O6为输出逻辑值,大小基于当前加载到查找表的初始值和当前选定的I0~I4输入引脚。同时可以分别将O5、O6输出形成两个不同的子集,共享输入分时复用,形成双通道的查找表。CDO接口是扩展初始值接口,作为级联CFGLUT5单元使用,每个单元的CDO引脚接入到下一个CFGLUT5单元的CDI输入接口。这将允许一个单一的串行数据链(每个单元32位)来重新配置多个LUT,可以来扩展输入数据的位数。

2.3 改进DA算法的可变FIR滤波器

许多FPGA芯片都具有可重构的LUT基本单元,例如Xilinx FPGA的重构模块CFGLUT5。本文通过使用CFGLUT5来改进传统DA算法[6],从而实现动态可重构的可变FIR滤波器,利用可以动态重配置的LUT可以将多套滤波器系数查找表共享为一套查找表。只需要32个工作时钟即可以完成滤波器系数查找表的一次重构,减少了资源的占用,降低了成本。现对上述传统DA算法改进,设计上述同样的可变FIR滤波器结构如图4所示。

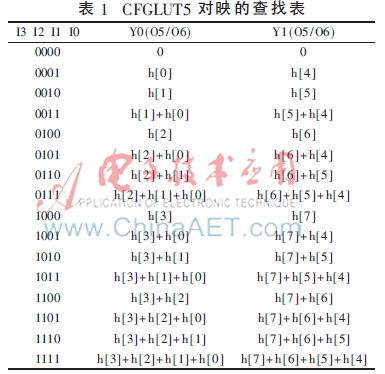

图4中M(0)~M(15)为滤波器对称系数的输入信号相加后信号,经过数据结构转换,得到M(0)~M(15)的最低位组成16位的数据,作为查找表的寻位地址,并依次再取M(0)~M(15)的次低位,这样一直取到最高位。由于输入数据为11位,则对称相加后数据M位宽12位,共 12次查找运算,所以取计数器count为12进制。其中M(0)(count)~M(15)(count)分别表示M(0)~M(15)的第count位(count取值为0~11的整数)。为改进传统DA算法所占用的ROM资源,采用分割查找表的方式,将传统DA算法16位ROM地址线,改为4个4输入地址线的CFGLUT5模块Y0~Y3来存储。令所有CFGLUT5的I4为高电平,则滤波器前8个系数的查找表Y0、Y1如表1所示。滤波器后8个系数同样按表1存储Y3、Y4。

滤波器系数量化为12位,则O5/O6输出值为保证不溢出则需要14位存储如图3所示,同时将数据拆分为从高位到低位存储,例如当Y0的地址位为1000时Y0(0)~Y0(13)分别表示存储值h[3] 的二进制补码数据最高位到最低位。在将Y0、Y1、Y2、Y3的每个可重构CFGLUT5的输出值相加后,为防止数据相加后溢出增加两位位宽来存储相加值,再送入移位寄存器。每送入一次相加后的数据,移位寄存器向左增加一位移位,直到向左移动11位后又回到向左移动0位,不断循环。控制器控制重构CFGLUT5的映射表的更新,当切换滤波器系数时,控制CFGLUT5的CE和CDI信号,在经过32个CLK时钟后,查找表Y0、Y1完成更新,对应为切换的滤波器系数。累加器由控制器控制使其经过11次累加和1次减法后输出滤波器数据,并清零,则Y[n]为滤波器输出数据。

为便于切换滤波器的简单操作,同样还需要一个滤波器系数存储模块,存储方式不同于传统DA算法的存储结构查找表,按照传统的串行结构存储,同时在控制器中加入滤波器系数转换运算电路。将按顺序存储的滤波器系数,通过简单加法运算转化为CFGLUT5查找表的结构的系数。

3 性能分析及实验结果

取线性可变FIR滤波器的系数长度为N,输入数据位宽为W1,滤波器量化位数为W2,滤波器套数为L,则可以估算消耗资源如下:

传统DA算法结构存储占ROM大小:

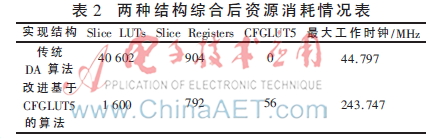

设计上述实验可变FIR滤波器传统DA算法消耗ROM大小为4×16×216=4 Mb,而当采用改进DA算法结构只需要增加56个CFGLUT5和滤波器系数转换运算消耗的68个加法器可以将ROM消耗减少到4×12×16=0.75 Kb,容易工程实现。现在Xilinx公司的XC6SLX75T器件上采用分布式ROM实现上述可变FIR滤波器,综合分析得到如表2所示实验数据。

从表2的实验数据可以看出改进传统DA算法后实现上述滤波器LUT的消耗减少了约25倍。最大工作时钟提高了近6倍左右。

4 结论

本文介绍了可变FIR滤波器的设计,并在传统DA算法结构上对资源消耗及工作速度进行了改善和优化。基于FPGA的CFGLU5的DA算法实现了对称结构FIR滤波器动态可重构设计,这种算法相比于传统DA算法的优势就是在运行中动态可重构FIR滤波器,共享了一套可重构查找表的方法从而实现可变FIR滤波器的功能,同时利用CFGLUT5的O5/O6不同输出接口,也可实现FIR滤波器的双通道功能,可同时处理2路不同信号,在节约资源的同时,可以增加实现的灵活性。最后通过FPGA仿真分析了CFGLUT5的DA算法的可变FIR滤波器,其结果表明在满足工作模式切换性能的同时可以明显减少占用的逻辑资源(LUT)和提高系统速度。

参考文献

[1] 潘林.基于FPGA的雷达脉冲压缩系统的研究与实现[D].上海:上海交通大学,2008.

[2] Uwe Meyer-Baese.Digital signal processing with field programmable gate arrays[M].BerLin:Springer,2007.

[3] 李姮,田克纯.一种基于FPGA的分布式FIR数字滤波器设计[J].电声技术,2012(10):28-32.

[4] 闫永鹏,于海勋.一种基于LUT的改进FIR滤波器的设计[J].微电子学,2010,40(5):694-696.

[5] Xilinx,Inc.Spartan-6 Libraries Guide for HDL Designs[J/OL].Xilinx,2013.http://www.xilinx.com/support/documenta-tion/sw_manuals/xilinx14_7/spartan6_hdl.pdf.

[6] KUMM M,MOLLER K,ZIPF P.Dynamically reconfigurable FIR filter architectures with fast reconfiguration[C].Darmstadt:IEEE,2013.