摘 要: 随着电子信息技术的不断发展,电子系统模块化的设计思想已经深入人心。因此,加强软件和硬件模块设计经验的相互借鉴意义重大。针对这种情况,借助于有限状态机理论,提出了一种将C程序转化成Verilog HDL描述的具体方法。同时,详细介绍了有限状态机理论,分析了在利用有限状态机进行设计时应该遵循的准则,并给出了一个具体的转化实例和最终的仿真结果。从仿真结果可以看出此方法是可行的。

关键词: 有限状态机(FSM);Verilog HDL;硬件设计;C程序

0 引言

近年来,电子系统的模块化设计思想越来越成熟,在一些实际的电子系统设计过程中,通常将整个系统分成软件和硬件两个系统分别进行设计,然后再进行整合,而一些比较成熟的综合开发工具使得软件和硬件的设计流程更加统一。在硬件设计过程中主要使用可编程逻辑器件(PLD),形成电路网表结构,实现具体的逻辑,这样的配置可以实现用于软件用途的硬件[1]。

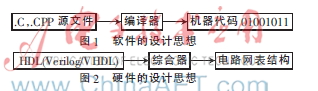

但是,软件设计的思想和硬件设计的思想是截然不同的。软件设计过程中首先是通过具体的算法描述实际的问题,再通过一些具体的编程语言去编写程序,然后通过相应的编译器编译连接,生成机器可以识别的二进制代码,最后这些代码在具体的微处理器上执行[2]。而对于硬件的设计则是通过一些比较成熟的综合工具将HDL编写的代码综合成实际的电路网表结构,最终形成具体的电路结构。图1和图2分别表示了两者设计思想之间的区别。

因此,如何实现C程序和Verilog HDL之间的转化就尤为重要。下文将重点论述如何借助于有限状态机,将C程序转化为Verilog HDL,并给出了其理论依据和具体的实现步骤。

1 有限状态机理论

有限状态机(Finite State Machine,FSM)是表示有限个状态以及在这些状态之间的转移和动作等行为的数学模型,状态机用来描述发生有先后顺序或者有逻辑规律的事情。状态机是对一些具有逻辑顺序或具有时序规律的事件进行描述的一种方法。

利用有限状态机进行设计有以下几个优点:综合器易于进行优化;较容易构成性能良好的时序逻辑模块;整个结构模式简单,层次分明,易读易懂,而且容易进行排错;运行模式类似于CPU的运行模式,可以进行顺序控制;系统的可靠性高,运行状态稳定。

有限状态机设计的重点在于状态的划分、过程的描述方式和状态的编码方式。在状态的划分过程中要明确每个状态的输入输出和状态之间的转移条件。

有限状态机的过程描述方式可分为单过程描述、双过程描述和三过程描述。在实际的有限状态机设计时更多的是采用双过程和三过程进行描述。双过程的描述有利于综合器优化代码,也便于阅读和维护,缺点是组合逻辑的输出可能会产生毛刺[3];三过程的描述与双过程描述相比,虽然代码的结构较复杂,但是没有毛刺的输出,而且有利于综合;单过程的描述会使得代码相对比较冗长,难以修改和调试,不利于代码的长期性维护,不利于附加约束,优化综合效果差,会导致逻辑速度变慢,资源消耗增多,一般情况下不采用这种过程描述方式[4-5]。

通常对于FPGA器件来说,采用一位热码编码可以有效提高电路的速度和可靠性,也有利于提高器件资源的利用率。在实际的设计过程中,更多的是采用One-Hot编码方式进行编码[6]。

2 理论依据和具体实现步骤

C语言作为一种面向过程的程序设计语言,在程序设计的过程中首先要分析出解决问题所需要的步骤,然后用函数把这些步骤一步一步地实现,在使用时逐步去调用这些函数,从而解决这些问题[7]。有限状态机正是将一个Verilog HDL程序中要表述的问题划分成不同的状态进行解决,通过状态的不断转换从而实现分步解决问题的目的,这与C程序的语句执行方式是相同的。因此,可以借助于有限状态机,用Verilog HDL去实现C程序。下面是将C程序转化为Verilog HDL进行描述的具体步骤:

(1)对于一个完整的C程序,先用算法流程图将其整个程序流程详细表述出来;

(2)根据程序的实际要求,将整个算法流程分成若干个状态,确定好每个状态的输入输出和状态之间的转换条件,用状态转移图描述整个算法流程图;

(3)用Verilog HDL描述其状态转移图,然后进行综合,最后进行仿真验证;

(4)在划分状态时应注意相同状态的合并,减少不必要的状态,简化程序。

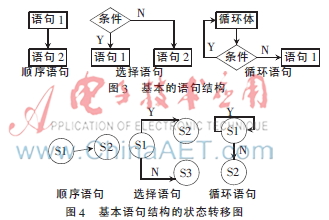

可以根据下面的基本单元模块用状态转移图描述算法流程图。图3所示的顺序语句、选择语句和循环语句是构成一个C算法流程图的基本单元,图4是其基本单元的状态转移图。

3 设计举例及其C程序表示

下面讲述一个利用C语言编写的、以51单片机作为微处理器实现的一个汽车尾灯控制程序,已知汽车左右两侧各有4个尾灯。要求:(1)当汽车正常行驶时所有的灯全灭;(2)刹车时所有的灯全亮;(3)左拐弯时,只有左侧四个灯闪烁;(4)右拐弯时,只有右侧的四个灯闪烁。先画出整个程序的算法流程图如图5所示,其中S1用来检测刹车信号,S2用来检测左拐弯信号,S3用来检测右拐弯信号。

如下是用伪代码表示的为51单片机编写的C程序:

#include<reg52.h>//头文件

/*用开关S1产生刹车信号,开关S2产生左拐弯信号,开关S3产生右拐弯信号*/

sbit S1=P2^0;//开关S1按下表示产生刹车信号

sbit S2=P2^2;//开关S2按下表示产生左拐弯信号

sbit S3=P2^4;//开关S3按下表示产生右拐弯信号

void keyscan();//按键信号检测

void main()

{

while(1)//循环检测

{

keyscan();//不断扫描按键,检测是否有信号产生

switch(k)//判断检测到的信号类型

{

/*P1口的低四位表示左侧的四个灯,高四位表示右侧的四个灯,低电平点亮*/

case1:P1=0x00;break;//刹车信号,所有灯全亮

case2:P1=0xF0;break;//左拐弯信号,左侧灯闪烁

case3:P1=0x0F;break;//右拐弯信号,右侧灯闪烁

default:P1=0xFF;break;//正常行驶,所有灯全灭

}}}

4 Verilog HDL描述及其仿真

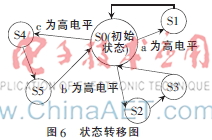

下面用Verilog HDL来描述上述C程序。首先根据图5的算法流程图画出状态转移图,如图6所示。将其整个算法流程分成S0~S5共6个状态,其中S0为初始状态,检测信号的产生;S1状态用来处理刹车信号;S2、S3状态用来处理左拐弯信号;S4、S5用来处理右拐弯信号。

用Verilog HDL描述图6的状态转移图,其完整代码如下所示:

module ex(clk,qout,a,b,c);

/*输入信号a,b,c为高电平时分别表示刹车信号,左拐弯信号和右拐弯信号*/

input clk,a,b,c;

/*输出信号qout的低四位表示左侧的四个灯,高四位表示右侧的四个灯,其中低电平有效*/

output reg[7:0]qout;

reg[4:0]current_state,next_state;

/*采用One-Hot编码方式进行编码*/

parameter s0=5′b00000,s1=5′b00001,

s2=5′b00010,s3=5′b00100,

s4=5′b01000,s5=5′b10000;

always@(posedge clk)

current_state<=next_state;

always @(posedge clk)

begin

case(current_state)

s0:begin if(a)next_state<=s1;else if(b)

next_state<=s2;else if(c)

next_state<=s4;

end

s1:next_state<=s0;s2:next_state<=s3;

s3:next_state<=s0;s4:next_state<=s5;

s5:next_state<=s0;default:next_state<=s0;

endcase

end

always@(current_state)

begin

case(current_state)

s0:qout<=8′b11111111;

s1:qout<=8′b00000000;

s2:qout<=8′b11110000;

s3:qout<=8′b11111111;

s4:qout<=8′b11111111;

s5:qout<=8′b00001111;

default:qout<=8′bzzzzzzzz;

endcase

end

endmodule

图7为波形仿真图,从图中可以看出:(1)当a为高电平时,产生刹车信号,qout信号在S1状态输出低电平;(2)当b为高电平时,产生左拐弯信号,qout信号的低4位在S2、S3状态分别输出低电平和高电平,产生闪烁信号;(3)当c为高电平时,产生右拐弯信号,qout信号的高4位在S4、S5状态分别输出低电平和高电平,产生闪烁信号;(4)从(1)~(3)可以看出其仿真结果是正确的,符合程序的基本要求,文中的方法是可行的;(5)用三过程进行描述时,无毛刺的输出,而且容易进行综合,采用One-Hot编码方式可以提高电路的速度和可靠性,同时也可以提高器件资源的利用率。

5 结论

通过上文的表述,借助于有限状态机,可以参考文中的方法实现用Verilog HDL描述C程序,从而可以通过实际的电路结构来实现软件程序的功能,这种方法也可以实现Verilog HDL程序和C程序之间的相互转换。同时,文中也归纳出在利用有限状态机进行设计时应该遵循的原则。

参考文献

[1] 杨海钢,孙嘉斌,王慰.FPGA器件设计技术发展综述[J].电子与信息学报,2010,32(3):714-723.

[2] 范华,秦茂玲,张俊.透视C程序设计语言[J].计算机技术与发展,2008,16(6):64-66.

[3] 王春旭,周晓平,王黎黎.基于FPGA的Verilog HDL语言设计优化[J].电子元器件应用,2009,10(11):45-47.

[4] 魏芳,刘志军,王立华.基于Verilog HDL的可综合有限状态机设计[J].电子工程师,2006,32(6):8-10.

[5] 刘小平,何云斌,董怀国.基于Verilog HDL的有限状态机设计与描述[J].计算机工程与设计,2008,29(4):958-960.

[6] 龚书涛,吕国强,彭良清.在FPGA中状态机的编码方式[J].电子工程师,2005,31(11):51-52.

[7] 丁亚涛.C语言程序设计(第二版)[M].北京:高等教育出版社,2006.