摘 要: 针对视频监控终端设备中的视频实时显示、编码数据本地存储备份等双重需求,设计了一种基于DM365视频处理芯片、H.264压缩技术、嵌入式Linux操作系统的双码流视频监控终端设备。给出了系统的总体软硬件结构,重点阐述了视频处理子系统模块(包括视频前端采集模块和视频后端显示模块)以及视频编码模块。测试结果表明,系统实时监测性能良好,本地存储的编码数据清晰稳定,具有很强的实用性和广阔的发展前景。

关键词: 视频监控;DM365;ARM

0 引言

随着网络技术、视频编解码技术、信息处理技术在安防领域中的应用日趋成熟,视频监控系统的发展也从最初的模拟视频监控系统发展到了如今的网络数字视频监控系统[1]。以往视频图像处理算法主要由DSP处理,但是随着算法复杂度的增加及视频分辨率的提高,传统DSP逐渐无法胜任这方面的工作[2]。为此,需要新的处理器架构来提高视频算法的并行性与带宽。当前TI公司已经推出相关的异构处理器与多核DSP;英伟达公司推出了最新的SoC芯片Tegra4,其内含4个Cortex.A15和72个GeForceGPU[3-4]。最新的SoC制程也已经达到28 nm,几乎取得了相当于PC的频率带宽。由于视频的数据量大,占用带宽多,这不仅对网络是个不小的负担,对图像本地存储备份的能力也有很大的影响,所以就需要采取一种高效的压缩算法对视频进行编码,以降低其所占用的网络带宽和存储空间[5]。近年来,H.264、MJPGE等算法的研究使得网络较实时传输和本地存储备份成为了可能。最新的H.265压缩算法的出现大大提高了视频传输效率,但这需要相应的处理器能力的提高[6]。

本文所设计的多路数据流视频监控终端设备基于TI公司的TMS320DM365芯片,支持双路不同分辨率大小的数据流,分别实现两种不同的功能,第一路数据流实现D1(720×576)分辨率大小H.264编码数据的本地存储备份,第二路数据流实现QVGA(320×240)分辨率大小原始数据的实时显示。

1 系统总体设计框架

本文采用视频采集芯片+多核芯片(ARM核+DSP核或编解码协处理器组成)的方案来设计视频监控终端设备,这种方案将视频采集芯片获得的数据接入到多核芯片中,再交由DSP核或编解码协处理器完成视频数据的编码,最终通过ARM核对系统进行控制,完成数据流的正确传递和其他必要操作。这种方案成本较低,性价比较高。

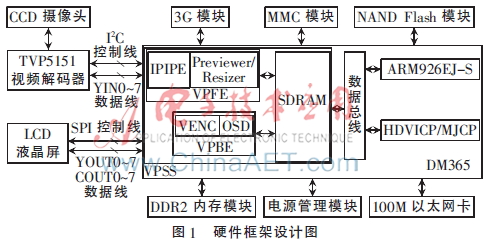

硬件框架方面,选用了TI公司的基于DaVinci技术的TMS320DM365芯片作为处理器芯片,以及同为TI公司出品的TVP5151芯片作为视频前端采集芯片来搭建嵌入式视频监控设备。

系统硬件框架设计图如图1所示。

软件框架方面,采用多线程配合工作的方案进行设计,多线程编程相较于多进程编程,它不仅在资源利用率方面有较大的优势,同时也大大降低了程序员编程的难度,加快了项目软件的开发。

2 视频处理子系统模块

TMS320DM365芯片上提供了一个视频处理子系统(VPSS),用于视频数据的实时采集、播放等功能。VPSS内部集成了一个视频处理前端模块(VPFE)和一个视频处理后端模块(VPBE),VPFE用来控制接入的外部图像采集设备,如图像传感器、视频解码器等,本系统接入了TVP5151视频解码器。VPBE则用来控制接入的显示设备,如标清的模拟电视显示器、数字的LCD液晶显示屏等,本系统接入了RGB565LCD液晶显示屏。此外,VPSS还集成了内存缓存区和DMA(直接内存访问)控制器,用来保证有效地利用DDR2或mDDR,控制突发带宽。

2.1 驱动配置

2.1.1 VPFE采集驱动的配置

VPFE采集驱动通过标准的V4L2接口将底层硬件的功能暴露给了上层应用程序,这样,应用程序就能通过控制V4L2设备(/dev/Video0)来获取由连接到VPFE的视频解码器(如TVP5151)采集到的一帧原始数据。VPFE硬件模块支持以下两种不同的数据管道[7],如图2所示。

(1)输入接口通过IPIPE接入到SDRAM,所有型号的SoC都支持这个通道。

(2)输入接口通过IPIPE接入到Previewer,并最终从Resizer输出两种不同分辨率大小的视频数据到SDRAM,从RSZ-A输出的是原始分辨率大小的图像,用于后续的数据编码,从RSZ-B输出的是分辨率较小的图像,用于后续的实时显示。

为了实现前文所述的视频实时显示功能,通过VPFE驱动将VPFE硬件模块配置成第二种数据流通道的采集方式。

2.1.2 VPBE显示驱动的配置

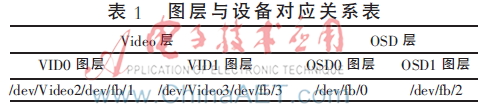

VPBE显示驱动由更底层的V4L2(Video for Linux 2)驱动和FB(Frame Buffer)驱动构成,当内核加载V4L2驱动时,它会向内核注册/dev/Video2和/dev/Video3两个设备,而当内核加载FB驱动时,它会向内核注册/dev/fb/0、/dev/fb/1、/dev/fb/2、/dev/fb/3 4个设备,注册的设备都对应了它们所能控制的图层[8],对应关系如表1所示。

可以通过设置系统启动参数来决定VPBE驱动被加载时会向内核注册的设备,以此决定开启的图层以及图层开启后受何种设备控制[9],例如,注册/dev/fb/3设备,VID1图层将被开启且只受/dev/fb/3设备控制。在实际方案中,启动参数指定VPBE向内核注册/dev/Video2设备和/dev/fb/0设备,分别开启了VID0图层和OSD0图层,其中VID0图层受/dev/Video2设备控制,用于显示采集到的视频数据,而OSD0图层受/dev/fb/0设备控制,用于显示QT等UI交互界面,其余图层默认保持关闭状态。

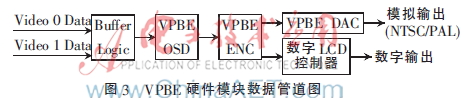

VID0图层的数据和VID1图层的数据会依次经过VPBE硬件模块中的OSD部件和ENC部件,最终由DAC模块输出模拟信号或者由LCD控制器输出数字信号[10],数据管道如图3所示。

在前文中已提到,LCD液晶屏被接入到了VPBE模块,所以VPBE驱动将VPBE硬件模块配置成视频数据由VID0图层输入,并最终通过LCD控制器输出到LCD液晶屏上。

2.2 应用程序设计

在VPFE驱动将VPFE硬件模块配置为双分辨率数据流的前提下,将应用层程序设计为一路数据流用于视频实时显示,另外一路数据流用于视频编码,Capture线程数据流程图如图4所示。

(1)第一路数据流

hCapture-->hCapBuf-->hDstBuf(D1:720x576)-->hOutFifo,用于视频编码存储。

(2)第二路数据流

hCapture-->hCapBuf-->hRzbBuf-->hDisBuf(QVGA:320x240)-->hDisplay,用于视频实时显示。

hCapBuf缓存用于存放VPFE采集驱动采集到的原始视频数据,存放着736×576大小的数据,hDstBuf缓存中的数据用于供后续视频编码存储,存放着D1:720×576大小的数据,hDisBuf缓存中的数据用于供后续视频显示回放,存放着QVGA:320×240大小的数据,hRzbBuf缓存中的数据用于供后续视频编码上传。

3 视频编码模块

原始视频数据的编解码需要用到达芬奇软件框架的Codec Engine(编解码引擎)技术来实现。Codec Engine定义了一组VISA(Video Image Speech Audio)APIs接口供应用程序调用。DM365的高清视频协处理器(HDVICP)封装了相应的编解码算法,ARM处理器中的应用程序可以通过VISA-APIs接口对编解码算法进行调用。ARM处理器负责执行应用程序,视频协处理器负责执行编解码算法,这样不仅大大降低了ARM处理器的CPU占用率,还能提高编解码的效率。本文采用H.264编码标准进行编码,需要调用相应的H.264算法实例。

3.1视频编码接口

H.264是一种高性能的视频编解码标准,继承了H.263和MPEG1/2/4视频编码器的优点。H.264标准中定义了两个层次:视频编码层(VCL)和网络抽象层(NAL),VCL负责高效的数字视频数据压缩,NAL提供适当的接口对数据进行打包和传送。

为了得到H.264格式的视频流,需要配置alg_server.cfg文件来实现对已经编译算法的调用,文件配置如下:

var H264ENC=xdc.useModule(′ti.sdo.codecs.h264enc.ce.H264ENC′);//指定调用的算法

var myEngine=Engine.create("alg_server",[{name:"h264enc",mod:H264ENC,local:true,groupId:1}]);

//创建引擎实例

在应用程序中能调用的接口函数有:VIDENC1_create、VIDENC1_control、VIDENC1_process和VIDENC1_delete,它们分别负责编码实例的创建、控制、运行以及最终的清除。

3.2 应用程序设计

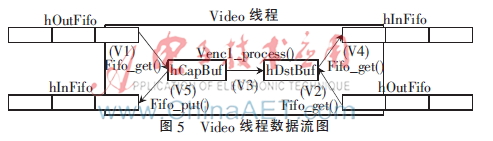

所设计的Video线程基于Capture线程,Capture线程向Video线程输入一路D1:720×576大小的数据流,Video线程如图5所示。

4 测试结果

测试环境搭建方法如下:

(1)LCD液晶屏连接在以TMS320DM365为主芯片的产品板上,TMS320DM365主芯片的CPU频率为216 MHz,板载Flash为1 GB,板载DDR2为128 MB。

(2)本地备份的视频数据文件存储在SD卡中,文件格式为H.264,文件大小为6.2 MB,总时长为1 min,使用VLC播放器播放。

经测试,视频监控终端设备能实时地显示摄像头采集到的视频画面,显示画面大小为QVGA(320×240),如图7(a)所示。SD卡里存储备份的视频数据也成功纪录了一段时间内的视频画面,分辨率大小为D1(720× 576),如图7(b)所示。

5 结论

本文设计实现了基于TMS320DM365硬件平台的视频监控终端设备,该视频监控终端设备不仅具有数据采集功能,而且还集成了本地存储备份以及原始数据实时显示等核心功能。采用TMS320DM365的ARM+DSP双核模式,提高了编码效率以及传输效率,通过测试发现,实时图像清晰流畅,ARM资源占有率低,可扩展性大,满足系统实时性和稳定性的要求。

参考文献

[1] 张伟.视频监控技术的发展历程和方向[J].中国交通信息产业,2007(6):139-142.

[2] 郑磊.基于嵌入式Linux的网络视频监控系统研究[D].武汉:武汉理工大学,2011.

[3] 刘继超.基于DM355的嵌入式网络视频监控系统设计[D].青岛:青岛科技大学,2012.

[4] 望重.嵌入式网络视频监控系统的研究与实现[D].镇江:江苏大学,2010.

[5] 胡攀.基于Linux的网络视频监控系统设计[D].武汉:武汉理工大学,2012.

[6] 项昌晨,王磊.基于TMS320DM365的网络视频监控系统设计[J].机电一体化,2011,17(12):58-63.

[7] Texas Instruments. Davinci Linux VPFE Capture Driver[EB/OL].[2014-12-15].http://www.ti.com/lit/an/sprs566a/sprs566a.pdf.

[8] Texas Instruments, Video Processing Back End(VPBE)[EB/OL].[2014-12-15].http://www.ti.com.cn/cn/lit/ug/sprufg9c/sprufg9c.pdf.

[9] Texas Instruments, LSP 2.10 DaVinci Linux VPBE Frame Buffer Driver[EB/OL]. [2014-12-15]. http://www.ti.com/lit/ug/spruek9/spruek9.pdf.

[10] Texas Instruments, LSP 2.10 DaVinci Linux V4L2 Display Driver[EB/OL]. [2014-12-15]. http://www.ti.com/lit/ug/spruel3/spruel3.pdf.