陈啸,李广侠,李志强,朱文明

(解放军理工大学 通信工程学院,江苏 南京210007)

摘要:提出了一种基于FPGA的低截获概率卫星测控信号捕获解决方案。基于AD+FPGA的硬件架构完成了带宽为200 MHz的跳频和直接序列扩频混合扩频信号的解跳、解扩,实现了基于Xilinx的快速傅里叶变换IP核的扩频码的快速滑动码相关,以及多跳积分结果的相干累加,并采用相对门限法进行了捕获判决。板上试验结果证明了该方案的捕获性能,最大捕获时间小于4 s,捕获概率达到99%,虚警概率小于0.001。该系统已应用于北斗二代导航MEO卫星测控链路。

关键词:FPGA;低截获概率信号;卫星测控;信号捕获

0引言

当前我国卫星测控网主要采用微波直接序列扩频测控体制,具有抗干扰性强、测距精度较高、一站对多星测控等优点[1]。一种新的低截获率混合扩频测控信号综合了跳频扩频(FHSS)和直接序列扩频(DSSS)的优点,测控信号抗截获、抗干扰能力得到有效提升,测控精度也随信号带宽增加而提高[2]。

低截获概率信号的合作性接收机设计中,信号捕获设计最关键,是信号跟踪的前提,运算量通常占同步运算的80%以上。其结合了DSSS和FHSS的低截获率扩频信号,由于信号频谱比直扩信号进一步展宽,因此其自相关函数峰更加尖锐,导致捕获时的时延搜索精度要求更高,另一方面,由于采用跳频体制,多普勒捕获问题中又加入了跳频频率跳变,需要设计高效的捕获算法[3]。

FPGA具有设计开发周期短、可在线更新、处理性能优异等特点,适用于解决测控通信中的捕获问题[46]。针对低截获率混合扩频信号的捕获问题,本文设计了一种基于FPGA芯片的跳频直扩混合扩频信号捕获系统,该系统在完成跳频解跳、直接序列扩频序列剥离的同时,实现快速的跳频多普勒搜索和时延搜索。对A/D采样信号进行FPGA芯片内数字正交下变频解跳,使用Xilinx的IP核进行基于FFTIFFT的并行直扩码解扩,用分段积分和相位补偿的方法实现了大多普勒范围搜索,实现了较大时间范围内的信号滑动相关,采用相对门限法进行信号捕获的判决,获得了优异的检测性能。该捕获系统芯片资源占用率合理,功耗较低,采用多重高可靠性设计,适用于卫星等空间飞行器的测控系统。

1捕获模型

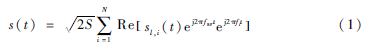

本文研究的低截获率扩频测控信号是相位连续的快跳频加直接序列扩频信号,也称为DS/FH混合扩频信号,采用二进制相位调制方式(BPSK)。跳频方式为块跳频(block hopping),即直扩码相位周期、跳频相位周期均等于一个调制符号的时间长度,跳频图案和伪码相位同周期变化,周期均为N跳,信号自相关峰的周期也为N跳,每个跳频时段内包含一个整周期的直接序列扩频码。由于卫星测控通信属于高可靠性的低速率通信,一个跳扩频周期内的调制信息是恒定的,那么信号可表示为:

其中,S为发送信号的平均功率,fi表示跳频频点, fRF 表示跳频频点的射频基准频率,那么实际的射频跳频频率为fi+fRF。Th为一个跳频频率的持续时间,N个Th组成一个跳频周期。Re[·]为取实部运算。sl,i(t) 表示第i个跳频频率内的扩频码,并且定义:

sl,i(t)=PN(t)(2)

其中,PN(t)表示伪码速率为fc的直接序列扩频码。为了确保各个跳频时段Th内的射频载波相位起始值相同,跳频频率设计为:

fi=k/Th, k∈{1,2,...,K},i=1,2,3,...,N(3)

其中,k表示跳频图案,fi为1/Th的k次谐波,射频跳频带宽为 BH=K/Th,K为跳频频率池的大小,N为所选用的跳频点的个数,NK。扩频码采用周期长度为M的伪随机码。为了满足块跳频要求,M满足

MTC=NTh

TC为一个码片时间长度。这种扩频信号的处理增益高,能够对抗单音干扰、宽带干扰等多种样式的单一和组合干扰。跳频图案采用Costas跳频序列,周期为200跳,PN码采用周期为1 023的Gold码,信号参数如表1所示。

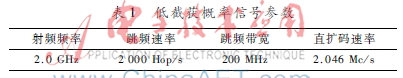

DS/FH混合信号作为一种扩频信号,信号频带宽,且能量均匀分布在整个频带内,导致信号被噪声所淹没,具有很强的抗截获能力,要实现对此混合信号的捕获,必须对接收信号进行滑动相关运算。如图1所示,接收机中频图1相干累加原理接收到跳扩信号后,经过滑动解扩和解跳,将信号的跳变频率和直扩伪码从信号中剥离[8]。当滑动相关时接收信号和本地信号相位重合,即信号恢复成窄带信号后,再对信号进行累加,滤除带外噪声,得到高信噪比的检测量或检测信号;最后将其送入检测器,完成捕获判决。

对于式(1)中的相干跳扩频信号,在背景噪声为白噪声、信道中无干扰的条件下,本地跳频扩频信号以半个码片(或者更细小)的搜索间隔进行滑动,完成载波/伪码剥离后经长度为多跳的相干积分后检测量的获得。无信号时检测量服从自由度为1的中心χ2分布,有信号时检测量服从自由度为1的非中心χ2分布。

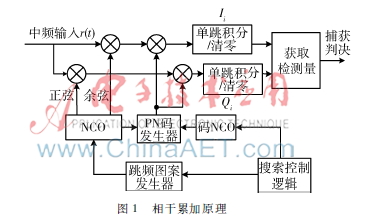

假设有信号条件下,单跳积分检测量服从A/σ2=10,σ2=1的高斯分布,并取N=10,那么根据参考文献[7],3种检测量的包络在信号有/无条件下的概率密度函数如图 2所示。信号捕获判决准则采用NeymanPearson准则,即在给定信号虚警概率PF前提下,设定判断区域V,使信号检测概率PD最大。从图2中可看出,选多跳相干累加检测量作为捕获判决量,在相同的虚警概率条件下能获得较高的检测概率。

2系统设计方案

2.1硬件环境

根据捕获运算要求,本系统用基于FPGA的硬件设计方案实现高速并行捕获逻辑运算。FPGA处理的硬件环境如图3所示。

待捕获的跳扩频信号通过两路ADC,将模拟信号转换为数字信号,进入FPGA,供FPGA进行处理。程序存储PROM中是本设计产生的FPGA配置文件,加电后,FPGA读取配置文件,在时钟驱动下,实现开发人员设计的逻辑功能。

2.2分模块设计

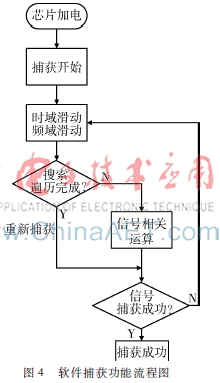

为实现FPGA内部软件的跳扩频信号捕获功能,本系统设计的处理流程如图4所示。

软件设计分为4个功能模块,其名称和功能如下:

(1)捕获控制模块:AcqCtrl

负责捕获处理流程控制和捕获结果的判断。

(2)正交解跳模块:AcqFront

在捕获控制模块控制下,完成跳扩频信号的解跳。

(3)并行解扩模块:CorrFFT

用FFTIFFT并行相关算法完成直接序列扩频信号的解扩,负责时间长度为1个跳频时段的信号积分。此模块负责完成分辨率为半个直接序列扩频码码片的时延搜索。

(4)多跳累积模块:PhasCmp

负责将N个跳频时段内的积分结果累加起来,得到半码片以内的时域搜索的捕获结果,同时实现(-50 kHz,50 kHz)范围的多普勒搜索,将累加结果送给捕获控制模块进行判断。综合以上4个模块,形成了本软件的模块架构,如图5所示。虚线表示控制信号,实线表示信号流。

2.2.1正交解跳模块

为节省硬件资源,本文算法对应的捕获结构采用了双下变频器交替变频解跳和基于FFT的快速码相关解扩的方案。图6表示解跳结构,跳频带宽为200 MHz,采样频率为280 MHz正交I、Q采样,用不同图案表示不同跳频频图6AcqFront模块工作示意率,τ表示收发时间差,PN1表示接收第1跳内的PN码,本地下变频器相位从0开始,到4 kπ结束,跳频频率重合时,解扩A、B输出正确的PN码。2个下变频器A、B交替解跳的结构加长了单个跳频谐波解跳的时长,获得了2Th时长的解跳结果,交替解跳结构能够保留2Th时长的解扩输出,从而保证码相关积分时长为Th时,码滑动相关的搜索范围能够达到τmax=Th。

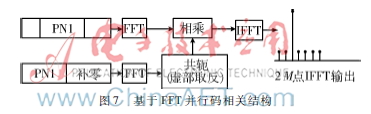

2.2.2基于FFT的并行解扩模块

解跳完成后,在芯片内对信号进行下抽处理,降低后端信号处理速率需求。将280 MHz采样信号下抽40倍到7 MHz后进行处理。图 7表示解扩结构,解跳结果以流水线顺序送入FFT核,每一帧点数为4 096点,同时本地扩频码也进行FFT。经处理后,每一跳时间内对应输出M=2 046个解扩结果,存入RAM中。

2.2.3多跳累积模块

将解扩模块输出的N跳内M个码相位上的共M×N个解扩结果从RAM中读出之后,按0.1码片的步进进行时间搜索和相干累积。图8所示为相干累积结构。

将2NM个数据点Pi(m)按跳频点i分为2M组,逐组对i=1,2,…,N个数据进行相干累加,相干累加结果取平方后经过一个比较器,保留最大相干累积能量及其对应的时间频率搜索值。当得到最大相干累积能量Pmax及其对应的时间频率信息后,再取该时间点附近的L个点计算出L个积分结果,表示码相位范围为(-L/2,L/2)个码片。若Pmax>2·E[P(l)],则判断捕获成功,反之则判定为捕获失败。

2.3实现情况

为实现低截获概率信号捕获系统,选用了Xilinx公司的Kintex7FFG900芯片,A/D芯片采用2片14位输入的AD9726芯片。FPGA外部参考时钟为100 MHz,内部工作时钟为280 MHz。芯片内部Slice使用率为56%,满足航天设备芯片降额使用的标准,芯片功耗估计值为4.3 W,包括A/D转换等器件的基带电路总功耗为7 W。实现了第2节中低截获概率跳扩频信号的捕获,时间捕获范围为(-50 ms,50 ms),多普勒频率捕获范围为(-50 kHz, 50 kHz),多普勒变化率范围为(-12 kHz/s, 12 kHz/s)。最大捕获时间不超过4 s,捕获概率大于99%,虚警概率小于0.001。

3试验结果

对本文的捕获系统进行了基带电路板仿真验证,统计了不同的时间搜索精度下,信号源发射信噪比与检测概率的关系如图9所示。试验环境包括安捷伦E4438C信号源2台、XX型卫星应答机射频通道、基于Xilinx Kintex7的基带板一副,以及电源、连接线若干。信号源负责信号上变频和射频加噪,基带板完成发送和捕获中频跳扩测控信号的功能。

电路板验证时可通过FPGA预留调试口调整时间搜索精度,可选精度有0.01/0.1/0.25/0.5 chip。由于码相位搜索间隔以及FFT运算的有限字长效应[9],导致板上仿真检测性能略有下降,距离理论值约有3 dB距离;当选取Δτ=0.1 chip,本文算法在单符号信噪比为17 dB时可达到99%的捕获概率;当码相位搜索间隔从0.25 chip扩大到0.5 chip时,检测性能急剧下降。

4结论

为解决低截获概率混合扩频的快速捕获问题,选择了以FPGA作为处理核心的基带解决方案[10],设计实现了基于FFT分段码相关和多跳相干累积的捕获系统并进行了板上试验。本算法捕获精度达到0.01 chip,捕获到的DS/FH信号可直接送入载波环路进行载波跟踪,能减轻跟踪环路负担。实际应用中,可根据捕获精度需求选择时间捕获分辨率,大小从0.01 chip到0.5 chip。经在轨测试后,本系统已成功运用于北斗二代导航卫星的某新型卫星测控系统中。

参考文献

[1] 沈荣骏,赵军.我国航天测控技术的发展趋势与策略[J].宇航学报,2001,22(3):15

[2] 杨文革,王金宝,孟生云,等.DS/FH混合扩频信号捕获方法综述[J].测控技术,2009,28(z1):1620.

[3] KAPLAN E D, HEGARTY C J, Understanding GPS, principles and applications(Second Edition)[M]. Norwood, MA: Artech House, Inc. ch. 5.4,173200.

[4] 王水鱼,冯晓靖.一种新型deltasigma小数分频器的FPGA实现[J].微型机与应用,2013,32(5):2527,31.

[5] 彭奇,习友宝.基于FPGA和改进CORDIC算法的NCO设计与实现[J].微型机与应用,2013,32(5):6062.

[6] 宋万均,张安堂.双基地雷达目标速度计算的FPGA实现[J].电子技术应用,2014,40(1):4749,52.

[7] MARCUM F I. A statistical theory of target detection by pulsed radar, rand research memo[R]. RM754, December 1947, with Appendix, RM753, July 1948.

[8] 潘点飞,程乃平,郝建华,等.DS/FH测控系统抗干扰性能分析与测试[J].空间科学学报, 2013, 33(5): 540547.

[9] 黄磊,张其善,寇艳红,等.GPS信号FFT捕获算法的有限字长效应分析[J]. 宇航学报, 2006, 27(5): 10291033.

[10] 陈巍,王国富,张法全,等.基于FPGA同步时钟测量系统的研究及实现[J].电子技术应用,2014,40(12):8688,91.