杨莹1,张琴1,杨灿美2,林福江1

(1.中国科学技术大学 信息科学技术学院,安徽 合肥 230027;2.中国科学技术大学 先进技术研究院,安徽 合肥 230027)

摘要:深入研究以太网组帧、传输的方式以及流量控制的原理,结合万兆以太网介质访问控制(XGMAC)64 bit数据并行处理的特点,针对PAUSE帧响应周期长、占用硬件资源多的问题,设计了一种精简的基于PAUSE帧的流量控制电路,在ISE中逻辑综合与仿真。验证结果表明,该电路可满足万兆以太网流量控制的要求。

关键词:万兆以太网;流量控制;XGMAC;PAUSE帧

0引言

自2002年万兆以太网标准IEEE802.3ae[1]提出以来,万兆以太网技术得到迅速发展与广泛应用,近年来逐步取代千兆以太网成为新一代的城域骨干网络。相对于千兆以太网MAC层的125 MHz时钟频率与8 bit数据处理位宽,万兆以太网介质访问控制(10 Gigabit Ethernet Media Access Controller, XGMAC)层采用156.25 MHz时钟频率与64 bit数据处理位宽。时钟频率的提高、数据位宽的增大给MAC层流控制电路的设计带来新的挑战[2]。本文针对XGMAC层的特点提出一种高效、低功耗的流控制电路设计方案,旨在减少流控制机制对系统造成的额外延时并以此提高发送和接收以太网帧的效率。

1基于PAUSE帧流控制的原理

为了提高传输效率,XGMAC层采用PAUSE帧进行流量控制。PAUSE帧为符合IEEE802.3协议的一种控制帧,遵从以太网最小帧长度64 B的限制[3]。

流量控制原理如图1所示,当local_XGMAC 接收模块中接收缓存快满(快空)时,local发送模块根据图1XGMAC流量控制示意图

流量控制模块指示的信号发送时间参数为0xFFFF(0x0000)的PAUSE帧。remote_XGMAC接收模块接收到PAUSE帧并确认有效后,提取时间参数用于流量控制模块的暂停发送计数器赋值,并以此控制发送模块暂停(恢复)发送数据帧。

2流量控制电路的结构

如图2所示,XGMAC流量控制模块分为发送和接收两个部分。

2.1PAUSE帧发送电路设计

千兆以太网中,因其8 bit的数据处理位宽限制,PAUSE帧通常使用逻辑状态机,按照帧格式通过状态转换填充至发送缓存,逻辑略显繁琐。

本文经过对比分析后发现,对于暂停发送与恢复发送这两种功能的帧,数据中有且只有时间参数与CRC校验码不同,考虑到XGMAC内部数据为64 bit并行处理,设计时可将帧中固定部分(即目的地址到操作码)与控制字节直接固化于72 bit位宽的PAUSE ROM空间内,时间参数根据帧的功能对应赋值即可。发送电路的结构如图2上半部分所示。实际工作中,由发送PAUSE控制器根据接收缓存逻辑判断结果选择PAUSE ROM或发送缓存FIFO作为数据源,按照XGMAC数据格式送至预存数据FIFO即可。

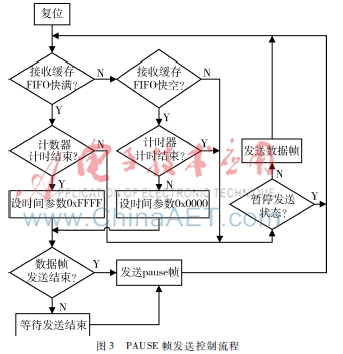

本文设计的PAUSE发送控制器流程如图3所示。

计数器于发送PAUSE帧后启动,用于保证两次PAUSE帧发送的间隔时间;local XGMAC处于暂停接收状态时,检测到接收缓存快空时,即进入发送PAUSE帧状态,设置时间参数0x0000,通知remote XGMAC可以继续发送数据。PAUSE帧所需的CRC32校验、填充及组帧可共用XGMAC本身的数据处理模块。

使用Verilog HDL[4]语言对PAUSE发送控制器进行描述,部分关键代码如下:

always@(posedge clk_tx or negedge reset_tx_n) begin

if(!reset_tx_n) pauserom_sel <= 1′b0;

else if(local_busy&pause_tmzero&(tx_empty|tx_eop)) pauserom_sel <= 1′b1;

else if(pause_eop) pauserom_sel <= 1′b0;

end

assign txl_rdat= pauserom_sel? pauserom _rdat : tx_rdat;

assign txl_eop = pauserom_sel? pauserom_eop : tx_eop;

assign txl_sop = pauserom_sel? pauserom_sop : tx_sop;

assign txl_empty = pauserom_sel? pause_rempty : (tx_empty | pause_state);

assign pauserom_ren = pauserom _sel? txl_ren : 1′b0;

assign tx_ren =pauserom _sel? 1′b0 : txlfifo_ren;

其中,local_busy表示接收缓存FIFO快满;pause_tmzero表示计数器计时结束;pause_state表示当前处于暂停发送状态。

2.2PAUSE帧接收电路设计

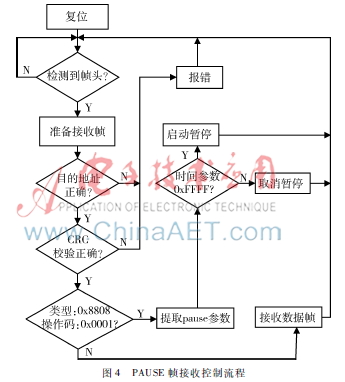

本文设计的接收电路结构如图2下半部分所示,接收PAUSE帧控制器是本设计的重点。与千兆以太网的8 bit数据处理位宽不同,64 bit并行识别PAUSE帧与定位参数的方式可大幅提高处理速度。XGMAC采用Deficit Idle Count(DIC)算法保证数据32 bit对齐;在本设计中利用移位寄存器,实现了数据帧的64 bit对齐,方便XGMAC的后续处理。实际工作中,3个时钟周期可完成PAUSE识别。

PAUSE接收控制流程如图4所示。检测到帧头后进行判断:若为PAUSE帧,设置暂停发送或者恢复发送的状态;若是数据帧,则根据当前接收FIFO状态保存数据,递交上层协议。部分关键代码为:

if (curr_cnt == 11′d0 && rx_aligndat[47:0] == ′PAUSE_FRAME) begin

next_pause_addr = 1′b1;

end

if (curr_cnt == 11′d8) begin

next_pause_addr = 1′b0;

if( pause_addr && rx_aligndat [47:32] == ′PAUSE_TYPE &&

rx_aligndat [63:48] == ′PAUSE_OPERATE) begin

next_pause_opera = 1′b1;

end

end

if (curr_cnt == 11′d16 && pause_opera == 1′b1) begin

next_pause_opera = 1′b0;

next_pause_time = rx_aligndat [15:0];

next_pause_frame = 1′b1;

end

其中,第一个时钟沿完成组播目的地址的检测;第二个时钟沿结合地址检测结果并行检测帧的类型与操作码;第三个时钟根据前两个检测结果获取时间参数并用于发送计数器。

3仿真及验证

电路选用Virtex5系列 XC5VSX50T型FPGA芯片,按以下流程使用ISIM进行仿真验证:(1)模拟以太网数据帧发送过程中插入PAUSE帧;(2)模拟以太网数据帧接收过程中检测PAUSE帧;(3)将发送部分与接收部分相连进行环回测试,检测PAUSE帧发送与接收整个过程。环回测试截取仿真时间140 ns~550 ns的波形如图5所示。图5回环测试结果A处表示正常状态下发送PAUSE控制器选择读取发送缓存 FIFO;B处监测到接收缓存FIFO快满,进入监测数据帧发送状态阶段;C处表示当前数据帧读取完毕;结合B处状态,D处发送PAUSE控制器切换读取PAUSE ROM并发送,若持续检测到接收缓存FIFO快满,则于计数器计数完成后再次进入D状态,计数过程中正常发送数据帧;E处pause_frame_ok信号指示PAUSE帧环回后被正常接收识别。

在ISE中对关键路径进行约束,综合后得到最高运行频率达181.23 MHz,频率设计余量约16%,满足XGMAC设计要求。

4结论

针对万兆以太网MAC层64 bit并行数据的特殊性,本文通过在发送缓存链路中插入控制电路,利用小容量ROM配合简易逻辑的方式,实现了发送端的流量控制。相对于纯状态逻辑的实现途径,此方式更容易凸显电路的简洁,从而提升电路的高速性能;接收链路中,将接收数据64 bit对齐后,并行检测特征参数以识别PAUSE帧,并提取时间参数反馈至发送端,有效地提升了处理速度。经过仿真,验证了该方案可行。本文的思路对其他高速通信的流量控制电路设计具有一定借鉴意义。

参考文献

[1] IEEE Std 802.3ae2002, Media Access Control (MAC) Parameters, Physical Layers, and Management Parameters for 10 Gb/s Operation[S].2002 .

[2] 张友亮, 刘志军, 马成海,等. 万兆以太网MAC层控制器的FPGA设计与实现[J/OL]. 计算机工程与应用,(20110224).http://www.cnki.net/kcms/detail/11.2127.TP.20110224.1050.005.html.

[3] 张立明,章建雄,王玉艳. 千兆以太网 MAC 的流量控制策略[J]. 计算机工程,2011,37(15):256258.

[4] 夏宇闻.Verilog数字系统设计(第二版)[M].北京:北京航空航天大学出版社,2008.