文献标识码: A

DOI:10.16157/j.issn.0258-7998.2016.08.004

中文引用格式: 蔡琰,季昊,施建安. 采用Mult-tap标准单元PGV以获取精准的Power EM违例[J].电子技术应用,2016,42(8):25-27.

英文引用格式: Cai Yan,Ji Hao,Shi Jian′an. Application of multi-tap standard cell PGV to capture accurate power EM violations[J].Application of Electronic Technique,2016,42(8):25-27.

0 引言

电源电子迁移(Power Electromigration,Power EM)检查在高速芯片设计中起着重要的作用。Voltus在进行电源网格分析时会对电源电子迁移进行检查。在先进工艺制程下,由于较高的时钟频率,M1电源网格上会出现一些Power EM违例。这些违例是假的,并且无法用像增强电源网格,把其他标准单元从违例区域移走之类的常规方法修掉。这些假的违例出现的根本原因是单个电流接入点(tap)过于简单,无法正确引导电流分布。因而,在下文中,我们会描述针对大型时钟单元抽取多电流接入点(multi-tap)PGV以获得更精确Power EM违例的方法。

1 常规标准单元PGV生成方法

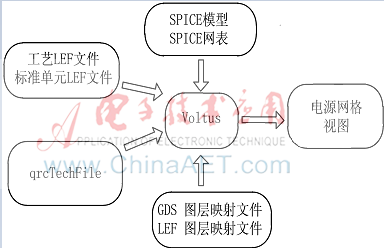

标准单元PGV生成流程如图1所示,Voltus会读取以下文件以产生标准单元PGV[1]。

图1 标准单元PGV生成流程

(1)工艺LEF文件

(2)标准单元LEF文件

(3)QRC提取工艺文件(qrcTechFile)

(4)GDS图层映射文件

(5)LEF图层映射文件

(6)SPICE模型

(7)SPICE网表

此外生成标准单元PGV,还需要脚本命令辅助。以下是一个范例。

read_lib -lef $tech_lef $std_lef_list

set_pg_library_mode \

-ground_pins { GND } \

-power_pins { VDD 1.0 } \

-decap_cells { $decap_cell_parttern } \

-filler_cells { $fill_cell_pattern } \

-celltype stdcells \

-spice_subckts $std_spice_netlist \

-spice_models $spice_models_file \

-spice_corners {$spice_corners} \

-temperature 0 \

-lef_layermap $lef_layermap_file \

-extraction_tech_file $ex_tech_file

generate_pg_library \

-output ./pgv/stdcell_pgv

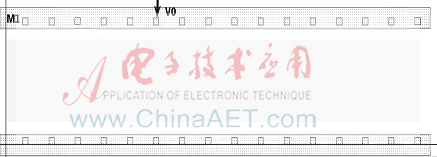

通常PGV会有EARLY,IR和EM三种视图。对于标准单元来说, 这三种视图是完全一致的,仅在电源端口包含电流分布参数和SPICE仿出来的电容信息。Tap通常产生在电源端口的中心位置。如图2中的BIGBUFFERD1 PGV所示,VDD和GND各自只有一个tap。因此,在Voltus网格分析中,流入每个标准单元的电流都聚集在一点。这也是为什么假的Power EM违例发生在tap位置的原因。

图2 BIGBqUFFERD1 PGV图形

2 Multi-tap标准单元生成方法

在现实世界中,电流是通过多个V0流入标准单元的。如图3所示,大型标准单元的VDD和GND 端口各自有很多V0。所以每个端口只抽取一个tap并不符合实际情况,无法真实反应电流分布。

图3 BIGBUFFETRD1 GDS图形

所以若产生multi-tap 标准单元PGV, 电流是可以均匀分布到所有tap上,结果会更加准确。基于这个方案,我们还需要解决以下三个问题。

(1)哪些标准单需要产生multi-ap PGV?

(2)怎么产生multi-tap 标准单元 PGV ?

(3)如何在电源网格分析中应用multi-tap 标准单元PGV?

2.1 哪些标准单元需要产生multi-tap PGV?

考虑到运行时间,内存消耗等因素,对所有的标准单元进行multi-tap PGV 抽取是不明智的。而且在我们的设计中,除了关键路径上的时钟单元,绝大多数标准单元的翻转率很低。所以对大多数标准单元来说,它们的电流不会太高,一个tap已经能够反映电流分布。然而,对关键路径上的时钟单元来说,它们分布的地方有很大几率出现M1电源网格的Power EM违例。因此,我们仅需对大型时钟单元抽取multi-tap PGV。

2.2 怎么产生multi-tap 标准单元PGV?

基于标准的PGV生成的流程,我们还可以加一些特殊指令去调节节点之间的距离以控制tap的数量(Voltus默认节点距离是50)。以下是节点距离为0.15脚本示例。

set_advanced_pg_library_mode \

-libgen_command_file libgen.cmd

libgen.cmd:

setvar max_itfnode_dist 0.15

如图4所示, VDD和GND端口各抽取了16个tap。

图4 Multi-tap BIGBUFFERD1图形

2.3 如何应用multi-tap标准单元PGV

当multi-tap PGV应用于电源网格分析中时,我们必须把这些特殊的PGV放到其他常规PGV的前面。对于有多个PGV的标准单元,Voltus仅会采用第一个非工艺的 PGV。此外,为了能在电源网格分析中保留所有的tap,我们必须关掉“-optimize_stdcells_library” 这个选项。以下有个例子。其中BIGBUFFERD1.cl是multi-tap PGV。

set_rail_analysis_mode \

-method static \

-accuracy hd \

-power_grid_library { \

techonly.cl \

BIGBUFFERD1.cl \

Stdcell.cl \

Ram.cl \

Analog.cl \

…}

-optimize_stdcells_library false \

…

3 结果分析

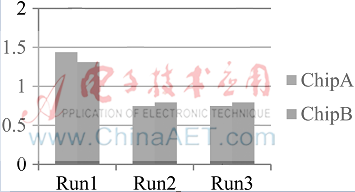

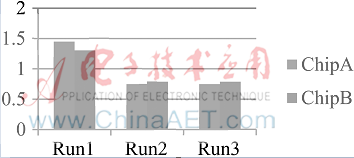

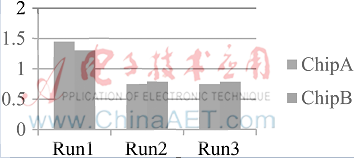

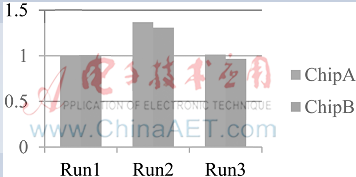

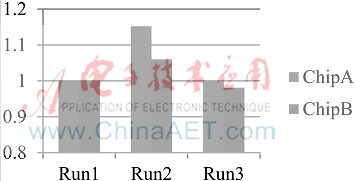

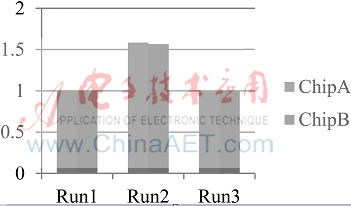

在Power EM分析中,我们的目标是当前流过的电流与可承受的最大电流的比率小于1。在图5~图11中,Run1是标准流程,Run2是对所有标准单元做multi-tap PGV抽取,而Run3只对大的时钟单元做这样的特殊处理;ChipA和ChipB是两块不同的芯片。

图5 VDD EM违例数量对比图

图6 GND EM违例数量对比图

图7 VDD最差电流比率对比图

图8 GND最差电流比率对比图

图9 归一化运行时间对比图

图10 归一化内存消耗对比图

从图5和图6中可以看出,对于ChipA,Run1中产生19个 VDD违例和19个GND违例,Run2和Run3没有违例。同样,对于ChipB,Run1中产生14个 VDD违例和14个GND违例,Run2和Run3没有违例。因此,采用multi-tap 标准单元PGV能有效减少违例数量。

图7和图8是最差电流比率的对比图。对于ChipA和ChipB,与Run1相比,Run2和Run3的最差电流比率下降了37%~40%。因此,采用multi-tap 标准单元PGV能有效降低最差电流比率,从而减少违例数量。

图9是归一化运行时间的对比图。和Run1相比,Run2运行时间增长了30%~37%,而Run3增长了-0.4%~0.1%。因此,对所有标准单元进行multi-tap PGV抽取会大量增加运行时间,而仅对大型时钟单元进行multi-tap PGV抽取基本不影响运行时间。

图10是归一化内存消耗的对比图。和Run1相比,Run2内存消耗增长了5%~15%,而Run3增长了-0.2%~0.1%。因此,对所有标准单元进行multi-tap PGV抽取会大量增加部分内存消耗,而仅对大型时钟单元进行multi-tap PGV抽取基本不影响内存消耗。

图11是归一化硬盘消耗的对比图。和Run1相比,Run2硬盘消耗增长了56%~59%,而Run3增长了-0.1%~0.1%。因此,对所有标准单元进行multi-tap PGV抽取会大量增加硬盘消耗,而仅对大型时钟单元进行multi-tap PGV抽取基本不影响硬盘消耗。

图11 归一化硬盘消耗对比图

综上所述,仅对大型时钟单元做multi-tap PGV抽取可以在几乎不增加运行成本的前提下去除假的Power EM 违例。

4 结论

通过只对大型时钟单元做multi-tap PGV抽取可以得到精确的Power EM违例结果,并且运行时间和内存消耗增加不到2%。在高性能的芯片设计中,这是一种分析Power EM违例的有效方法。

参考文献

[1] Voltus IC Power Integrity solution User Guide Version14.21,November 2014.