卢建章1,刘洋2

(1.中航工业雷华电子技术研究所,江苏 无锡 214063;2. 江南计算技术研究所,江苏 无锡 214083)

摘要:嵌入式应用中采用多处理系统所面临的主要难题是多处理器之间的数据通信。通过对KeyStone架构TMS320C6678处理器的HyperLink通信机制进行研究,利用其高速、低延迟、引脚少的特性实现处理器间的高速数据交换。从实际应用的角度,设计了HyperLink的映射结构,并分析了性能,对多处理器间通信具有一定的参考价值。

关键词:TMS320C6678;HyperLink;处理器间通信

中图分类号:TN915.04文献标识码:ADOI: 10.19358/j.issn.1674-7720.2017.03.011

引用格式:卢建章,刘洋.TMS320C6678多核DSP的HyperLink应用[J].微型机与应用,2017,36(3):36-38,41.

0引言

嵌入式领域的处理器设计已经向多核与多处理器迅速发展,最典型的是TI公司的KeyStone架构的多核处理器。TI公司2010年11月发布的KeyStone架构的8核DSP处理器TMS320C6678,其每个C66x内核主频最高达1.25 GHz,可以提供每秒高达40 GB MAC定点运算和20 GB FLOP浮点运算能力;1片8核的TMS320C6678提供等效160 GB FLOP的浮点运算能力,是TS201S的50倍多[1],适用于诸如油气勘探、雷达信号处理等对定浮点运算能力以及实时性有较高要求的超高性能计算应用。

处理器之间的数据交换是多处理器系统所面临的主要难点,通信机制的优劣直接影响系统的处理性能,高效的通信机制是发挥多处理器系统高性能的重要保障。TMS320C6678采用TI全新KeyStone多核架构,属于单芯片多核结构。由于板载多芯片之间的通信相对复杂,因此不同的设计选取会直接影响通信的效率。TMS320C6678采用基于KeyStone结构的专有外设接口HyperLink,采用的编码方式等效于8b9b,相对用于高速SerDes接口的传统的8b10b编码方式,其减少了编码冗余,提高了数据传输效率。单片提供4个设计速度为12.5 Gb/s的SerDes通道,所以HyperLink的理论吞吐率能达到44.4 Gb/s。

基于以上分析,本文针对TMS320C6678多核处理器,首先介绍了HyperLink的原理与机制,然后分析芯片之间HyperLink通信的映射原理,给出了通信连接的实现方法,并通过对多种映射关系进行对比,得出优缺点和使用范围,为嵌入式多处理器系统的设计提供参考。

1HyperLink机制

HyperLnik能为两个KeyStone架构DSP之间提供一种高速、低延迟、引脚数少的通信连接,是TI专有的外设接口。它使用了类似PCIE的内存映射机制,但能为多核DSP提供一些更为灵活的特性,下面从应用的角度分析HyperLink的构成和配置。

1.1模块架构

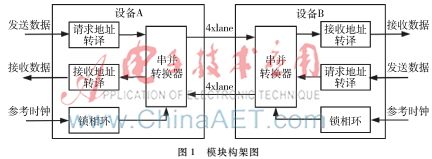

HyperLink是TI公司为实现嵌入式系统中芯片间高效数据交互而开发的一种点对点的全双工的连接模式,并能提供读、写和中断3种传输方式。HyperLink模块架构如图1所示。其中的PPL负责模块的时钟控制,通过合理的倍频系数配置生成需要的内部时钟,从而驱动链路上数据的传输[2]。

1.2映射机制

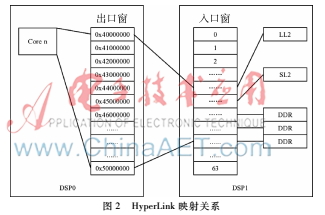

TMS320C6678每个核的0x400000000x50000000地址空间为HyperLink专属,相应核只有在配置了HyperLink图1模块构架图后才能对该地址空间进行读写,并通过相应的配置实现与远端存储空间的映射,包括DDR、SL2和LL2,具有非常灵活的映射关系。如图2所示。

对于任何一个TMS320C6678,入口映射窗一共64个,每个都可以对应不同的远端地址和长度,比如DSP1的LL2、SL2和DDR。本地出口窗由16个16 MB的地址空间组成,可以映射到远端入口窗所指向的地址空间。通过图2的映射配置,DSP0可以访问DSP1的所有内存空间,就像访问自己的本地存储空间一样。为了实现地址映射,必须按照以下方式进行设置[3]:

(1) 根据实际的地址映射关系和地址有效位配置发送端地址掩码寄存器(TXIGMASK)、PrivID和安全位域寄存器,接收端配置地址段选择寄存器(RX_SEG_VAL)和PrivID表;

(2) 配置串行/解串模块(SerDes)的参考时钟、数据传输回路方式和链路速率等信息;

(3) 写锁相环寄存器(CFGPLL),启动HyperLink的训练序列,并等待物理层返回准备状态。

按照上述配置后,DSP0读写本地出口窗地址时,HyperLink通过地址转译,即相当于直接访问映射的远端地址。

1.3地址转译

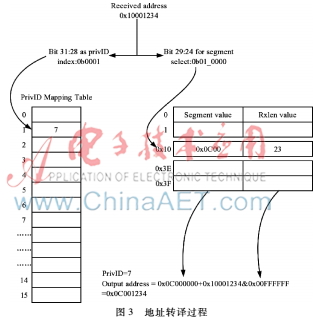

处理器核1在通过本地专属的地址0x40001234 进行读写操作时,HyperLink按照地址掩码寄存器的配置要求,结合专属地址和PrivID(core 1)生成发送端的HyperLink请求地址。例如发送端配置地址掩码寄存器(TXIGMASK)为11(即掩码0x0FFFFFFF),PrivID位域为1(即Bit31:28),那么经过转译后输出的请求地址为PrivID+0x40001234&0x0FFFFFFF=0x10001234。接收侧根据段选择寄存器解析出请求地址映射的目的地址,从而完成数据访问。整个接收端的地址转译过程如图3所示。

以图3的过程为例,从接收到的请求地址的31:28位提取出PrivID索引值1,相应表对应的值为7,从29:24位提取出地址片段表索引0x10,相应表对应的地址片段起始地址值为0x0C00,长度为23(即16 MB),通过地址的转换,最后真正访问的地址为0x0C001234。

2HyperLink应用设计与性能测试

以上是对TMS320C6678 的HyperLink通信机制及其实现过程的简单分析,但是要实现TMS320C6678 强大的多处理器功能,必须从系统的角度来设计良好的拓扑。通信代价、带宽和功能是评测通信的重要指标,下面介绍一种多处理器通信方式,分析它们的拓扑结构,并对不同映射配置做出测试对比。

2.1拓扑结构

以机载雷达某机箱内的多个处理器(6678)之间的通信为例,简要说明HyperLink如何应用在机载雷达设计中。如图4所示,某雷达机箱内有4个TMS320C6678处理器,每个处理器包含8核,并与一个RapidIO 路由器相连,整个机箱内每两个处理器之间通过HyperLink连成两组,这就形成了该机箱内的处理器拓扑结构,各处理器结合HyperLink和SRIO实现数据的高效流转。

2.2性能测试实验

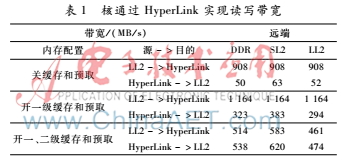

本节对HyperLink 访问远程存储空间的性能进行评估,并提供在不同的操作条件下获得的性能测试数据。大部分测试是在最理想的测试条件下进行,以使评估可以获得最大吞吐量。处理器运行的频率设置为1 GHz,DDR配置成64 bit,位宽1 333 MB,采用的编译环境是TI 公司的CCSv5.0。

通信测试结果如表1所示,描述了使用HyperLink 在LL2 与远程大块线性存储空间进行数据传送测试获得的传输带宽。传输块的大小为64 KB。带宽是通过计算总的传输字节数除以传输所用的时间获得。表1的数据展示了cache 能够极大地改善DSP 内核通过HyperLink 读取数据的性能。但是 L2 cache 却遏制了通过HyperLink 写数据的性能,这是因为L2 是writeallocate cache。对于使能L2 cache 后的写操作,它总是会先从将要写入的存储区读取128 B数据到L2 cache,然后在L2 cache 中修改数据,最后在cache 冲突时回写到原先的存储区,或者人为地回写到原存储区。

HyperLink还可以通过TMS320C6678设定EDMA事件进行传输,通信测试结果如表2所示。

表2中的EDMA 吞吐率数据是通过TC0 (传输控制器0)和CC0(通道控制器0)测试得到,其他TCs的数据会比TC0 稍低。整个传输的瓶颈是在HyperLink,不是在EDMA 传输控制器上。表2的测试结果表明,通过HyperLink 进行写操作的性能会比通过HyperLink 进行读操作的性能要好。

3结论

本文研究了基于TMS320C6678处理器的片间通信,深入分析了HyperLink模块结构、映射机制(包括寄存器配置以及具体的实现方法)和地址转译过程,文中以某种机载雷达处理机拓扑结构为例测试了HyperLink的数据传输性能。对设计多片DSP 处理器的片间通信具有一定的指导价值。

参考文献

[1] Texas Instruments Inc.Multicore design overview[Z].2011.

[2] Texas Instruments Inc.TMS320C6678 data manual[Z].2011.

[3] Texas Instruments Inc.KeyStone Architecture HyperLink User Guid[Z]. 2012.