最新版瓦森纳安排管控清单解读:光刻软件、大硅片技术管控升级,直指半导体发展命脉

2020-02-28

来源:与非网

今年一场突如其来的武汉“新冠肺炎”疫情牵动着每一个中国人的心。

可最近一周,有两个消息传来,顿时让半导体业界赶到更加揪心。

一是 2020 年 2 月 18 日,美国媒体华尔街报道,特朗普政府正考虑对中国采取新的贸易举措,将限制美国芯片制造设备的使用,寻求切断中国获得关键半导体技术的渠道。美国商务部正起草对所谓外国直接产品规定进行调整的计划,该规定限制外国企业将美国技术用于军事或国家安全产品。据知情人士称,相关调整将允许商务部要求世界各地的芯片企业在获得许可的情况下,才能使用美国设备生产供应给华为芯片。

二是 2020 年 2 月 24 日,日本媒体 Japantime 报道,包括美国、日本在内的瓦森纳安排 Wassenaar Arrangement”42 个成员国在 2019 年 12 月同意扩大出口管制范围,新增加的管制范围包括可用于军事目的的半导体基板制造技术和用于网络攻击的军事软件。报道指出,日本经济产业省和其他部门将制定有关的细节,要求硅片制造商申请出口产品和相关技术的许可证。日本相关厂商人士透露,目前还不确定日本政府的相关细节。一旦有了相关细节,则产品及相关技术的出口就必须要申请许可,厂家就会陷入疲于应付的境地。

事实上,先前华尔街的报和 Japantime 报道,都和 2019 年 12 月在奥地利召开的瓦森纳安排出口管制会议有关。

首先,我们先了解一下瓦森纳安排到底是什么条约呢?

“瓦森纳安排”的全称是“关于常规武器和两用物品及技术出口控制的瓦森纳安排 The Wassenaar Arrangement on Export Controls for Conventional Arms and Dual-Use Good and Technologies”,它是世界主要的工业设备和武器制造国在“巴黎统筹委员会”解散后成立的一个旨在控制常规武器和高新技术贸易的国际性组织。“巴黎统筹委员会”的正式名称是“对共产党国家出口管制统筹委员会 Coordinating Committee for Export to Communist Countries”,是对社会主义国家实行禁运和贸易限制的国际组,是 1949 年 11 月在美国的提议下秘密成立的,因其总部设在巴黎,通常被称为“巴黎统筹委员会”。1994 年 4 月 1 日,“巴黎统筹委员会”的正式宣告解散。然而,它所制定的禁运物品列表后来被“瓦森纳安排”所继承,延续至今。

“瓦森纳安排”于 1996 年在荷兰瓦森纳签署,当时有 33 个国家参与,包括澳大利亚、比利时、加拿大、丹麦、法国、德国、希腊、意大利、日本、卢森堡、荷兰、挪威、葡萄牙、西班牙、土耳其、英国、美国 17 个“巴黎统筹委员会”成员国和以及阿根廷、奥地利、保加利亚、捷克共和国、芬兰、匈牙利、爱尔兰、新西兰、波兰、罗马尼亚、俄罗斯、斯洛伐克、韩国、瑞典、瑞士、乌克兰等 16 国;之后墨西哥、南非、印度、克罗地亚、爱沙尼亚、拉脱维亚、立陶宛、马耳他、斯洛文尼亚等国家陆续加入。

和“巴黎统筹委员会”一样,“瓦森纳安排”包含两份控制清单:一份是军民两用商品和技术清单,涵盖了先进材料、材料处理、电子器件、计算机、电信与信息安全、传感与激光、导航与航空电子仪器、船舶与海事设备、推进系统等 9 大类;另一份是军品清单,涵盖了各类武器弹药、设备及作战平台等共 22 类。所有成员国必须签署。中国、朝鲜、伊朗、利比亚等都在被禁运之列

“瓦森纳安排”声称是一种建立在自愿基础上的集团性出口控制机制,其根本目的在于通过成员国间的信息通报制度,提高常规武器和双用途物品及技术转让的透明度,以达到对常规武器和双用途物品及相关技术转让的监督和控制。“瓦森纳安排”声称不针对任何国家和国家集团,不妨碍正常的民间贸易,也不干涉通过合法方式获得自卫武器的权力,但无论从其成员国的组成还是该机制的现实运行情况看,“瓦森纳安排”具有明显的集团性质和针对发展中国家的特点。

简单来说,就是“瓦森纳安排”虽然允许成员国在自愿的基础上对各自的技术出口实施控制,但实际上成员国在重要的技术出口决策上受到美国的影响。

好吧,有点跑题了,我们还是回到半导体领域。

对半导体产业来说,受限于《瓦森纳安排》,从芯片设计到生产等多个领域,中国都不能获取到国外的最新科技。小到一颗螺丝钉,大到航天推进器,都在管控范围内。

于是,芯思想研究院迅速找到“瓦森纳安排”的《军民两用商品和技术清单》2018 版和 2019 版进行研读。经过对照发现,刚发布的 2019 版和 2018 版相比,内容修订不多,但非常关键,直指痛点!也许会对发展中的中国半导体产业形成严重伤害。

瓦森纳安排的《军民两用商品和技术清单 Dual-Use Goods and Technologies and Munitions List》到底有那些和半导体密切相关呢?下面让我们来了解一下《军民两用商品和技术清单》。

2019 年 12 月发布的最新版瓦森纳安排的《军民两用商品和技术清单 Dual-Use Goods and Technologies and Munitions List》有共有 243 页,其中正文 241 页,比 2018 年版多了 3 页内容。

清单包括如下

通用技术、通用软件、通用信息安全说明

第一类 特殊材料和相关设备

第二类 材料加工

第三类 电子产品

第四类 计算机

第五类之一 电信

第五类之二 信息安全

第六类 传感器与激光

第七类 导航及航空电子

第八类 海洋技术

第九类 航空航天推进系统

附录一 敏感清单

附录二 非常敏感清单

其中和半导体最相关的莫过于第三类“电子产品”。当然,其他部分也多少会涉及到。

在第三类“电子产品”中,共分五项进行说明,分别是:系统、设备和组件 SYSTEMS, EQUIPMENT AND COMPONENTS;测试、检测、制造设备 TEST, INSPECTION AND PRODUCTION EQUIPMENT;材料 MATERIALS、软件 SOFTWARE、技术 TECHNOLOGY。

1、系统、设备和组件(该部分内容没有变化)

对半导体集成电路进行了诸多限制,涵盖:单片集成电路、混合集成电路、多芯片集成电路、薄膜型集成电路(包括蓝宝石上硅集成电路)、光集成电路、三维集成电路”、单片微波集成电路(MMIC)。具体来说包括:微处理器、微计算机电路、微控制器、DSP、ADC/DAC、光器件、FPGA、FFT 处理器、存储器(SRAM、NVM)、微波器件。

比如 ADC/DAC 的在符合以下条件的都在管制之内。

分辨率 8bit 到 10bit,采样率大于每秒 1.3G SPS;

分辨率 10bit 到 12bit,采样率大于每秒 600M SPS;

分辨率为 12bit 到 14bit,采样率大于 400 M SPS;

. 分辨率为 14bit 到 16bit,采样率大于 250 MSPS;

分辨率大于或等于 16 位,采样率大于 65 M SPS

2、测试、检测、制造设备(该部分内容没有修订)

包括原子层外延设备(ALE)、金属有机化学气相沉积设备(MOCVD)、分子束外延生长设备(MBE)、光刻设备(包括纳米压印)。

其中光刻设备管制范围说明如下:(和 2018 年版本没有变化)

光源波长短于 193 nm;

生产最小可分辨特征尺寸(MRF)为 45 nm 或更小的图案(MRF=曝光光源波长*0.35/NA)

如此看来 EUV 光刻机确实是在管制范围内。

但是控制和不批准是两个概念,控制归控制,但是还是有可能批准的。

确实如此,此前,中芯国际、华虹集团等半国内导体公司进口的很多设备都需要取得出口许可证,但经过双方的交流和沟通 ,设备也都购买回来了。现在我国最先进的工艺也推进到了 14 纳米,也已经实现了量产!

3、材料(该部分内容也没动)

包括衬底材料和 193 纳米用光刻胶。

半导体基板衬底说明非常明确,其范围包括硅片(Silicon Wafer)、锗片、碳化硅片以及 III-V 族的镓和铟材料,以及晶锭、晶棒等。

内容也对高电阻率材料进行了说明,并且标注了注意事项。因为高阻抗率材料可以用来生产超高压、超大电流的器件,可以转用于军事领域。

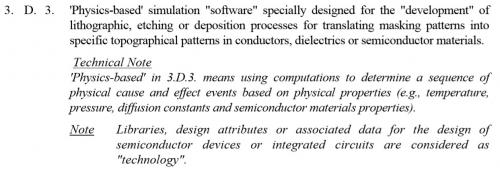

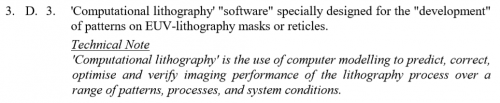

4、软件

包括为规定的设备开发的软件,以及用来开发 EUV 光刻掩模或掩模版上的图案的软件。

笔者发现 2019 版和 2018 版相对照,该部分有了变化。

修订的这部分内容非常关键。请大家仔细品读。

2018 年的内容表述为:物理模拟软件

2019 年的内容直接表述为:计算机光刻软件。

芯思想研究院认为,这一修订非常关键,直接打在半导体光刻工艺研发的七寸上。

据悉,光刻工艺过程可以用光学和化学模型借助数学公式来描述。光照射在掩模上发生衍射,衍射级被投影透镜收集并会聚在光刻胶表面,这一成像过程是一个光学过程;投影在光刻胶上的图像激发光化学反应,烘烤后导致光刻胶局部可溶于显影液,这是化学过程。计算光刻就是使用计算机来模拟、仿真光刻工艺中光学和化学过程,从理论上探索增大光刻分辨率和工艺窗口的途径,指导工艺参数的优化。计算光刻起源于 20 世纪 80 年代,它一直是作为一种辅助工具而存在。随着工艺的不断进步,设计尺寸不断缩小,器件上最小线宽开始小于曝光波长,越来越接近光刻成像系统的极限,光的衍射效应变得越来越明显,导致最终对设计图形产生光学影像退化,实际形成的光刻图案相对于掩膜版上的图案发生严重畸变,最终在硅片上经过光刻形成的实际图形和设计图形不同,这种现象称为光学邻近效应(OPE,Optical Proximity Effect)。为了修正光学邻近效应,便产生了学邻近效应修正(OPC,optical proximity correction),光学临近效应修正已经成为光刻图形处理的关键步骤,变得必不可少。

光刻工程师还使用一些专用的测试图形曝光,收集晶圆上的数据,用来修正软件里的模型,使之计算出的结果和实际尽量吻合 。

现在,在先进工艺特别是 FinFET 工艺中,计算光刻已经成为光刻工艺研发的核心。计算光刻是依靠专用 EDA 工具来实现的,这些 EDA 工具都是有专门的供应商提供的。明导(MENTOR)、新思(Synopsys)都有专用 OPC 软件提供,目前国内的全芯智造也在瞄准 OPC 软件。

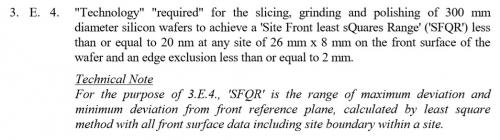

5、技术

包括浮点运算计算技术、HEMT 和 HBT 等一系列技术。

笔者发现 2019 版和 2018 版相比,在此部分最后加了一内容。就是有关 12 英寸大硅片的切磨抛(Slicing、Grinding、Polishing)工艺技术。

芯思想研究院认为,新增内容就是针对中国的大硅片企业。

新增内容中“Site front least-squares range(SFQR)”是指硅片平整度,该参数是硅片抛光质量的一个重要指标,据悉,该参数也是抛光过程中比较难于优化的一个参数。

目前,12 英寸大硅片生产技术主要由日本信越半导体(Shin-Etsu)、胜高(SUMCO)和德国世创(Siltronic)掌握,切磨抛设备也几乎被日本控制,上游的原材料高纯多晶硅也被美国、日本和德国所垄断,这也导致国内大硅片技术进展缓慢。

目前国产 8 英寸硅片出货主要还是 MOS 管器件生产用,真正用在集成电路制造中的少之又少;12 英寸主要还是以控片、陪片为主,正片还是在相对低端工艺小批量试用阶段,至于工艺节点就不要去猜测了,反正不可能是 14 纳米和 28 纳米(偷笑)。

遍地开花的大硅片项目引起了美国及其他国家的高度戒备,不知道是幸运还是悲催!但起码有一点,这些大硅片项目又可以借机炒作一把!

我国半导体集成电路产业还是发展阶段,不管是设备、材料、工艺、管理等方面,都和海外半导体有着不少的差距,脖子还是被卡着!

希望媒体不要天天写“中国半导体不再被‘卡脖子’了”、“中国告别‘缺芯’之痛”,你越吹,人家就越卡你脖子!

不要以为真得可以倒逼出半导体产业!

也许这次疫情能够让半导体产业回归理性!

如需原文可联系笔者。