台积电3nm细节公布:2.5亿晶体管/mm2 能耗性能大提升

2020-04-20

来源:新浪科技综合

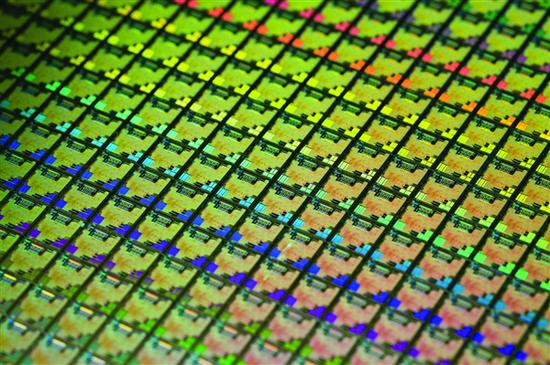

近日,台积电正式披露了其最新3nm工艺的细节详情,其晶体管密度达到了破天荒的2.5亿/mm²!

作为参考,采用台积电7nm EUV工艺的麒麟990 5G尺寸113.31mm²,晶体管密度103亿,平均下来是0.9亿/mm²,3nm工艺晶体管密度是7nm的3.6倍。这个密度形象化比喻一下,就是将奔腾4处理器缩小到针头大小。

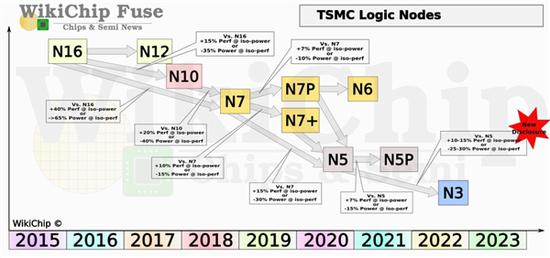

性能提升上,台积电5nm较7nm性能提升15%,能耗提升30%,而3nm较5nm性能提升7%,能耗提升15%。

此外台积电还表示,3nm工艺研发符合预期,并没有受到疫情影响,预计在2021年进入风险试产阶段,2022年下半年量产。

工艺上,台积电评估多种选择后认为现行的FinFET工艺在成本及能效上更佳,所以3nm首发依然会是FinFET晶体管技术。

但台积电老对手三星则押宝3nm节点翻身,所以进度及技术选择都很激进,将会淘汰FinFET晶体管直接使用GAA环绕栅极晶体管。

本站内容除特别声明的原创文章之外,转载内容只为传递更多信息,并不代表本网站赞同其观点。转载的所有的文章、图片、音/视频文件等资料的版权归版权所有权人所有。本站采用的非本站原创文章及图片等内容无法一一联系确认版权者。如涉及作品内容、版权和其它问题,请及时通过电子邮件或电话通知我们,以便迅速采取适当措施,避免给双方造成不必要的经济损失。联系电话:010-82306118;邮箱:aet@chinaaet.com。