FinFET的继任者:纳米片该如何制造?

2021-01-05

来源:半导体行业观察

据行业内知名媒体semiwiki报道,当前被先进工艺节点的FinFET器件的下一个继任者架将是一种被称为“纳米片”器件。

他们指出 ,与平面器件相比,FinFET的栅极横穿鳍的三个侧面,提供了改进的栅极至沟道静电控制。而纳米片器件的“GAA”特性在器件通道周围的静电控制方面则带来了进一步的改进。这就带来了更理想的亚阈值斜率或SS(subthreshold slope)。SS与器件栅极输入电压的变化有关,该变化导致泄漏电流变化10倍。较小的SS意味着更快的器件开关速度,并且显著 地减少了静态源极/漏极泄漏电流和泄漏功耗。

另外,纳米片装置提供了更大的设计灵活性。FinFET器件宽度的拓扑是量化的(Weff?((2 * fin_height)+(fin_thickness))),而纳米片器件的宽度由EUV光刻法定义(Weff?nanosheet_perimeter)。

有效的纳米片宽度可以通过垂直堆叠多个通道来进一步扩展,而栅极材料完全围绕着各个纳米片。这个设计的灵活性和改进的设备特性使该技术显得非常有吸引力。

然而,将纳米片处理引入生产存在重大挑战。以下只是其中的一部分:

1、隔离纳米片设备沟通的各个“功能区”(“ribbons”)

纳米片器件被制造在外延层中。水平器件板嵌入其他外延生长层中,例如,由不同组成的外延层(例如SiGe / Si / SiGe / Si / SiGe)夹在中间的硅层。(其中,Si和Ge之间晶体结构的紧密相似性至关重要。)

纳米片装置“带”( “ribbons” )的形成需要非常有选择性的蚀刻工艺。去除上方和下方的外延层,同时不蚀刻剩余的器件沟道。对于多个堆叠的纳米片,该蚀刻过程还需要是各向异性的,以使纳米片之间的所有牺牲外延层材料被完全去除。

2、围绕暴露的纳米片带(exposed nanosheet ribbons)的高K栅极氧化物电介质需要非常均匀,并具有出色的附着力

氧化物缺陷密度和界面陷阱密度(对于注入的“热”载流子)必须非常低。(氢气环境中的退火步骤通常包含在设备工艺流程中。)

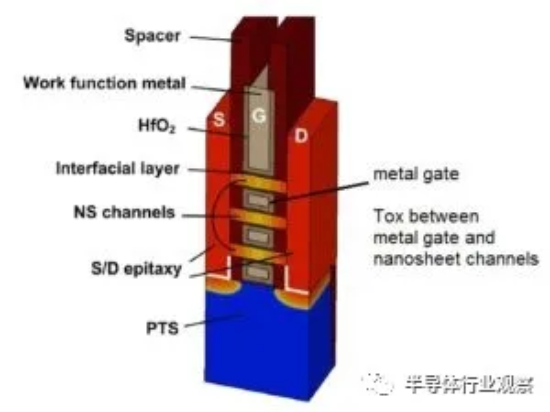

3、同样,金属栅材料堆叠需要均匀地沉积在整个结构中,以完全包围堆叠的sheets

栅极堆叠通常包括初始的金属氧化物e “workfunction”层(例如TiN),然后是填充栅极体积的金属(例如钨)。(原子层沉积(ALD)确实是一项了不起的技术。)

4、需要在沟道附近制作一个低阻源极/漏极器件节点,以减小Rs和Rd

使用外延生长步骤(具有高的掺杂剂浓度)来增加沟道附近的S / D体积,该沟道通过侧壁隔离氧化物适当地与栅极隔离。(其他FET拓扑结构也使用类似的凸起S / D外延步骤。)此外,S / D掺杂轮廓需要确保与第一级金属的接触电阻低。

5、“器件工程”需要在沟道材料中引入很大的应变,以提高自由载流子迁移率,从而改善驱动电流

从平面到FinFET器件拓扑的几代工艺中,已经采用了多种技术将应变引入沟道材料晶体中——拉伸应变可提高nMOS电子迁移率,压缩应变可提高pMOS空穴迁移率。“ Stressor”材料介电层被添加到平面设备的顶部。凸起的S / D外延区域还将应变传递到通道。

特别值得关注的是硅中电子与空穴迁移率之间的差异。

工艺开发工程师不断努力提高空穴迁移率,使其更接近电子迁移率。该领域的关键进展是在S / D外延生长步骤中添加了Ge,并最终在pFET通道中添加了Ge –即Si(x)Ge(1-x)晶体结构,提供了压缩应变和大大提高了空穴迁移率。(经验丰富的电路设计经验丰富的人会记得pFET器件宽度是nFET器件宽度的2.5倍至3倍的3年代,以补偿空穴与电子迁移率的差异。随着在SiGe pFET制备过程中引入的应变,这种差异已大大减小。)

向厚度非常小的纳米片通道的过渡加剧了提供改进的pFET器件特性的难度。

在最近的IEDM会议上,英特尔详细介绍了其纳米片工程技术如何应对这一挑战的论文。

pFET纳米片制造

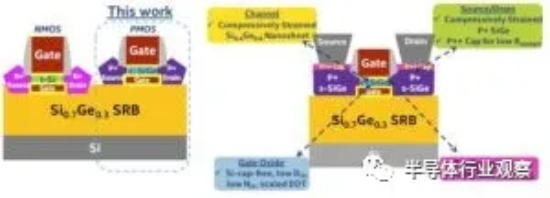

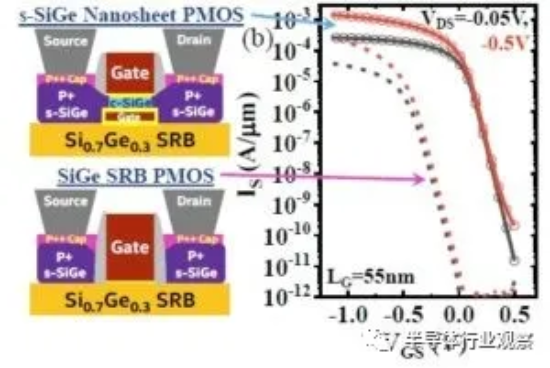

下图描绘了nFET和pFET纳米片的概述。

如上所述,沟道中的压缩应变是高性能设备的关键。这可以通过以下方式实现:

pFET沟道的外延纳米片是Si(0.4)Ge(0.6)

提高的S / D外延生长量也是SiGe

纳米片正下方的衬底由Si和Si(0.7)Ge(0.3)的“应变消除缓冲”(strain relief buffer:SRB)层组成

该缓冲层提供了从块状硅衬底的中间晶体转变,并提供了一定程度的附加沟道应变。

值得一提的是,Si和Ge的晶格常数仅相差4.2%,即Si = 0.543nm,Ge = 0.566nm。结果,Ge / Si比是完全可混溶的。

上图还说明了其他过程工程约束:

为了降低接触电阻,需要在S / D区域上添加高度掺杂的顶层

栅极氧化物需要低的缺陷和陷阱密度(具有非常高的高K材料厚度-例如,通道和随后的HfO2层的介电层)

从纳米片厚度(?5nm)到大的p + S / D节点的过渡需要详细的工艺设计,以使栅极与S / D隔离,并将压缩应变从掺杂的SiGe外延引入pMOS沟道。(有关此步骤的更多信息,请稍后。)

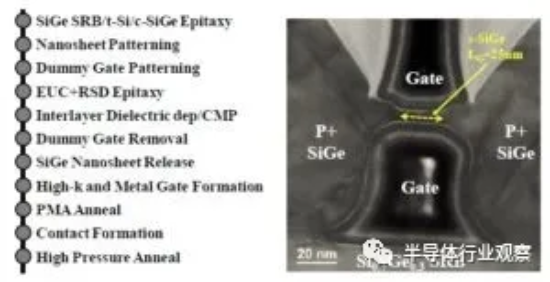

下图总结了整个英特尔pMOS纳米片制造步骤,并提供了单个纳米片器件的TEM截面-NS厚度= 5nm,Lgate = 25nm,宽度= 100nm,EOT氧化物= 9.1埃。

纳米片的制造需要几个独特的步骤,将保形材料沉积与各向同性和各向异性(定向)蚀刻技术相结合。另外,各向同性蚀刻技术需要对不同的材料组成具有很高的选择性。

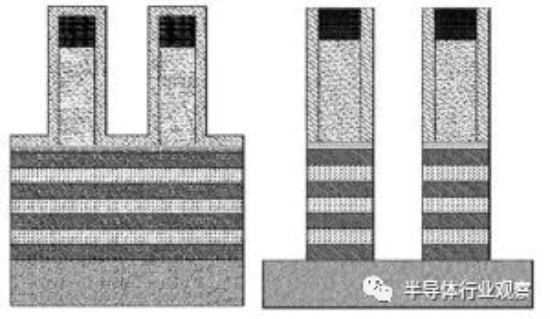

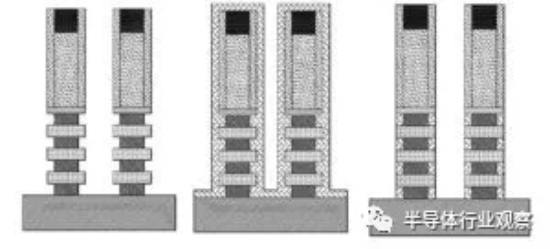

以下来自参考文献的图说明了多层堆叠纳米片的一般情况的总体流程。而英特尔IEDM讨论集中于单个pMOS纳米片器件的材料和压缩沟道应变。

起始材料是未掺杂的Si / SiGe外延层的交替层。对“虚拟”顶层栅极进行构图,然后共形沉积氧化物并(高度)各向异性蚀刻氧化物和Si / SiGe层,以形成初始纳米片堆叠。下一步很关键,如下所示。

选择性地蚀刻暴露的栅极区域的侧壁,以提供用于共形氧化物沉积的凹陷体积。对该氧化物的各向异性蚀刻导致堆叠,其中栅极区域具有横向间隔氧化物,而沟道的侧壁保持暴露,并用作源/漏外延生长的种子。

Si中的纳米片nMOS器件需要对相邻的SiGe层进行高度选择性蚀刻的处理,从而暴露出用于S / D外延生长的Si侧壁。纳米片pMOS器件需要高的硅蚀刻速率,从而暴露出用于S / D外延生长的SiGe侧壁。广泛的工艺研发(和材料化学)已应用于优化Si / SiGe“蚀刻速率比”。

在S / D外延生长之后,将虚设栅极和外延栅极层蚀刻掉(再次非常有选择地蚀刻到现在发布的纳米片沟道“ribbons”上)。在预清洁之后,将高K栅极氧化物材料沉积在ribbon上,然后沉积(功函数和低电阻)金属栅极堆叠,这两个步骤均使用原子层沉积(ALD)。向下接触底部的“沟槽”,将其打开并填充金属,以完成纳米片的制造。(在该流程中,为了蚀刻前的表面平面度,也有化学机械抛光(CMP)步骤。)

附带一提的是,还应该指出,已经进行了广泛的工艺研发,以选择特定的晶体取向,以优化应变增强的载流子迁移率,蚀刻速率选择性和S / D外延生长。

纳米片和寄生晶体管

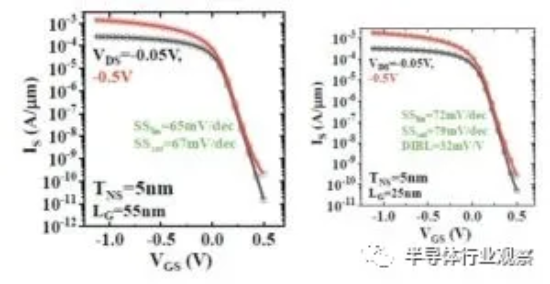

回到其优化的压应变pMOS纳米片的英特尔演示文稿中,不同设备的IDS-VGS曲线如下所示(Lgate = 55nm和25nm)。

从全方位栅极配置的优异静电中可以预期到,为这些器件测量的亚阈值斜率非常出色。(英特尔没有描述其建立pFET器件阈值电压的工程方法。)

特别令人感兴趣的是S / D到基板接口的设计。纳米片结构导致围绕底部纳米片的金属栅极与衬底之间的寄生晶体管。与纳米片的S / D接触还用作底部寄生晶体管的S / D连接。为了评估这种寄生器件电流的大小,英特尔制造并测量了仅由该寄生晶体管组成的测试工具-实验结果如下所示。

该设备的泄漏电流远小于纳米片的泄漏电流,表明该“sneak” 电流得到了适当的抑制。(为进一步减小这种寄生电流,可以在S / D触点下方引入穿通停止掺杂剂区域。)

VDD优化

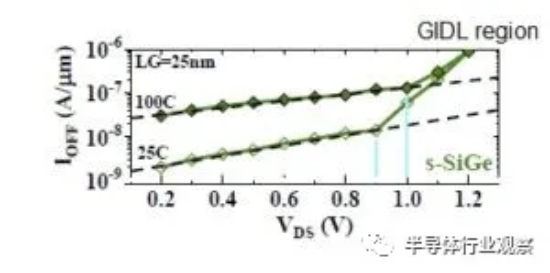

对于高性能应用,设计人员正在寻求将电源电压提高到技术最高水平。这些限制是由于较高电压下Ioff泄漏的增加所致。沟道中较高的漏极至源极电场会导致漏极引起的势垒降低(drain-induced barrier lowering:DIBL)电流,而非常高的漏极至栅极场会导致栅极引起的漏极泄漏隧道电流(gate-induced-drain-leakage tunnel current:GIDL)。下图表明,在GIDL电流呈指数增长之前(应变SiGe,Lgate = 25nm,t_NS = 5nm),VDD = 0.9V对于该技术是可行的。