一文看懂高速发展的2.5D/3D封装

2021-03-18

来源:半导体行业观察

据DIGITIMES Research分析,伴随着CPU、GPU、FPGA等高效能运算(HPC)芯片性能要求持续提升,覆晶封装(Flip Chip;FC)、层叠封装(Package on Package;PoP)等传统封装技术已不敷使用,使2.5D/3D封装技术需求逐渐增加,吸引半导体制造业者积极布局,其中,IDM与晶圆代工业者2.5D技术发展相对委外半导体封测(OSAT)业者成熟、完整,也具有多年量产经验,3D封装技术则将陆续开花结果。

DIGITIMES Research分析师陈泽嘉指出,覆晶封装虽是现行芯片封装主流技术,然2.5D/3D封装提供较覆晶封装7~8倍以上的I/O数增量,以及更高密度整合更多芯片/模组,有助芯片提升效能、改善功耗等,增加HPC芯片业者采用2.5D/3D技术的诱因。具体来看,NVIDIA与超微(AMD) CPU与GPU、英特尔(Intel)与赛灵思(Xilinx) FPGA等多为2.5D封装,而英特尔Lakefield CPU更是首个以3D封装的CPU。

陈泽嘉进一步指出,HPC芯片所催生的2.5D/3D封装商机吸引IC制造业者积极布局,其中,英特尔、三星电子与台积电已具成熟的2.5D封装经验;3D封装部分,英特尔已量产Foveros技术,三星与台积电则将在2021~2022年陆续量产。日月光、艾克尔(Amkor)等OSAT业者虽布局2.5D/3D封装,但技术方案仍不若IDM与晶圆代工业者完整,然逐渐强化中。

2.5D和3D封装技术有何异同?

除了先进制程之外,先进封装也成为延续摩尔定律的关键技术,像是2.5D、3D等技术在近年来成为半导体产业的热门议题。究竟,先进封装是如何在延续摩尔定律上扮演关键角色?而2.5D、3D等封装技术又有何特点?

人工智能(AI)、车联网、5G 等应用相继兴起,且皆须使用到高速运算、高速传输、低延迟、低耗能的先进功能芯片;然而,随着运算需求呈倍数成长,究竟要如何延续摩尔定律,成为半导体产业的一大挑战。

芯片微缩愈加困难,异构整合由此而生

换言之,半导体先进制程纷纷迈入了7 纳米、5 纳米,接着开始朝3 纳米和2 纳米迈进,电晶体大小也因此不断接近原子的物理体积限制,电子及物理的限制也让先进制程的持续微缩与升级难度越来越高。

也因此,半导体产业除了持续发展先进制程之外,也「山不转路转」地开始找寻其他既能让芯片维持小体积,同时又保有高效能的方式;而芯片的布局设计,遂成为延续摩尔定律的新解方,异构整合(Heterogeneous Integration Design Architecture System,HIDAS)概念便应运而生,同时成为IC 芯片的创新动能。

▲异构整合成为实现小体积、高效能芯片的另一种方式。(Source:SEMI)

所谓的异构整合,广义而言,就是将两种不同的芯片,例如记忆体+逻辑芯片、光电+电子元件等,透过封装、3D 堆叠等技术整合在一起。换句话说,将两种不同制程、不同性质的芯片整合在一起,都可称为是异构整合。

因为应用市场更加的多元,每项产品的成本、性能和目标族群都不同,因此所需的异构整合技术也不尽相同,市场分众化趋势逐渐浮现。为此,IC 代工、制造及半导体设备业者纷纷投入异构整合发展,2.5D、3D 封装、Chiplets 等现今热门的封装技术,便是基于异构整合的想法,如雨后春笋般浮现。

2.5D 封装有效降低芯片生产成本

过往要将芯片整合在一起,大多使用系统单封装(System in a Package,SiP)技术,像是PiP(Package in Package)封装、PoP(Package on Package)封装等。然而,随着智能手机、AIoT 等应用,不仅需要更高的性能,还要保持小体积、低功耗,在这样的情况下,必须想办法将更多的芯片堆积起来使体积再缩小,因此,目前封装技术除了原有的SiP 之外,也纷纷朝向立体封装技术发展。

立体封装概略来说,意即直接使用矽晶圆制作的「矽中介板」(Silicon interposer),而不使用以往塑胶制作的「导线载板」,将数个功能不同的芯片,直接封装成一个具更高效能的芯片。换言之,就是朝着芯片叠高的方式,在矽上面不断叠加矽芯片,改善制程成本及物理限制,让摩尔定律得以继续实现。

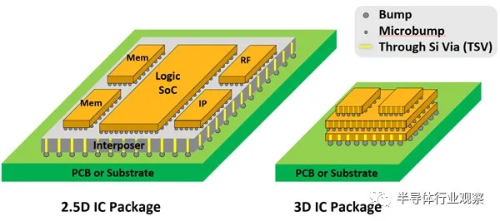

而立体封装较为人熟知的是2.5D 与3D 封装,这边先从2.5D 封装谈起。所谓的2.5D 封装,主要的概念是将处理器、记忆体或是其他的芯片,并列排在矽中介板(Silicon Interposer)上,先经由微凸块(Micro Bump)连结,让矽中介板之内金属线可连接不同芯片的电子讯号;接着再透过矽穿孔(TSV)来连结下方的金属凸块(Solder Bump),再经由导线载板连结外部金属球,实现芯片、芯片与封装基板之间更紧密的互连。

▲ 2.5D和3D封装是热门的立体封装技术。(Source:ANSYS)

目前为人所熟知的2.5D 封装技术,不外乎是台积电的CoWoS。CoWoS 技术概念,简单来说是先将半导体芯片(像是处理器、记忆体等),一同放在矽中介层上,再透过Chip on Wafer(CoW)的封装制程连接至底层基板上。换言之,也就是先将芯片通过Chip on Wafer(CoW)的封装制程连接至矽晶圆,再把CoW 芯片与基板连接,整合成CoWoS;利用这种封装模式,使得多颗芯片可以封装到一起,透过Si Interposer 互联,达到了封装体积小,功耗低,引脚少的效果。

▲台积电CoWos封装技术概念。(Source:台积电)

除了CoWos 外,扇出型晶圆级封装也可归为2.5D 封装的一种方式。扇出型晶圆级封装技术的原理,是从半导体裸晶的端点上,拉出需要的电路至重分布层(Redistribution Layer),进而形成封装。因此不需封装载板,不用打线(Wire)、凸块(Bump),能够降低30% 的生产成本,也让芯片更薄。同时也让芯片面积减少许多,也可取代成本较高的直通矽晶穿孔,达到透过封装技术整合不同元件功能的目标。

当然,立体封装技术不只有2.5D,还有3D 封装。那么,两者之间的差别究竟为何,而3D 封装又有半导体业者正在采用?

相较于2.5D 封装,3D 封装的原理是在芯片制作电晶体(CMOS)结构,并且直接使用矽穿孔来连结上下不同芯片的电子讯号,以直接将记忆体或其他芯片垂直堆叠在上面。此项封装最大的技术挑战便是,要在芯片内直接制作矽穿孔困难度极高,不过,由于高效能运算、人工智能等应用兴起,加上TSV 技术愈来愈成熟,可以看到越来越多的CPU、GPU 和记忆体开始采用3D 封装。

▲ 3D封装是直接将芯片堆叠起来。(Source:英特尔)

台积电、英特尔积极发展3D 封装技术

在3D 封装上,英特尔(Intel)和台积电都有各自的技术。英特尔采用的是「Foveros」的3D 封装技术,使用异构堆叠逻辑处理运算,可以把各个逻辑芯片堆栈一起。也就是说,首度把芯片堆叠从传统的被动矽中介层与堆叠记忆体,扩展到高效能逻辑产品,如CPU、绘图与AI 处理器等。以往堆叠仅用于记忆体,现在采用异构堆叠于堆叠以往仅用于记忆体,现在采用异构堆叠,让记忆体及运算芯片能以不同组合堆叠。

另外,英特尔还研发3 项全新技术,分别为Co-EMIB、ODI 和MDIO。Co-EMIB 能连接更高的运算性能和能力,并能够让两个或多个Foveros 元件互连,设计人员还能够以非常高的频宽和非常低的功耗连接模拟器、记忆体和其他模组。ODI 技术则为封装中小芯片之间的全方位互连通讯提供了更大的灵活性。顶部芯片可以像EMIB 技术一样与其他小芯片进行通讯,同时还可以像Foveros 技术一样,通过矽通孔(TSV)与下面的底部裸片进行垂直通讯。

同时,该技术还利用大的垂直通孔直接从封装基板向顶部裸片供电,这种大通孔比传统的矽通孔大得多,其电阻更低,因而可提供更稳定的电力传输;并透过堆叠实现更高频宽和更低延迟。此一方法减少基底芯片中所需的矽通孔数量,为主动元件释放了更多的面积,优化裸片尺寸。

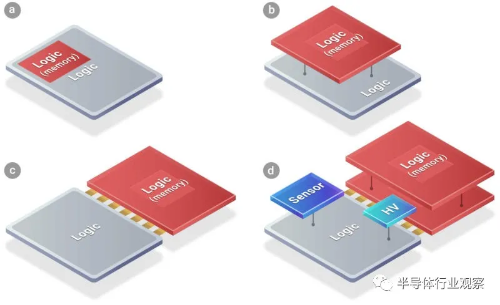

而台积电,则是提出「3D 多芯片与系统整合芯片」(SoIC)的整合方案。此项系统整合芯片解决方案将不同尺寸、制程技术,以及材料的已知良好裸晶直接堆叠在一起。

台积电提到,相较于传统使用微凸块的3D 积体电路解决方案,此一系统整合芯片的凸块密度与速度高出数倍,同时大幅减少功耗。此外,系统整合芯片是前段制程整合解决方案,在封装之前连结两个或更多的裸晶;因此,系统整合芯片组能够利用该公司的InFO 或CoWoS 的后端先进封装技术来进一步整合其他芯片,打造一个强大的「3D×3D」系统级解决方案。

▲台积电SoIC整合方案。(Source:台积电)

此外,台积电亦推出3DFabric,将快速成长的3DIC 系统整合解决方案统合起来,提供更好的灵活性,透过稳固的芯片互连打造出强大的系统。藉由不同的选项进行前段芯片堆叠与后段封装,3DFabric 协助客户将多个逻辑芯片连结在一起,甚至串联高频宽记忆体(HBM)或异构小芯片,例如类比、输入/输出,以及射频模组。3DFabric 能够结合后段3D 与前段3D 技术的解决方案,并能与电晶体微缩互补,持续提升系统效能与功能性,缩小尺寸外观,并且加快产品上市时程。