存算一体芯片,这几年可能就要覆盖从端到云

2021-09-17

来源: 电子工程专辑

有关存算一体、存内计算的概念,此前我们撰文探讨过。尤其在AI发展的时代背景下,存储墙问题越来越成为算力持续提升的瓶颈,所以业界就提出了非冯(non-von Neumann)架构,将传统、以计算为中心的冯诺依曼架构,变换计算范式,将部分算力下推到存储,也就有了存内计算的说法。

这个概念有不同的实施方案,通常这种存算一体结构,可理解为在存储器中嵌入算法,存储单元本身就有计算能力,从理论上消除数据存取的延迟和功耗。这种芯片格外适用于神经网络。

昨天的第二届中国(上海)自贸区临港新片区半导体产业发展高峰论坛的“芯”品路演活动中,北京知存科技有限公司CEO王绍迪谈到了自家的WTM2101:存算一体芯片;以及未来今年内知存的战略规划。

解决存储墙问题

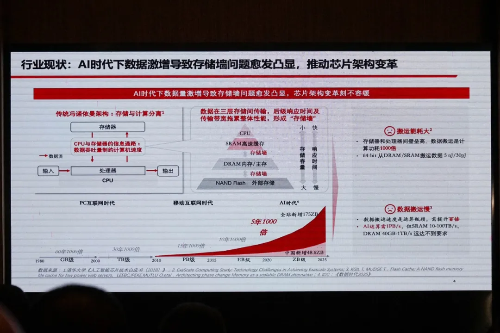

王绍迪给出的下面这张图中,提及了存储墙问题存在的一些典型数据;主要反映的是,随着工艺技术的进步,处理器计算能力越来越强、运算速度越来越快,存储容量越来越大,但存储器带宽却难以获得同比增长。

随算力增加,处理器核心数增多,每核心可用带宽越来越少,也就限制了整体速度。“搬运数据,成为相当大的瓶颈。”“与此同时能耗也成问题。”从外部存储器,和片内存储搬运数据的能耗差别巨大;而且“数据搬运时间是运算时间的几百倍、上千倍。”

“这也是为什么要做存算一体方案。解决存储墙最根本的方案,就是把存储和计算融合到一起,用存储单元去做计算。”王绍迪说。

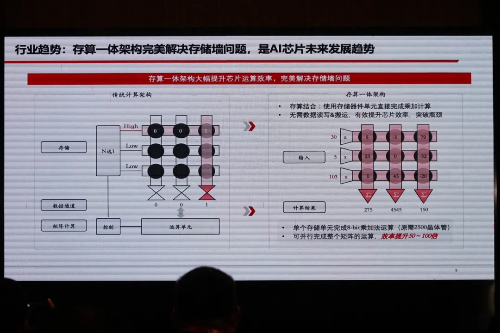

“存内计算这个名字可能更好,就是用存储器去做计算,整体还是计算类型的芯片。其计算介质是存储器,不是逻辑运算单元。”上面这张图对比了两者的结构区别,其中的圆圈代表存储单元。

和传统计算架构存储子系统每次激活一行,并依次完成数据读取不同;存算一体架构同时激活多行多列。“横轴不再是选择信号,实际上是被处理数据。”过程中需转换为模拟电路——此前我们也提过利用单一器件的欧姆定律完成一次乘法,然后利用基尔霍夫定律完成列累加。以此使用存储器件单元完成乘加计算。

“一个存储器运算周期可以完成100万次参数乘法和加法运算,效率提升50-100倍。”显然这对AI而言就相当有价值了。

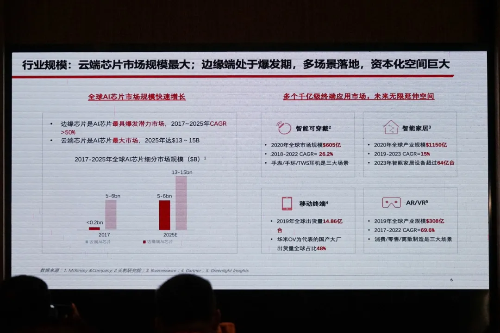

在更具体的使用场景方面,面向从端侧到云的AI计算,做算力弹性扩展在存算一体的芯片产品上似乎也具备了天然的优势。“2MB、4MB、8MB存储器算力相对更低,可以给端侧设备去用;存算一体阵列到128MB,就可以给边缘侧了;存储容量达到1GB、2GB、4GB,可提供超过1000TOPS的算力,使用云端场景。”

“存算一体会花5-8年的时间去覆盖AI运算场景,就从端侧和边缘侧开始。”王绍迪说。上面这张图也明确给出了不同场景的AI芯片,未来的市场规模及其发展潜力——这些应当也是众所周知的了。

从知存1.0到知存3.0

从知存这家公司的发展轨迹来看,两名创始人比较早就有参与美国存算一体项目研发的经验;2017年成立知存科技,并于次年拿到天使轮融资。这还是相当年轻的一家企业。2019年,知存“与国际知名公司开展存算一体IP研发合作,并完成IP和SoC测试芯片的流片,发布国际上首个存算一体芯片”。

2020年,知存完成“国际首个存算一体芯片量产投片”,以及“国际首个存算一体SoC芯片验证”。这次王绍迪介绍的WTM2101存算一体芯片预计于今年第四季度量产。看起来“存算一体”这个概念的发展速度远比我们预想中的快。

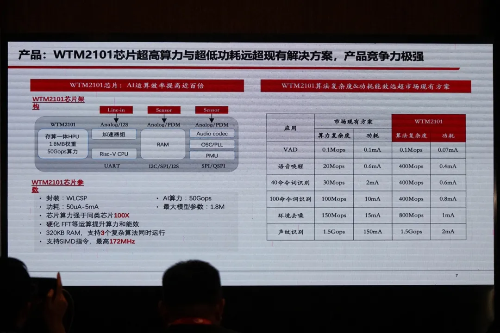

上面这张图左侧为WTM2101芯片架构图,有存算一体的存储器主体部分“大部分运算都通过存算一体完成”;另外也配了RISC-V CPU,提供非矩阵类运算。

“对比现有市场方案的算力、功耗,WTM2101都有10倍以上的优势。”虽然并不清楚这张图中“市场现有方案”究竟是什么方案,但WTM2101这一栏所标的算法复杂度与功耗,的确都相当令人惊叹。

除了介绍产品以外,王绍迪还谈到了知存的战略规划。从公司成立到2020年是“知存1.0时代”,这一阶段“研发存算一体技术,并应用于语音场景”,王绍迪也再次强调了“我们是国际上首个技术落地的公司”。

从今年到2024年属于知存2.0规划期,“进一步推进,推进到128MB,实现64-100TOPS算力级别,覆盖端侧、边缘侧场景。我们会选择优势场景去落地应用。”

而在2024年以后,芯片“推向云端”,以1GB容量做到500-2000TOPS算力区间,且产品实现车规级的可靠性。“2025年之后,计划推出标准化产品。之后产品不再以应用场景落地为导向,而是像存储器那样提供不同的容量,和现有计算系统做整合,以先进封装技术完成这样的整合。”“同时我们也推出对应的工具链,完全适配存算一体技术,去适配主流的人工智能算法。”

注意这张图横轴的营收与纵轴市值预期,都表明这家公司在未来短期内的发展信心就相当充足。或许这张图本身也能代表存算一体技术未来几年内的发展趋势。