影响了芯片可靠性设计的六大因素

2021-12-31

来源:探索科技TechSugar

现阶段,越来越多的芯片应用于安全或关键任务领域,对于芯片缺陷率和良率的要求越来越高。另一方面,对于企业来说,更低缺陷率和更高良率也是降低设计和制造成本的一种方式。

而在初始设计中解决这些问题已经成为降低芯片缺陷率、提高良率的新方向。过去,芯片缺陷和良率问题总是被归结于晶圆厂。为了确保芯片设计能够成功流片点亮,企业实施了限制性设计规则 (RDR)。但RDR对于芯片设计生产来讲,仍然存在一些挑战:

RDR增加了太多设计裕量,尤其是在先进工艺节点上。这会对性能、功耗和面积产生负面影响。

为特定应用定制的芯片越来越多,频繁使用某种类型的先进封装、不同种类的处理器和存储器,以及过去未批量生产的独特架构。

在某些应用中,芯片的预期寿命更长,这意味着在智能手机中原本不是问题的潜在缺陷现在可能需要花更大代价召回。因此,设计团队开始在设计中加入传感器,以确定芯片从开启到预期寿命结束的使用状态。

如今,设备及产品对芯片都有着不同的要求。例如,与为物联网消费设备生产的芯片相比,用于汽车传动系统的芯片具有完全不同的应力和预期。设计团队需要了解这些芯片随着时间的推移会如何表现,从环境和使用条件到老化、电热、应力和变化效应等综合考量。

“可靠性是当今电路设计和仿真中需要解决的最重要议题之一,”西门子EDA ICVS AMS验证产品工程总监Ahmed Ramadan Hassan表示。“我们现在拥有的产品在2年、5年或10年后可能不再起作用。例如以特定频率运行的处理器,由于电路中的每个设备都施加了应力,其频率可能会在5年或更长时间后下降。对于更大的设计,这种偏压或温度方面的应力会降低特定设备的整体性能。因此,芯片可能无法执行预期的功能,或者会降低其预期的功能。”

设计人员现在必须在电路设计和验证中考虑可靠性问题,有效地将有关缺陷、良率和可制造性问题从设计到制造流程中一直左右转移。

“过去,由于缺乏良好的可靠性分析和仿真技术以及可靠性模型,设计人员会过度设计,并留有很多裕量。他们在设计中添加了大量防护带,来确保该产品至少在保修期内不会出现故障。”

这种转变意义重大,但需要从更高层面来看,才能真正了解其包罗万象。“多年来,我们始终努力制造更好、更快、更新的芯片,”Vtool前数字设计经理Aleksandar Mijatovic表示。“当技术处于临界点时,我们也面临着一系列问题。有时技术突破边界却与预期背道而驰。这意味着如果尝试使用最大频率来实现芯片上的最大密度,则很可能在给定技术的可能性边缘工作,有时可能会破坏芯片功能。但另一方面,这不是工程师的错。我们都知道这一点,但市场要求更好、更新、更快。”

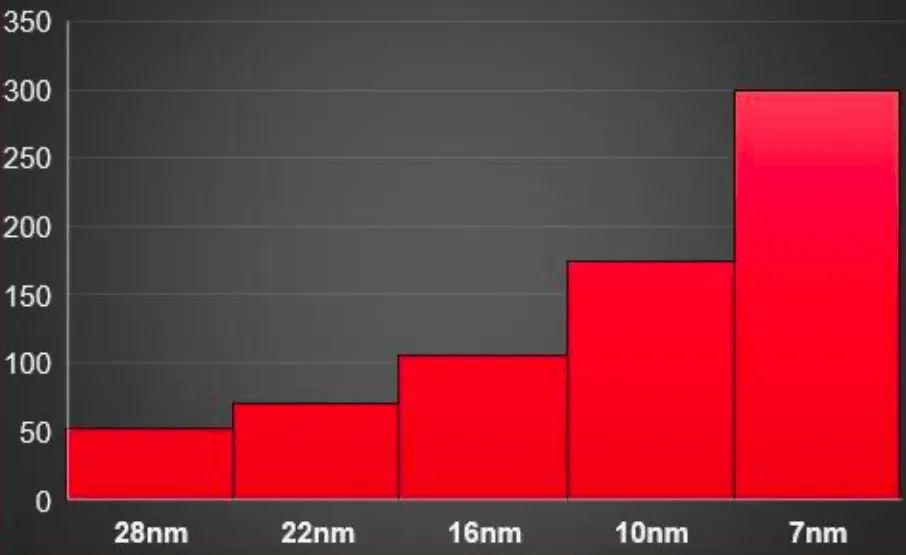

经济负担也在向左转移。虽然这种动态在某种程度上一直存在,但随着芯片制造商努力控制成本,这种趋势已成为行业关注的焦点。

图1:每个工艺节点的SoC成本以百万美元成倍上升。

图源:Cadence

“当前,一些公司表示,‘我们没有必要使用最新工艺制程,而是需要可靠的工艺节点。我们不想太频繁地更换芯片。’这并不是什么新鲜事,只是关注重点正在转移,” Mijatovic表示。“有许多公司正在使用非常过时的技术制造芯片。因为成熟工艺已经足够好,且经过验证,并且没有太多惊喜,整个汽车芯片制造工作都是用成熟技术完成的。在追逐全新的更先进的技术和工艺过程中,我们忘记了很多时候并不需要最新的制程节点。”

对于汽车、医疗、工业和数据中心应用,这些考虑变得更加复杂。在这些应用中,芯片成本急剧上升、对更长寿命的需求、令人生畏的更换成本以及出现问题时的潜在责任掀起了一场风暴。

“当我们开始谈论在汽车应用中使用电子产品时,更重要的是要确保此类故障不会发生。确保全面考虑了这些问题,确保汽车电子在更长时间或很短时间内都不会出现问题,” Hassan表示。“此外,这意味着在设计方面需要更严谨的安全防护。”

与此同时,随着从汽车、机器人、无人机等应用场景的自主性越来越高,可靠性已成为重中之重。

安全问题

与可靠性密切相关的是安全性,尤其是在汽车、医疗、工业和军用/航空应用方面。

Vtool项目经理Olivera Stojanovic 回忆称,在一次与安全相关的会议上,最终得出的结论是,若黑客可以在车辆行驶过程中控制汽车驾驶,那么security(面对恶意操作的安全)可能比safety(面对非恶意操作的安全)更重要。

Mijatovic指出,当很少有设备连接到互联网时,这并非什么大问题。“这不仅是我们的个人电脑和手机,还有冰箱、微波炉和暖气。我们把所有设备都连接入网。”

越来越多的设备联网将增加设备的复杂性,这反过来又需要更多的验证和更好的兼容性。

“从设计验证的角度来看,可以将提出的每个附加要求都视为规范中的附加层,”Mijatovic表示。“规范并不意味着设备必须执行规范中的功能,而是需要保证设备更可靠、准确和安全地运行。所有这些都可以定义为功能,最终也将作为功能实现。可使用不易出错或不易被黑客入侵的架构,并进行安全检查。最后,这也适用于协议,以及从一开始就考虑到的安全性或可靠性概念。”

持续监测

这些可靠性问题不仅限于汽车领域。“我们已经开始看到,对于其他应用,可靠性设计和可靠性验证也变得越来越重要,”Hassan表示。“我们已经看到许多EDA供应商与Compact Model Coalition等组织合作,从电路设计所需的仿真和建模角度解决这种可靠性问题。”

Compact Model Coalition开发了一个用于老化和仿真的标准接口,称为开放模型接口,为代工厂或任何设计公司的各个团队创建了一种方法来集成老化模型以处理机械退化等影响、热载流子注入(HCI)等机制或该接口内的负偏置温度不稳定性 (NBTI)。它还能够使用EDA工具运行仿真,并在5或10年后或在该产品的预期使用寿命内捕获芯片运行状态。

“这项工作旨在是通过运行这种分析,设计人员将不需要过度设计,因为已经有了这种老化仿真,” Hassan表示。“现在他们可以看到并预测其设计在一定年限后的状态,并且可以将其设计推向极限以获得性能——但不会留有裕量。当他们开始使用时,实际上可以在其电路和设计中添加一些补偿技术。”

使用的一些技术包括创建片上监控器和传感器,以检测操作期间设备性能的任何下降。通过这种感应,可以应用补偿来适应参数退化,从而避免设计的整体性能退化。

额外的监控器可能会增加设备和后续产品的面积,并消耗额外的功率或影响性能。但在某些情况下,拥有此类监控器和补偿技术可以确保在不造成伤害或服务中断的情况下采取纠正措施。

老化和应力

虽然老化和各种类型的应力(机械、电气、热)是不可避免的,但能够预测这些影响会对设备执行规范的时间产生重大影响。预测影响的关键要素之一是了解芯片的使用环境。

“对于分析的探索源于汽车等传统领域,例如如何对应力环境进行建模,如何让设计工程师有信心确保部件在未来15年内都能正常工作。”Cadence数字与签核小组高级产品管理总监Brandon Bautz表示。“汽车应用要求设备能够运行10年,但只消耗这么多电力,否则我的电动汽车不会走那么远。部件的可靠性和性能之间需要平衡。如何获得更准确的分析,以便可以更清楚地了解芯片性能与可靠性?从数字角度进行的老化分析已经有一段时间了,但分析结果相对悲观。但考虑到10年前,甚至5年前拥有的工具,这种分析方法确实是需要的。”

然而,鉴于汽车行业对硅的依赖程度如此之高,出于成本原因,许多较新的领域也在寻求高可靠性。“您可以使芯片非常可靠,但它可能无法按照需要的方式运行。” Bautz表示。“由于芯片本身的复杂性,成本、性能、面积和风险的权衡变得越来越激烈。因此,需要进行的分析类型更加复杂。保护带和确保可靠是好的,但根据我们所做的一些研究,以及我们在表征和分析算法中所做的改进,已经展示了客户使用这些较旧的方法所拥有的利润率。通过更准确的分析,设计团队将能够平衡可靠性和性能。”

这为更多的全面分析打开了大门,反过来又会对可靠性产生重大影响。

“从了解过去二十年的工作方式开始,我们认识到10年前有限的计算能力无法真正捕捉到问题的真正本质。在这种情况下,我们指的是老化,以及影响老化的应力依赖性,”Bautz称。“通过在数字分析中将两个部分放在一起,表征过程可以在单元级别捕获设备性能。然后查看设计级别,并在设计的上下文中观察特定的元件和设备性能。将特征与时序分析相结合,为设计人员提供准确度,更具体地说,让设计人员深入了解他们的电路在整体设计环境中的工作方式。那么将电路置于设计环境中,便可以分析设备的实际应力。因此,我们可以更准确地分析老化对设备的影响,并了解它如何影响设备的整体寿命。”

模拟可靠性问题

这仅适用于数字设计,模拟设计面临着更多的自身挑战。

如今,几乎所有的芯片都包含模拟电路。“即使在拥有数百万个门级的系统中,仍然存在一定数量的模拟电路,而且这个数量还在增加。”Cadence定制IC和PCB集团产品管理总监Jay Madiraju表示。“模拟设计团队关心的不仅仅是功能,他们设计的模拟组件和模块将与庞大的数字逻辑电路相连接。他们想预先知道设计是否可靠。”

可靠性在模拟方面具有多重含义。“当您查看经典浴缸曲线时,您认为什么时候产品才算是可靠的?可靠性的概念实际上意味着什么?这需要看模拟器件随着时间的推移是否能够运作良好,”Madiraju表示。“这绝对是模拟人关心的问题。那么,随着时间的推移,电路如何发挥作用?从多年经验来看,设备故障将会变得越来越多,越来越不易于使用。但哪些地方损坏了?就载流子迁移率、阈值电压和其他器件特性而言,这是整个电路按其应有的方式运行的基础。它是如何随着时间的推移而退化的,如何在退化之前预测?”

虽然老化技术的仿真已经发展了几十年,但其任务配置文件在过去几年中才得到了改进。

“在任务配置文件之前,工程团队仿真了最坏的情况,”他介绍。“‘这将是最糟糕的情况。该芯片将用于汽车领域。我们将假设这辆车将永远在120°的天气里。如何仿真这种极端情况?’你必须通过假设这些极端恶劣情况来保障设备可靠性,但其意外后果是过度设计、过度裕量和保护带。设计人员的设计理念相当保守,全面考虑性能会受到的影响——性能来自不同方面,比如速度、时序和功率泄漏,以及芯片应该如何表现的所有不同方面。任务配置文件有助于解决这个问题,因此可以定义不同的条件,包括温度、电压和其他随时间变化的条件。你可以说有时候这些芯片有不同的应力模式,或者在这种操作下,比如在进行校准过程时,它会承受多大的应力。应力会导致退化。不同模式下也不尽相同。”

另一方面是制造可靠性,在模拟领域中,有几个因素将会影响可靠性。“一个是时间的退化。另一个是在制造过程中发生的未通过测试的缺陷,例如芯片已经完工且在将其发布给原始设备制造商之前已经完成了初始测试。例如,在汽车领域,一些芯片通过了这些测试并交付给客户,汽车OEM会面临这些问题。可靠性问题将是业界重点关注的问题。”他解释。

这就是模拟故障仿真的用武之地。它类似于数字端的DFT,在芯片流片之前的验证过程注入故障。“我们可以看到哪些故障没有影响,哪些故障会影响输出,哪些不会影响输出,然后可以尝试进行覆盖测量。我们正在通过各种测试来验证设计。当注入故障时,预期看到的是错误的输出。最终,所有这一切的目标是看看在使用测试集来运行电路时,是否捕捉到了需要的一切现象,以便当芯片退化时客户不会发现错误?” Madiraju说。

电热效应是模拟领域中另一个日益重要影响因素,而自热模型中缺少的是热量对相邻或附近设备的影响。这需要电热模拟仿真。

“以前,工程团队只会进行热模拟,测量传播效果,然后他们会根据对功率的影响返回相应信息至模拟电路,这是电气仿真、电路仿真和热之间单向流动的一部分。”他说。“现在,这对于先进芯片和高压设备来说显然是不够的,当然还有汽车领域的那些芯片,以及承受高压条件的工业芯片。亟需一种综合方法,使这种反馈效应在单个仿真中建模。”

可靠性和内存

内存对可靠性的影响越来越大,因为内存选择会影响从功率到面积的所有性能参数。这在 DRAM中尤为明显,随着时间推移,选择高带宽内存或GDDR会对内存在其他组件环境中的状态产生重大影响。

“与DDR、GDDR或LPDDR相比,HBM设备的功耗将更低,需要处理的物理接口更少。”Synopsys内存接口IP产品营销经理Brett Murdock表示。“如何在SoC上物理实现它们是不受控制的。你想做什么,就可以做什么。你可以将一个完整的线性PHY放在芯片的一侧,可以环绕在角落,也可以将它折叠起来。有无数种方法可以实现该物理接口。但是使用 HBM,则需要放置HBM立方体,而JEDEC已经准确定义了该立方体上的凸点地图是什么样子。这意味着虽然就放置凸点的位置而言,灵活性可能较低,但它能够带来更好的可预测性和可靠性。中介层以及如何将其连接在一起有多种不同的选择,但归根结底,如果选择GDDR、LPDDR、DDR,则可以构建数百万种不同的电路板,以数百万种不同的方式将其连接起来,导致数百万种不同的实现方式,以及数百万种不同的错误结果。而对于HBM,放入PHY,放入设备,并且如何在这两者之间放置中介层没有太多可变性。SoC和HBM设备之间会有最小间距规则。”

在可能的情况下,重复过去有效的方法可以大大确保它在新设计中有效。“重复有助于提高可靠性,” Murdock认为。“我们为每个客户做同样的事情,或几乎同样的事情,这一事实意味着我们越来越有经验。这是经过验证的方案。”

偏差

偏差是另一个影响可靠性的因素,因此了解其对先进节点和先进封装的影响尤为重要。造成偏差的原因有很多,从材料中的污染物和CMP的剩余颗粒,到封装过程中的芯片移位和光刻技术的不一致性。芯片在什么时候会产生缺陷,以及如何在设计阶段解决这些问题仍然是一个挑战。

“设计团队意识到需要对设计中的偏差采取解决措施,”西门子EDA AMS验证产品PLM 软件负责人Sathishkumar Balasubramanian表示。“人们围绕这个谈论不同的概念,包括稳健性和可靠性。归根结底,这些都指向同一目标,即客户希望设备能够在投入最终产品的任何地方工作,且能够在给定的合理时间表内工作更长时间。”

Balasubramanian表示,偏差非常重要,以至于业界开始将偏差作为高sigma要求包含在内,从库组件的设计流程早期开始,将其作为流程的一部分。“他们旨在确保组件坚固耐用。例如,在标准库中,对于给定的标准单元库和特定工艺,它满足所有不同的 PVT,范围更广,并且仍然满足3到7 sigma要求。”

总结

将所有这些部分放在设计到制造流程的最左侧是一项复杂的工作。实际上,过去可以在制造中修复的问题已经越来越难以完成。如今,必须在更左侧考虑潜在问题,这意味着设计团队现在正在努力解决通常为工艺工程师保留的概念,而工艺工程师正在将数据反馈给EDA供应商,从而对工具进行调整,或增加新功能。

当前,可靠性仍是一个普遍性挑战,从最初设计到现场产品监控,整个供应链都需要为保障芯片可靠性尽职尽责。