泰瑞达:后摩尔时代的集成电路芯片复杂测试挑战

2022-01-25

来源:泰瑞达

泰瑞达中国区销售副总经理黄飞鸿

编者按:后摩尔时代集成电路芯片的晶体管数量急剧增加,另一方面功能的集成度同样不断提高,都对于集成电路芯片测试解决方案提出了新的挑战,测试效率和测试功能都必须满足新的测试需求。日前,泰瑞达中国区销售副总经理黄飞鸿借着新测试设备的解决方案发布的机会,详细地阐述了集成电路芯片测试的现状与趋势。

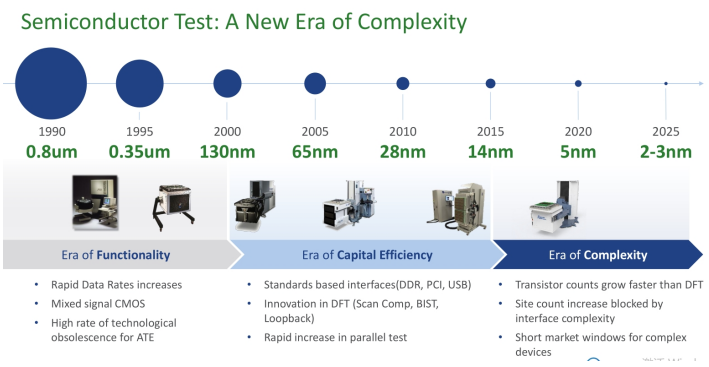

ATE测试技术发展的三个时代

集成电路芯片工艺演进大概可以分成三个时代,而ATE测试解决方案同样随之演进了若干阶段。

在1990年代的时候是0.35微米和0.13微米制程,在这之前是CMOS工艺蓬勃发展的时代,实际上是半导体SOC芯片功能越来越强,在芯片上面会集成模拟的功能,包括数据接口的传输率也在增加。在这一时代,对于之前ATE(Automatic Test Equipment)的测试技术带来极大的挑战。原先旧的测试平台实际上不能够覆盖这种新带来的模拟和高速接口测试的需求,表现为对于ATE测试机要满足日趋复杂的SOC芯片的需求,可以称之为比拼测试机的“功能时代”。

到了2000-2015年,集成电路工艺开始进入90纳米、65纳米、28纳米和14纳米时代。这个时代工艺越来越先进,芯片尺寸也越来越小,它带来了芯片上面晶体管集成度越来越高。芯片规模日趋变大之后带来的挑战是测试时间非常长,测试成本在整个芯片成本之中的比例变得很高。

伴随芯片设计工艺演进,芯片对于ATE测试提出了更为广泛的要求,包括标准化接口,DFT设计能力也在不断地加强,只有这样才能够覆盖到日趋复杂的芯片测试需求,ATE测试设备需要具备包括BIST测试和标准化接口测试以及越来越深的扫描测试的能力。

如果说功能时代基本上测试都是单工位测试,那么进入这个时代单工位测试对芯片成本带来非常大的压力,所以对测试机提出了“同测”的要求,即要求测试机板卡集成的通道数要越来越多,能够同时进行2工位,4工位,8工位测试,在此这个时代也可以称之为“资本效率时代”。

第三个时代开启于2020年后,即集成电路工艺进入5纳米和2-3纳米,而此时情况似乎开始轮回了。

这个时代晶体管上面数量的增长,增长速度超过了本身可测试设计的技术。另外,从测试机台设备角度来看,机台多工位测试不可能无限次增加。同时芯片的生命周期越来越短,原来消费类芯片生命周期2年或者3年,现在1年就迭代,甚至对于AI芯片和AP高复杂度芯片来说也是逐年迭代,这些因素都是复杂性的因素,对于测试机要求带来了不同领域,不同要求的复杂性的调整,所以这个时代可以称之为“复杂性时代”。

“复杂性时代”带来新挑战

先进工艺演进会带来哪些测试挑战呢?

首先,先进工艺芯片增加了测试时间,而ATE测试设备的效率需要提速。

先进工艺演进使得芯片里面晶体管数量逐渐的增加,测试要求对每个晶体管都要覆盖,因此会极大增加整个芯片的测试时间。

对于以处理器芯片为代表的数字芯片来说,测试时间主要花费在Scan和BIST测试。工艺尺寸越来越小,势必带来测试时间的增加。和2015年相比,同样测试条件下的测试时间增加了近2.5倍,接下来可能会达到3倍的测试时间。

对于模拟和射频芯片来说,除了芯片内部的模拟测试外,Trim测试花费的时间比重越来越大,就是在测试之前内部需要先做trim调整,调整完之后,每颗芯片再进行测试,同样会带来额外的测试时间。

其次,先进工艺条件下,采用先进工艺生产芯片,仅仅是测试时间增加意味着测试成本的增加,同时保证良率(yield)是对于测试技术提出的另一个挑战。

当工艺尺寸不断缩减,初次yield对于晶圆来说是不断下降的,但是随着芯片程度越来越复杂,每颗芯片Die尺寸是不断增加的,实际上它对于里面可能带来失效的概率也在增加,所以两个因素如果迭加起来看,对800平方毫米的die size wafer来说,可以看到初次良率跌到不足10%。

虽然消费类集成电路产品所能允许的失效率较高,但是到了2020年出现了新的趋势,即越来越多的消费和手持移动的芯片开始应用到汽车电子领域。一旦应用场景到了汽车场景之后,对于失效率的要求就会呈指数型增长。现在对芯片失效率要求掉10个DPM以下,甚至有些场景要求1个DPM。

在这两个截然相反的趋势下,这就要求针对集成电路芯片的ATE测试一定要测的准,才能保证产品良率的提高。

新机台UltraFLEXplus应对测试挑战

为了满足后摩尔时代大规模集成电路芯片的测试新需求,泰瑞达不断通过创新技术手段推出系列测试新品设备,UltraFLEXplus就是一款最新型的集成电路芯片的ATE测试平台。

UltraFLEXplus是UltraFLEX家族的新成员,它完全基于UltraFLEX和IG-XL平台方案的优势并结合了用户新的功能需求。

黄飞鸿表示,UltraFLEXplus是对原来UltraFLEX系列很好的补充,并且具备独特优势和特点。

一是结构更紧凑,采用全水冷系统。

UltraFLEXplus可谓使人眼前一亮,外观特别干净,特别紧凑,跟上一代UltraFLEX相比,感觉一下子漂亮好多,精致很多,集成度做的非常好,是全水冷系统。

芯片测试接口板采用Broadside技术设计,可以使这块接口板的应用区域更大,同时可以使接口板PCB层数做的更少。

二是全新的数字测试板卡。

测试板卡是一块插在测试头里面,上面有一根一根针顶到芯片测试接口板,这个芯片测试接口板是根据每个芯片同测数需求专门设计的。

全新的数字测试板卡除了高密度特点外,还采用新的技术,包括开放式架构,可升级的架构,后面提到分布式控制CPU的架构。本身来说测试效率提高,同时配合IG-XL软件可以使工程开发时间从原来100%变成80%,也就是说在更快的时间内,更短的时间内,能够开发出更优化的测试程序。

三是独有的PACE架构。

PACE架构在这一代UltraFLEXplus平台上面所独有采用的。在原来UltraFLEX控制结构总线结构上面是通过中间的工作站主控电脑来控制每块板卡的测量测试、计算、数据结果的传送。对于新的架构来说,依然有一台主控电脑,但是我把真正的板卡控制全部都下放到每块板卡上面,因为每块板卡上面都有自己独立的CPU,在这上面可以完成所有的指令的运行。最终只要通过RESULTS BUS传回主控电脑就可以了,这样带来的好处就是测试效率的提升。

截至目前, UltraFLEXplus全球装机量已经接近600台,获得了主要客户的欢迎。