入门:工具使MCU+FPGA编程变得轻而易举

2022-08-26

来源:上海秉恒

自从商业上可行的 FPGA 出现以来,嵌入式设计人员就已经实现了异构架构。最初,FPGA 主要用作处理系统、外设和 I/O 之间接口的粘合逻辑。但随着 FPGA 技术的改进,市场扩大到在嵌入式系统中发挥更大和更核心的作用。异构计算的最新趋势是将处理器和 FPGA 子系统集成到单个 SoC 中。以处理器和软件为中心的设计团队现在可以在这些复杂的 SoC 上利用这两个系统。

异构计算架构

系统设计人员被嵌入式系统的处理器和 FPGA 组合所吸引,因为它们在标准设计模板中提供了灵活性和性能。系统中的处理器提供了广泛的标准外设接口,如以太网、串口、USB、CAN、SPI和内存。在仅处理器方法中,应用程序 I/O 通常通过 SPI 或 USB 连接。为处理器开发软件已广为人知且易于管理。

在处理器和专用 I/O 之间放置 FPGA 可提高系统的灵活性和处理能力,并增加硬件驱动操作的可靠性和确定性。FPGA 不受操作系统或其他软件开销的影响,这会降低性能并降低可靠性。由于 FPGA 是可重新配置的门阵列逻辑电路矩阵,其硬件可以重新编程以执行无数功能,包括信号处理、自定义定时和触发,以及极其先进的确定性控制。可重新编程有助于硬件升级和产品差异化,从而在不断发展的接口和标准中延长产品寿命。

除了这些优势之外,处理器加 FPGA 的组合还带来了一些挑战:

FPGA 的功耗

将单独的 FPGA 集成到 PCB 设计中的尺寸、成本和复杂性

与处理器上的软件开发相比,与 FPGA 硬件设计相关的编程。

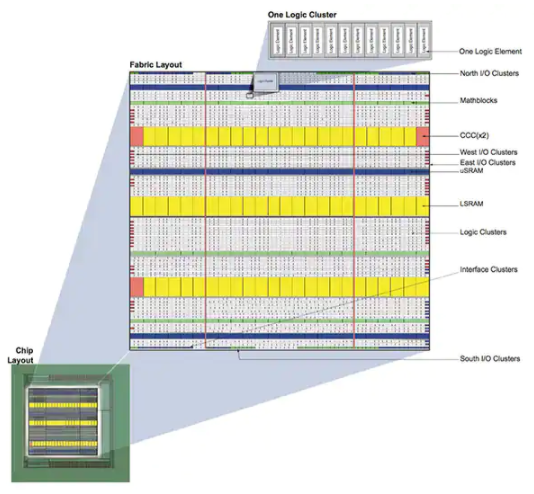

FPGA 供应商正在通过 SoC 解决其中的许多挑战,SoC 集成了处理器和 FPGA,并确保两者之间的连接。Xilinx Zynq All Programmable SoC 是一个将 ARM Cortex-A9 CPU 与 FPGA 逻辑集成的示例。Cypress Semiconductor PSoC(可编程 SoC)和 Microsemi SmartFusion cSoC(可定制 SoC)将 ARM Cortex-M3 CPU 与可编程逻辑和可编程模拟接口集成在一起。这些产品降低了集成 FPGA 的尺寸、成本和功耗。

图 1:SoC 相对于 DSP 或 ASIC 的优势——基于每芯片的 MAC、每 W 的 MAC 和每美元的 MAC。

软件编程和硬件描述语言

将 FPGA 子系统集成到处理器 SoC 通常会使 PCB 设计更加容易。然而,对这两个系统进行编程仍然很困难。通常,硬件描述语言 (HDL),如 VHDL 或 Verilog,是利用 FPGA 所必需的。精通 C/C++ 等语言的系统设计人员库非常丰富,而 HDL 专家只占嵌入式系统工程师劳动力的一小部分。

可编程逻辑工具已经发展到更好地适应嵌入式软件工程师的技能。具有 FPGA 架构的 FPGA 和 SoC 可供领域和 VHDL 专家在工业应用中使用。FPGA 供应商正在大力投资工具和合作伙伴,以更好地协调处理器和 FPGA 架构之间的开发实践。高级综合 (HLS) 工具,例如 LabVIEW FPGA 模块、Vivado HLS 或 SystemC,可缩小软件和数字域之间的代码开发差距。

一个示例工具是 LabVIEW,它自 2003 年以来就具有一个插件模块,该模块针对用于 NaTIonal Instruments 基于 FPGA 的硬件中的 Xilinx FPGA。该工具将处理器和 FPGA 逻辑的开发抽象为相同的语言和控制循环,这可以比以前使用基于处理器的系统更快地创建。单个系统设计人员可以掌握软件和 FPGA 开发领域,这通常需要两名或多名具有独特技能的工程师。他们可以利用内置语言结构来管理时钟/时序、内存 I/O 和数据传输(例如,直接内存访问),以及周期精确的仿真和调试功能、云编译支持以提高生产力,以及支持 HDL 集成。一个算法,写一次,

通过提高集成度来缩短上市时间

使用传统方法,将 I/O 集成到 FPGA 中通常很耗时。许多高级综合工具无法替代整个 HDL 工具链,因为从 FPGA 架构到现实世界的 I/O 接口仍然必须使用 HDL 实现。来自 HDL 设计团队的轶事表明,I/O 集成通常需要 70% 以上的时间专门用于设计,而只有 30% 或更少的时间用于通过控制算法或信号处理来增加差异化价值。

LabVIEW 软件和基于 FPGA 的硬件的紧密集成带来了解放——团队可以提升集成水平,不再为完全定制设计的细节所累。他们可以花更多的时间专注于增加自己的价值和差异化,而不是花在构建操作系统、开发中间件驱动程序或调试 PCB 设计信号完整性问题上。

更多信息可以来这里获取==>>电子技术应用-AET<<