2030单颗芯片容纳1万亿晶体管,中国科学家设计1nm晶体管惊艳全世界

2023-01-12

来源:雷锋网leiphone

1947年12月,人类第一代半导体放大器件在贝尔实验室诞生,其发明者肖克利及其研究小组成员将这一器件命名为晶体管。

今年是晶体管诞生的第75年,其发展已经陷入了瓶颈,我们是否还能找到新方法延续摩尔定律?

2022年,我们依然需要新的晶体管

为了纪念晶体管被发明75周年,IEEE(电气与电子工程师协会)电子器件分会(E lectron Device Society )组织了一场活动,在此活动上有Fin-FET的发明者胡正明教授对晶体管的过去进行回顾。

我们的世界是否还需要更好的晶体管?

胡正明在演讲中给出了肯定的回答,并给出了三个理由:

第一,随着晶体管的改进,人类掌握了从未想象到的新能力,例如计算和高速通信、互联网、智能手机、内存和存储、计算机技术、人工智能,可以想象的是,未来还会有其他新技术涌现出来;

第二,晶体管广泛的应用正在改变所有技术、工业和科学,同时半导体技术的演进不想其他技术一样受到其材料和能源使用的限制,IC使用相对较少的材料就可以生产,并且正在变得越来越小,使用的材料也越来越少,IC本身也在变得更快更高效;

第三,理论而言,信息处理所需的能量依然可以减少到今天所需能量的千分之一以下,虽然我们可能还不知道如何达到这种理论效率,但我们知道这在理论上可行,而其他大部分技术的能源效率已经达到理论极限。

2030年,单颗芯片可容纳1万亿个晶体管

需要新的晶体管是事实,但研发制造出新的晶体管已经举步维艰,无论是在经济上还是在技术上,都遇到了新的困难。

近期,Fin-FET的进步能够带来的性能提升和功耗降低变得越来越有限,业界正在采用一种新的3D CMOS结构的环栅(GAA)制造新的晶体管。

英特尔为了进一步缩小晶体管的三维尺寸,用RibbonFET的结构实现了GAA,但是发现源极和漏极之间的距离进一步缩小的同时,会产生比较明显的短沟道效应而漏电。

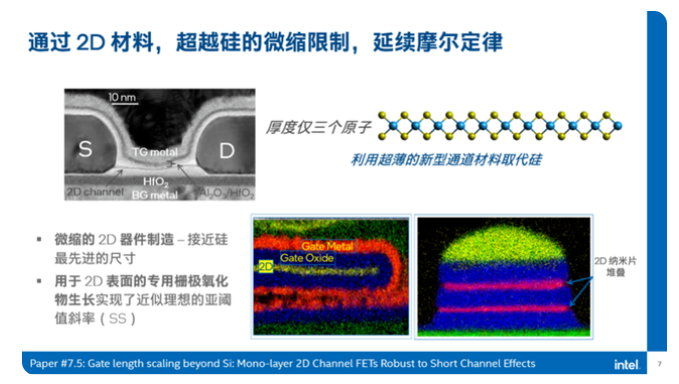

如果将传统的通道材料硅材料换成非硅的新材料,就能改善这种情况。学术界也有了一些相关的研究,使用一种名为过渡金属硫化物的材料作为通道材料,这种材料只有三个原子的厚度,电子流动性好,作为通道材料有天然优势。

在这种2D材料方面,针对这种材料,英特尔也做了很多研究和分析,并在会议上展示了一种全环绕栅极堆叠式纳米片结构,使用了厚度仅三个原子的2D通道材料,同时在室温下实现了近似理想的低漏电流双栅极结构晶体管开关。

除此之外,3D封装技术也能进一步提升单个设备中晶体管的数目。

英特尔在3D封装方面也取得了新进展,与IEDM 2021上公布的成果相比,英特尔IEDM 2022上展示的最新混合键合研究将功率密度和性能又提升了10倍。

另外,通过混合键合技术将互连间距继续微缩到3微米,英特尔实现了与单片式系统级芯片(system-on-chip)连接相似的互连密度和带宽。加上将多芯片互连的工艺里需要的材料换成无机材料,以便于与封装厂多种工艺要求兼容。

虽然进一步实现晶体管的微缩是一件需要耗费巨大财力和人力的事情,但依然有像英特尔这样的企业在持续投入研发,并对晶体管的未来抱有期望。

英特尔认为,从2023年到2030年,单个设备中晶体管的数目将翻10倍,即从1千亿个晶体管到1万亿个晶体管。

要实现这个目标,需要整个行业持续投入研发,尝试更多可行的技术。

中国科学家设计1nm晶体管惊艳全世界

在不久之前,我们曾披露,复旦大学微电子学院的周鹏教授,包文中研究员及信息科学与工程学院的万景研究员,创新地提出了硅基二维异质集成叠层晶体管技术。

该技术利用成熟的后端工艺将新型二维材料集成在硅基芯片上,并利用两者高度匹配的物理特性,成功实现 4 英寸大规模三维异质集成互补场效应晶体管。

该技术成果的文章发表在 nature electronics,并受到大家广泛关注,以下为引言部分——

大规模集成电路的特征尺寸缩小依赖于新型材料、器件架构和工艺流程的持续创新,大数据和即时数据的传输逐渐成为信息技术发展的主要趋势。目前已经提出了诸如鳍型场效应晶体管(FinFET)、全栅(GAA)以及垂直堆叠的叉片和CFET器件等巧妙的器件架构,缩小晶体管的尺寸可增加集成密度并提高性能。其中,CFET架构(PMOS和NMOS器件垂直堆叠并由同一公共栅极控制)已被证明可以减少42-50%的面积,性能提高7%,与传统的互补金属氧化物半导体(CMOS)器件相比,成本降低了12%10。因此,它提供了将摩尔定律进一步扩展到1nm节点以下的巨大应用前景。

最近,Intel公司报道的3D堆叠GAA n/p-Si纳米带CMOS展示了最先进的Si工艺技术,其显示出高集成密度和优异的短沟道控制能力。这种3D/3D堆叠CFET架构是硅器件中的一个了不起的突破。然而,硅基的CFET面临许多制造挑战,例如复杂的工艺流程、对热预算的额外要求、源极和漏极外延生长的困难以及电子/空穴迁移率失配和阈值电压(VTH)调谐的补偿。为了通过双金属栅极调整阈值电压,不可避免地需要额外的光刻、蚀刻和沉积工艺,这使得工艺相当复杂。在电子器件中使用二维半导体的研究已经开始从单一器件的工作过渡到IC的开发。然而,在将二维系统引入IC行业之前,仍有许多挑战需要解决,包括晶圆级制造、性能匹配、,将2D半导体并入硅互补金属氧化物半导体基IC是一种替代方法,可用于弥合新兴材料与工业应用之间的差距。然而,这需要与传统硅技术兼容的2D材料的器件架构和集成方法。

在本文中,我们提出了一种异质CFET架构,它结合了晶圆级绝缘体上硅(SOI)pFET和二硫化钼(MoS2)nFET。SOI技术自然能够抑制短沟道效应(SCE),降低寄生电容,并具有优异的亚阈值特性和与现代硅工艺的完全兼容性,全耗尽SOI(FD-SOI)技术已经用于先进的VLSI电路,低至22 nm和14 nm技术节点。另一方面,2D半导体在超大规模CMOS、光电子和传感器中显示出良好的潜力由于其原子厚度、丰富的带结构和高的表面与体积比。MoS2中的电子迁移率与硅中的空穴迁移率相似,可以使用化学气相沉积(CVD)在晶片规模上合成高质量的MoS2,并在低温下转移。我们通过迁移率匹配(具体地,通过选择MoS2层的厚度)缓解nFET/pFET中电子和空穴之间的迁移率失配问题,堆叠的n/p金属栅极,并引入额外的控制栅极。我们使用该方法创建了一个SOI–MoS2 CFET反相器,在电源电压(VDD)为3V时电压增益高达142.3,在100 mV的低VDD时电压增益为1.2,功耗为64 pW。我们还通过开发SOI–MoS2 CFETs的4英寸制造工艺来验证该方法的制造潜力。

如果对具体内容感兴趣,可前往全文阅读。

更多信息可以来这里获取==>>电子技术应用-AET<<