芯片制程背后的秘密:三星、台积电的3nm,实际是22nm?

2023-02-05

来源:互联网乱侃秀

2022年末,台积电实现了3nm工艺,而在半年之前,三星实现了3nm工艺。

那么问题就来了,3nm工艺究竟代表的是芯片的哪一部分是3nm?估计没有谁能够说清楚,而事实上也是如此,因为与3nm芯片的所有关键指标中,没有一项是3nm。

我们知道芯片是由晶体管组成,晶体管越多,芯片性能越强,因为一个晶体管就是一路电流,代表一个0与1的开关换算。

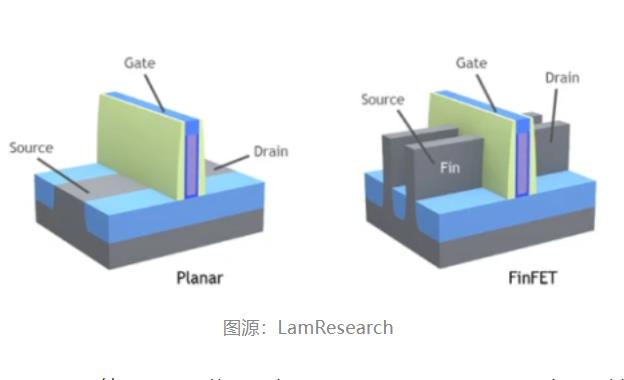

而一个晶体管里面又含有三个部分,分别是源极(Source,电流入口)、漏极(Drain-电流的出口)、栅极(Gate-开关)。

电流从源极流向漏极,中间要经过栅极,栅极相当于一道门,所以栅极的开关门速度,就代表了这个晶体管的性能,开关门的速度越快,计算就越快,晶体管性能就越强。

而开关门的速度,与栅极的长短有关,栅极越短,电流经过的距离越短,自然速度就越快,这样晶体管的性能也就越强。

所以关键来了,在50年前的时候,芯片界就有了共识,用栅极的宽度,来代表工艺制程的大小,比如150nm工艺,代表的是栅极的宽度是150nm。

后来晶圆厂们就想,既然栅极代表的就是工艺制程,那就是极力的去缩小栅极的宽度,就达到了提升工艺的目标了。

所以有一段时间,栅极的发展突飞猛进,大家纷纷用更好的材料,更高的技术来优先缩小栅极的宽度,栅极的发展比摩尔定律的发展更快。

一个有意思的事情:在晶圆厂们130nm工艺的时候,其实栅极宽度约为70nm,那时候栅极的发展,实际快于晶体管技术、整体工艺的的发展。

但遵循摩尔定律,大家没有直接用栅极的宽度来命名工艺制程,还是按照摩尔定律来命名工艺,从这里开始栅极与工艺开始脱钩,栅极工艺命名法第一次暂时失效。

但后来大家也发现,栅极越短,会带来很多的问题,比如漏电导致功耗上升,还会导致性能不稳定,开关门不受控等等后果,最后影响芯片的整体性能。

所以后来栅极的发展就又慢了下来,最后与工艺制程,摩尔定律基本一致,栅极与工艺又一一对应了。

再后来,栅极的发展,又慢于工艺制程、摩尔定律的发展了,哪怕英特尔推出了FinFET晶体管,将晶体管做成立体的,栅极也落后于摩尔定律了,因为栅极无法持续缩短。

这里栅极与工艺制程又开始脱钩了,不过晶圆厂们,再次用摩尔定律的发展,来命名工艺制程了。栅极工艺命名法第二次暂时失效。

台积电研发负责人、技术研究副总经理黄汉森所说的:“现在描述工艺水平的XX纳米说法已经不科学了……制程节点已经变成了一种营销游戏,与科技本身的特性没什么关系了。”

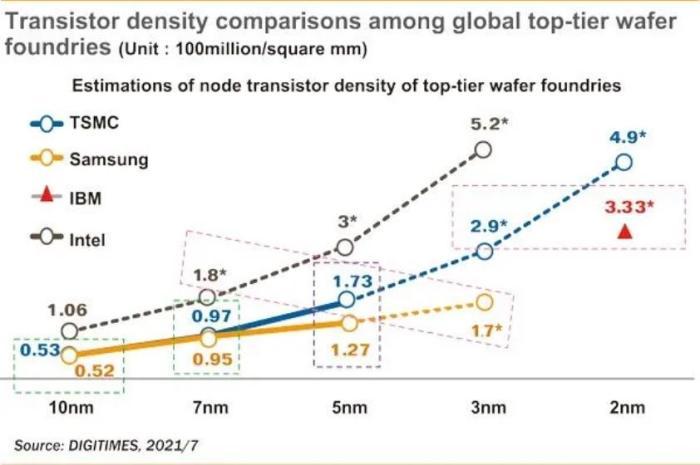

这里其实指就是这个意思:现在的多少纳米,代表的并不是栅极的宽度,而是各晶圆厂,按照摩尔定律推算出来的工艺,每次工艺更新是上一代的0.7倍,至于真正是什么工艺,只有晶圆自己知道,也就有了各大晶圆厂,同一工艺,晶体管密度完全不同的情况出现。

最近有媒体报道称,如果真要按照栅级的宽度来命名纳米工艺,那么台积电、三星的3nm工艺,其栅级实际宽度可能在22nm左右,但现在没人用栅级宽度来命名工艺了。

事实上,我们知道英特尔曾经想严谨的命名的,想保留一下最后的倔强,所以intel的14nm打磨了5年,因为它发现自己工艺的提升,无法与晶体管、栅极对应,所以就不改变工艺节点。

这样就也有了intel的14nm能媲美台积电、三星的10nm,intel的7nm,能媲美台积电的5nm,三星的3nm的事实。

但后来英特尔发现,严谨并没有用,反而给消费者留下一个坏印象,那就是自己的工艺落后了,于是intel改名,改为intel7、intel4、intel3等,正式向台积电、三星们看齐,大家一起来玩这场营销游戏。

下一次栅极与工艺制程什么时候会重合?谁也不清楚,也许再也回不来了,因为这种营销游戏深受市场、客户的喜欢,一用开始了就会让人上瘾,再也戒不掉了。

更多信息可以来这里获取==>>电子技术应用-AET<<